采用双采样技术的高性能采样保持电路

2007-12-03 10:44:11 作者:吴剑龙 于映 来源:现代电子技术关键字: 增益 极点 差分 运放

1 引 言

随着技术的发展,高速度高精度已成为流水线A/D转换器的设计目标,而采样/保持电路作为流水线结构A/D转换器的核心部分,他的性能决定了整个A/D转换器的性能。因此,设计一个高速高精度的采样保持电路就显得尤为重要。采样保持电路的精度要求一般受限于运放的有限增益和开关电路引起的误差。一方面,运放并非理想运放,他存在着增益误差;另一方面由于采样保持电路是一种开关电容电路的运用,他本身存在的开关电荷注入效应[1]和时钟溃通,以及开关导通电阻的非线性[2],都会影响采样保持电路的精度。对于电荷注入效应和时钟溃通,一般可以采用底极板采样技术[3],利用开关的导通时序,使电荷注入与输入信号无关,再通过全差分结构来消除。本文采用栅压自举电路,在减小电荷注入效应和时钟溃通的同时消除了开关导通电阻的非线性,减小了信号失真,提高了电路精度。而对于采样保持电路的速度,一般都要求设计具有高速的运算放大器,但是当运放的设计达到一定瓶颈时,就需对采样保持电路做进一步的改进。本文采用了双采样的电路结构,即在同一个时钟周期内进行两次采样保持的建立,从而使采样频率在同等性能运算放大器的条件成倍增加,减小了对运算放大器的要求。

2 双采样的采样保持电路结构

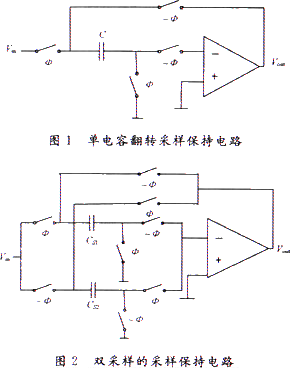

CMOS采样保持电路通常有电荷转换结构和电容翻转结构。电荷转换结构电路包含两个电容,一个为采样电容Cs,一个为保持电容Cf。在采样相时钟下,采样电容上的电压跟随输入信号变化,在采样相结束,即采样时刻到来时,采样到的信号以电荷形式储存于采样电容Cs两端;在保持相下,Cs储存的电荷转移到Cf上,令Cf与Cs相等,则稳定时候运放输出电压即采集到电压;另一种结构即如图1所示的电容翻转采样保持结构,在采样时刻,电容C采集输入信号量,在保持时刻电容C与输出相接,输出电压为采样时刻电压,从而实现采样保持。

这两种结构比较,电荷转换结构有较大的共模输入范围,但是在功耗与噪声方面,在同样采样频率下,电容翻转结构的功耗是电荷转换结构的一半,且电荷转换结构的噪声是电容翻转结构采样保持的2倍。因此这里选择了电容翻转结构。

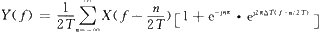

但是,这种采样保持结构在采样周期时,保持电路空闲,在保持周期时,采样电路空闲,一个时钟周期内电路只能对信号进行一次采集。若在此基础上增加一个采样电容,如图2所示,两个采样电容交替工作。在电容Cs1采样周期,输出端保持电容Cs2的采样信号;同样,在输出端保持电容Cs1的采样信号时,电容Cs2进行采样。两个电容轮流工作,使在一个时钟周期内,电路实现两次采样保持的建立过程。因此,在同样性能的运放条件下,采样频率提高到了原来的2倍[4]。

两相时钟进行采样时,由于采样间隔不均匀,采样将会有一个间隔误差,设采样间隔误差为△T,则两个采样相的序列分别为:

总输出频谱为:

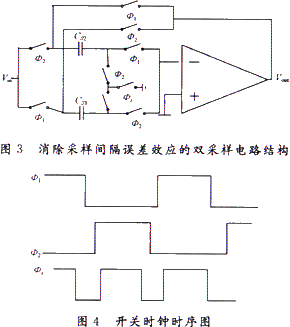

由于采样间隔误差的存在,使采样信号将在n×Fs/2处产生多余的频谱分量。为了消除采样间隔误差产生的这种效应,引入了φs相,整体结构和时钟时序如图3,图4所示。电路每一次的采样都是在φs相的下降沿进行,例如在φ1与φs都为高电平时,采样电容Cs1跟随输入信号变化,在φs下降沿到达时,Cs1对此刻输入信号进行采集。随后φ1变为低电平,φ2变为高电平,运放输出保持Cs1采集到的电平,等φs再次由高电平下降到低电平时Cs2对输入信号进行采集,由此交替进行。由于都是在同一相时钟φs下降沿进行采样,因此消除了采样间隔误差,也就消除了由此引起的效应。

3 栅压自举开关

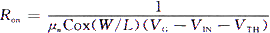

对于精度一般电路而言,NMOS管可以表现出较好的开关特性。但是在精度要求较高情况下,由于存在电荷注入效应和时钟溃通效应,开关会带来一定的误差,他的输入范围也因开关阈值电压的存在而减小,并且在非理想情况下,导通的NMOS管具有与输入电压有关的非线性导通电阻。其阻值为:

可以看出导通电阻受输入电压影响,并为非线性。若将栅压VG固定为VDD+VIN,栅源电压VGS为VDD,是与输入信号无关的固定量,他的导通电阻将为一个固定值,与输入电压无关,这样就可以消除导通电阻的非线性且同时减小导通电阻,从而可以提高采样速度,减小开关传输失真。同时,因为开关管注入到采样电容的电荷量Q=WLCox(VGS-VTH),当VGS固定,开关注入的电荷量也为一个常数,不受输入电压影响,再通过差分结构即可减小电荷注入效应的影响。

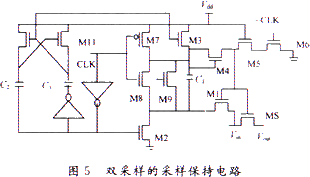

采用图5所示的栅压自举开关电路[5]即可实现上述对NMOS开关的优化。栅压自举开关电路包括两部份,图5中左半部分为采样时钟提高电路,他为M3提供了一个高电平为2VDD,低电平为VDD的栅压,使M3导通时电容C1可以充电到VDD;右半部分是自举开关电路,采样开关MS在单个时钟CLK的控制下实现开关。当CLK为低电平时,M5,M6导通,MS栅压接地,开关管截止,M3,M2导通,电容C1充电到VDD;CLK为高电平时,M6,M2,M3断开,M1,M4导通,C1两端电压加在MS栅源两端,使MS栅源电压固定为VDD,不受输入信号的影响。M9在M1导通时起作用,避免M4栅源电压过高,M5可适当增大沟道长度,增加放电通路电阻,避免M6被击穿,他们的加入提高了器件的可靠性,不影响电路的功能。

4 两级运算放大器

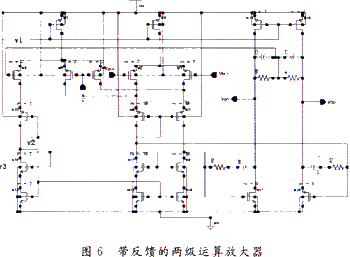

为了得到较大的增益和输出摆幅,采样保持电路的运算放大器采用两级结构,如图6所示,包括了运放的主电路和反馈电路。主电路的输入级采用共源共栅结构用以增大运放的增益,输出为共源结构。共模负反馈电路用来稳定全差分运算放大器输出共模电压,他的开环直流增益需与运放的差分开环直流增益相当,单位增益带宽也与运放的差分单位增益带宽值相当。此共模反馈电路结构共用了共模放大器和差模放大器的输入级中电流镜及输出负载。这样既可降低了功耗同时保证共模放大器与差模放大器在交流特性上保持完全一致。

为了使运放工作稳定,需将运放的相位裕度设计在60°左右。本文采用米勒电容[6]进行补偿,使电路的一个极点移向复频面的原点,另一个极点远离复频面原点,增大运放的相位裕度。再通过调零电阻与米勒电容串连,将由于米勒补偿电容在复频面的右半平面产生零点,移到左半平面并置于最高的非主极点,从而保证了运放的稳定性。

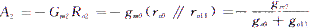

第一级放大器的增益为:![]()

第二级增益为:

运放的总增益为:

运放的第一极点为:![]()

第二极点为:

![]()

另外,图6中需要的偏置电压,采用宽摆幅共栅共源的电流源来产生,增大输入级的动态范围。

5 仿真结果

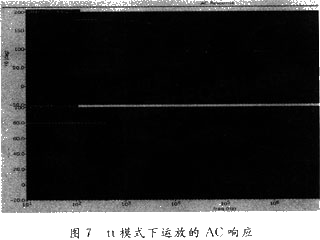

使用cadence仿真器specltre,采用SMIC标准O.25μm工艺库对其进行仿真,在单电源2.5 V供电条件下,运放的输入共模范围为O.75~1.75 V,在tt模式得到的AC响应如图7所示,开环直流增益为80 dB,相位裕度为62°,单位增益带宽160 MHz。

采用不同模式对其进行仿真得到结果如表1所示。

6 结 语

本文采用双采样的采样保持电路结构,在同等性能运放的条件下,采样频率比传统的单采样结构采样保持电路提高1倍。使用栅压自举电路,消除开关导通电阻的非线性,减小失真。采用的两级共栅共源运算放大器,使用cadence公司的spectre仿真器进行仿真,AC响应的开环增益达到80 dB,相位裕度为62°。整个采样保持电路在单电源2.5 V环境下工作,总体仿真达到高速高精度的要求。

- 相关阅读

向农,EEWORLD副总编。被英特尔董事长贝瑞特称为“中国可与之对话的两名记者之一”

向农,EEWORLD副总编。被英特尔董事长贝瑞特称为“中国可与之对话的两名记者之一”  汤宏琳,人皆称为“汤汤”,电子工程世界高级编辑。随着EEWORLD一起成长。

汤宏琳,人皆称为“汤汤”,电子工程世界高级编辑。随着EEWORLD一起成长。  今年,是中国集成电路产业丰收的一年,相比较往年都有大幅提升。

今年,是中国集成电路产业丰收的一年,相比较往年都有大幅提升。  一枚小小的车钥匙能做什么?可以遥控开启车门和后备箱就已经令你满意了吗

一枚小小的车钥匙能做什么?可以遥控开启车门和后备箱就已经令你满意了吗