ICSl523型同步时钟发生器的原理及应用

2007-12-24 13:16:26 作者:林云标 吴成柯等 来源:国外电子元器件关键字: 编程 硬件 接口 封装

1 引言ICSl523是一款高性能、低功耗的行同步信号发生器,它广泛应用于要求行同步、同步锁相的视频应用领域。由于采用低电压CMOS混合模式技术,使得它能够为视频工程及分辨率从VGA到UXGA的显示提供有效的时钟解决方案。ICSl523能够提供差分(高达250 MHz)或者单路格式(高达125 MHz)的像素时钟。动态相位调整电路可以控制像素时钟相对HYSNC的相位,先进的锁相环技术可以选择内部可编程分频或外部分频。所有的功能都可以通过行业标准的I2C总线以它的硬件接口进行配置。

2 主要特点和引脚功能

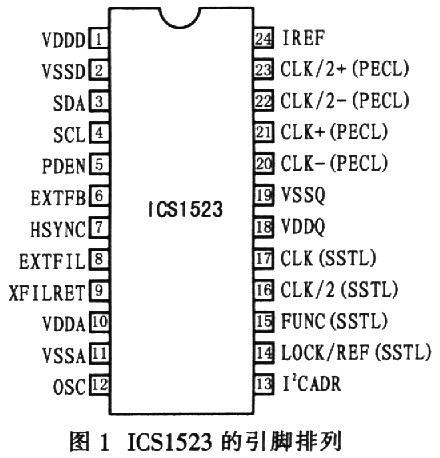

ICSl523的引脚排列如图1所示。它采用24引脚的SOIC封装。表1所列是其引脚功能。ICSl523的主要特点如下:

像素频率高达250 MHz;

频率抖动非常小;

动态调整输出时钟相位;

单终端SSTL_3时钟输出;

双缓冲的PLL/DPA控制寄存器;

可以分别对PLL和PDA软件复位;

可选择内部或者外部环路滤波器;

3.3 V工作电压,输入耐压高达5 V;

I2C串行接口既可以100 kHz工作,也可以400 kHz工作。

3 工作原理和内部寄存器

3.1 工作原理

ICSl523的内部组成框图如图2所示。

ICSl523的锁相环是针对行同步应用优化设计的。内部高性能施密特触发器在很短时间内对输入的HSYNC信号进行预处理,并将处理后的HSYNC作为干净的参考信号。预处理后的HSYNC信号或者HSYNC的恢复信号会在FUNC引脚上出现,这个输出信号与像素时钟的边界对齐。

ICSl523内部具有自动上电复位检测电路,如果输入电压值低于它的门限值会自动复位,因而没有必要连接外部复位信号。

动态相位调整功能使得它能够输出相关的HSYNC信号,并且延时于像素时钟的输出信号,延迟的大小可以通过编程的方式设置。增加延时功能在多个视频源要求必须同步时显得非常有用。

ICSl523使用行业标准的I2C串行总线接口进行编程。通过该接口能够访问内部的12个寄存器:1个只写寄存器、8个读写寄存器和3个只读寄存器。根据引脚I2CADR的状态可分别访问2个ICSl523。当此引脚为低电平时,读地址是4DH,写地址是4CH。如果是高电平,则它的读地址是4FH,写地址是4EH。I2C总线接口既可以低速(100 kHz)工作,也可以高速(400 kHz)工作,并且有5V耐压。

3.2 内部寄存器

ICSl523有12个控制寄存器,分别为输入控制寄存器、锁相控制寄存器、反馈分配0和l寄存器、DPA偏移寄存器、DPA控制寄存器、输出使能寄存器、晶体振荡器分配寄存器、复位寄存器、电路版本寄存器和状态寄存器。下面介绍几个重要的寄存器。

(1)状态寄存器(Status Register)

DPA_LOCK:动态相位调整锁定标志,0=没有锁定,l=锁定。

PLL_LOCK:锁相环锁定标志,同上。

D2-D7:Reserved。

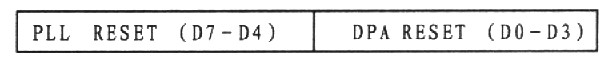

(2)复位寄存器(Reset Register)

DPA RESET:复位动态相位调整工作寄存器,写XAh表示复位DPA工作寄存器。

PLL RESET:复位锁相环工作寄存器,写5Xh表示复位PLL工作寄存器。

其中,写5Ah表示同时复位2个工作寄存器。

(3)晶体振荡器分频寄存器

![]()

Osc_Div:OSC(12引脚)/设置的系数(设置的数值+2)。

ln_Sel:选择相位/频率检测器的输入信号,0=HSYNC,1=OSC分频器。

(4)输出使能寄存器(Output Enable Register)

EnDLS:使能DPA锁存状态输出到LOCK/REF脚。

EnPLS:使能PLL锁存状态输出到LOCK/REF脚。

Func_Sel:功能输出选择,0=恢复的HSYNC,1=外部的HSYNC。

Fbk_Sel:反馈选择,0=内部反馈,l=外部反馈。

4 典型应用

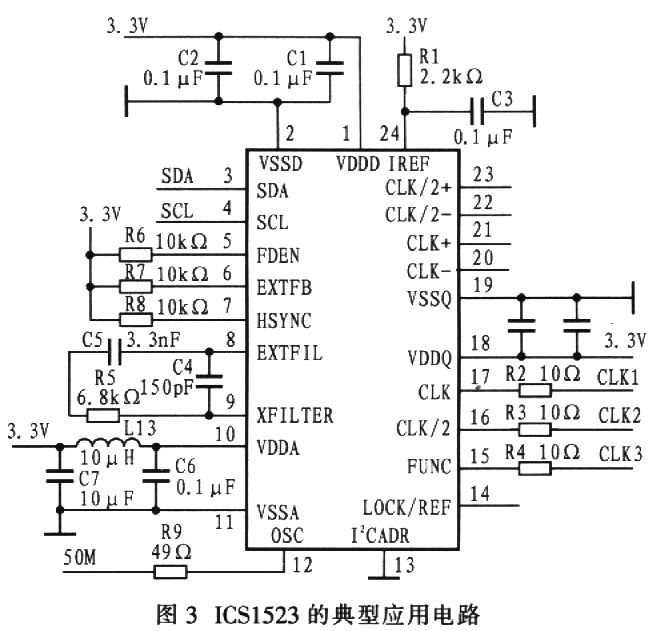

4.1 硬件电路

ICSl523的典型应用电路如图3所示,该电路为SIDl3806型显示控制器提供视频同步信号。这些信号是SIDl3806连接LCD时所需要的。ICSl523输入时钟是50 MHz(引脚12)、输出CLKl(25 MHz)、CLK2(12.5 MHz)和CLK3(387.6 kHz)分别接S1D13806的BUSCLK(60引脚)、CLKl(66引脚)、CLKl2(64引脚)和CLKl3(引脚)。

4.2 软件配置

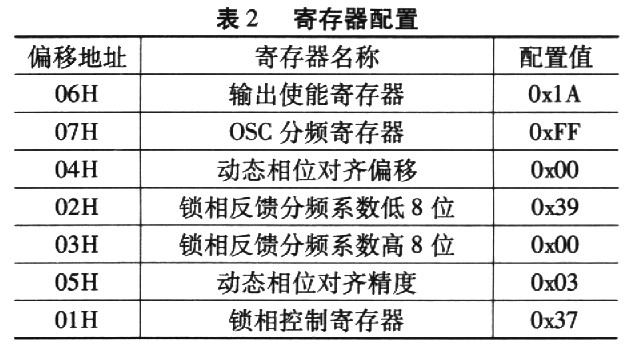

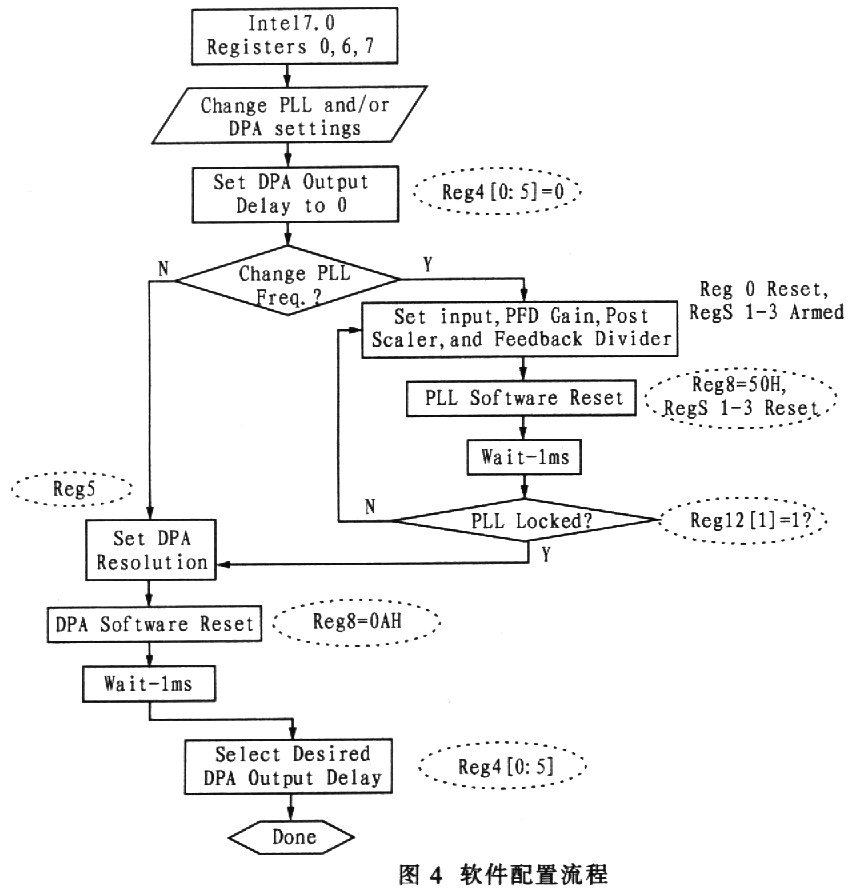

软件配置流程如图4所示,详细配置过程见下文给出的部分配置程序。结合典型应用还给出相关寄存器的具体配置数值,如表2所示(这些值可通过ICSl523专用软件获取)。

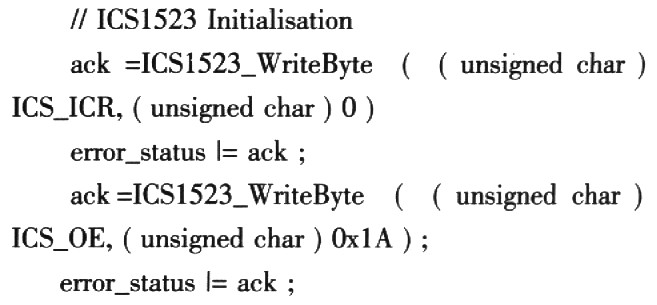

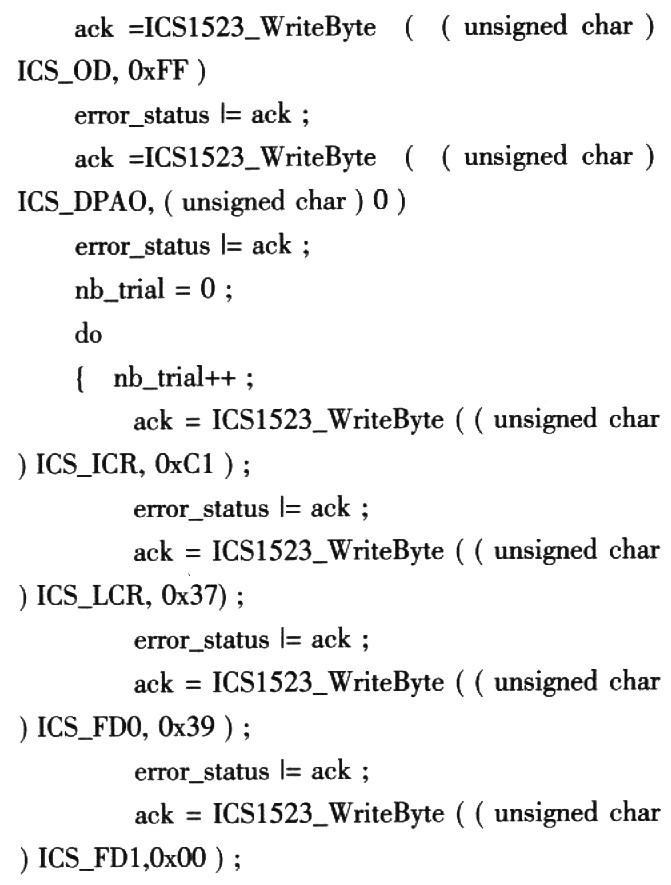

配置程序:

5 结束语

本文提供的硬件电路及寄存器配置值已经在实际应用中得到验证,是完全正确的。ICSl523为视频领域提供了一种很好的视频时钟解决方案。

- 相关阅读

向农,EEWORLD副总编。被英特尔董事长贝瑞特称为“中国可与之对话的两名记者之一”

向农,EEWORLD副总编。被英特尔董事长贝瑞特称为“中国可与之对话的两名记者之一”  汤宏琳,人皆称为“汤汤”,电子工程世界高级编辑。随着EEWORLD一起成长。

汤宏琳,人皆称为“汤汤”,电子工程世界高级编辑。随着EEWORLD一起成长。  今年,是中国集成电路产业丰收的一年,相比较往年都有大幅提升。

今年,是中国集成电路产业丰收的一年,相比较往年都有大幅提升。  一枚小小的车钥匙能做什么?可以遥控开启车门和后备箱就已经令你满意了吗

一枚小小的车钥匙能做什么?可以遥控开启车门和后备箱就已经令你满意了吗