1 系统介绍

1.1 系统构成

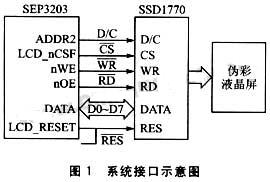

系统主要由SEP3203处理器和伪彩点阵型图形LCD控制器SSD1770组成,系统接口示意图如图1所示。

1.2 SEP3203概述

SEP3203是由东南大学国家专用集成电路(ASIC)与系统工程技术研究中心设计的一款基于ARM7TDMI内核的16/32位RISC微控制器,面向低成本手持设备和其他通用嵌入式设备,它集成了支持黑白、灰度、彩色的LCD控制器,SEP3203中的彩色LCD控制器主要用于TFT真彩显示,不能直接控制CSTN(伪彩)显示,须通过外接伪彩控制器来实现伪彩显示。

SEP3203处理器内嵌20KB零等待的

1.3 SSD1770概述

SSD1770是一个单片高度集成的伪彩点阵型LCD控制驱动器件,它内含312×81×4位的图形数据显存GDDRAM和477KHz的振荡电路,集成偏压电路和DC-DC电路,具有8位PPI接口(可直接连接80/68xx MCU)、3/4线SPI串行接口和36条控制/传输指令。外加几个电容器件,SSD1770就可控制驱动104RGB×81点彩色STN型LCD,4096种颜色。

1.4 电压匹配

SSD1770 CMOS电源提供电压为1.8-3.6V,而SEP3203输入/输出电压最小为2.7V,最大为3.6V,前者的输出可以直接作为后者的输入,无须进行电平转换。

2 硬件设计

SEP3203接口协议如图2所示。

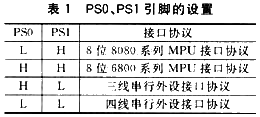

SSD1770同时有4种信号接口协议:1)8位8080系列MPU接口协议;2)8位6800系列MPU接口协议;3)三线串行外设接口协议;4)四线串行外设接口协议。不同的接口协议可通过PS0、PS1引脚的设置来实现,如表1所列。

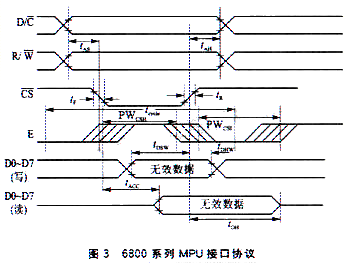

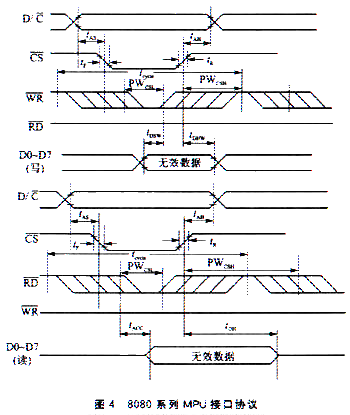

由于本设计中传输距离不需要过长,且考虑到速度问题,所以选择并行接口协议,SSD1770支持2种并口模式:一种是6800系列MPU接口协议,如图3所示,另一种是8080系列MPU接口协议,如图4所示。

将SEP3203接口协议与这两种MPU接口协议相比,可知SEP3203的接口协议属于8080系列MPU接口协议,因此,采用8080接口实现SSD1770与SEP3203的连接。

SEP3203所用的接口引脚是外部存储接口模块(External Memory Interface,简称EMI)中的8位数据总线、输出使能、写使能、地址总线、NAND Flash准备就绪/忙和控制时钟中低电平有效的Reset,EMI的功能即提供对外部存储器的读/写接口。

SEP3203的主要引脚定义如下:

nOE:读使能信号,表示当前周期执行读操作。

nWE:写使能信号,表示当前周期执行写操作。

LCD_nCSF:片选信号。

DATA:外部数据总线。

ADDR:外部地址总线。

SSD1770的主要引脚定义如下。

D0-D7:并行接口方式,双向数据总线。

RES:复位信号输入,低电平有效。

D/C:数据或命令选择引脚,若为1,则数据总线上的信息当做显示数据,若为0,则数据总线上的信息发送到命令寄存器。

CS:片选信号输入,低电平有效。

RD:与8080CPU接口时,为写信号输入,低电平有效。

WR:与8080CPU接,用于写信号(低电平有效)。

与8080系列CPU并行接口,由8位双向数据脚D0-D7、RD、WR、D/C、CS组成,根据8080CPU接口协议,SSD1770的D0-D7、RD、WR、RES、D/C、CS引脚分别与SEP3203的PORTB、nOE、nWE、LCD_RESET、ADDR2、LCD_nCSF引脚相连,如图5所示。

CS信号直接由SEP3203的LCD_nCSF控制。如果CS是低电平且RD为低,则RD输入作为读数据锁存信号;无论是从GDRRAM读显示数据还是从状态寄存器读状态都需要D/C脚的控制,如果CS是低电平且WR为低,则WR输入作为写数据锁存信号,无论是写显示数据到GDDRAM还是将命令写入命令寄存器都需要D/C脚的控制,第一有效数据读之前,需要一次虚拟读。为了不产生错误操作,在SSD1770与SEP3203控制信号之间使用CMOS芯片,由图5可知,控制信号D/C、CS、WR、RD都是单向的,所以使用1片单向的CMOS八位锁存74LS373控制;而D0-D7是双向的,因此采用1片双向的74LS245缓冲,具体电路连接如图5所示。

3 软件设计

3.1 软件系统

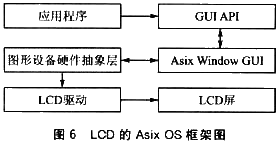

LCD的软件驱动程序是在嵌入式操作系统Asix OS上运行的。Asix OS系统是由国家ASIC系统工程技术研究中心开发的一种嵌入式操作系统,具有设计简洁、模块化、易移植、功耗低等特点,它是基于uITRON3.0的TKernel,由设备驱动、内核、文件系统、图形用户接口以及系统级服务5个模块组成,结合LCD的具体运用,设计的Asix OS框架如图6所示。

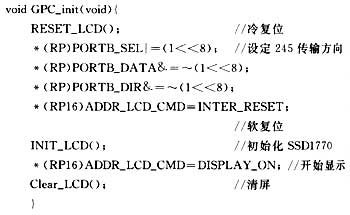

3.2 LCD初始化

在Asix OS系统之上,LCD的驱动程序通过SSD1770的初始化流程,命令参数列表以及其他资料来编写,SSD1770的访问有2

首先计算SSD1770的各端口地址。SEP3203的片选信号LCD_nCSF所对应的基址为0x34000000,所以设定SSD1770的访问地址为0x34000010,RAM的访问地址为0x34000018,软件设计的流程图如图7所示。

初始化程序如下:

4 结论

本设计不仅是对晶门科技公司新推出的单片CMOS彩色STN-LCD驱动控制器在嵌入式系统中应用的扩展,而且满足了东南大学ASIC中心设计的嵌入式处理器SEP3203外接伪彩显示的需求。既实现了在具有友好界面的工控系统中的应用,又可以在更多想要具有友好界面的系统中得到推广。

上一篇:PCI9052接口电路的功能及应用

下一篇:显示控制器S680724的接口技术

推荐阅读最新更新时间:2024-05-13 18:16

整车控制策略开发需求分析及新能源汽车动力总成测试系统

整车控制策略开发需求分析及新能源汽车动力总成测试系统 ICCV2023论文汇总:Embodied Vision: Active Agents, Simulation(具身视觉:主动代理、模拟)

ICCV2023论文汇总:Embodied Vision: Active Agents, Simulation(具身视觉:主动代理、模拟) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号