凔海笔记之FPGA(六):二进制的加法番外篇

貌似在会说话的时候,妈妈就会问,这是几?1+1等于几?如果伸出两个手指头或是说个2,那幸福日子就来了,若是蹦出三个手指头,呵呵……。

咱打小学的就是满十进一的运算,也就是十进制,而对于数字系统来说,它只有高低电平,所以只有0和1。然而就是这些0和1,若我们按一定的顺序排列,就可以表示一些自己想要的东西了,这和十进制数一样,我们可以说119是一百一十九,也可以认为是火警电话,就看在什么语境下了。对于10进制的数学运算,例如146+179=325,计算方式就是由低位到高位进行满十进一。同理可得,二进制的数学运算也是如此。

例如:11+10=101(3+2=5),1001+1100=10101(9+12=21),由右向左,满二进一。我们的计算机就是进行二进制计算的,Why?因为在数字系统中,只有高电平和低电平,如果有“中电平”这么个东西的话可能就是三进制了。那么,用逻辑器件是如何实现的呢?

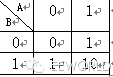

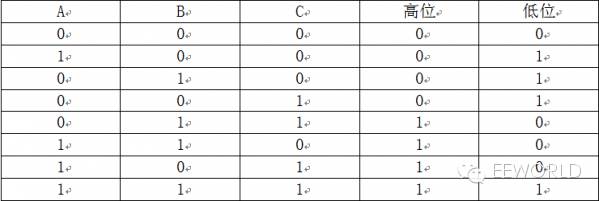

先看一位的,列个表看一下一位二进制A+B?

看这表可以发现,0+0=0,0+1=1,1+0=1,但当A、B同时为1时,是个麻烦事,因为1+1=2有个进位。所以,以防AB均为1时出现尴尬,需要俩个输出来表示。这样说来,就需要一位表示二进制的第一位,一位表示二进制的第二位,这个第二位是因为进位产生的,所以这个位被称之为“进位”,而第一位被叫做“和”。总得来说,当A+B时,有俩个位数来记录它们的输出,分别为和和进位。

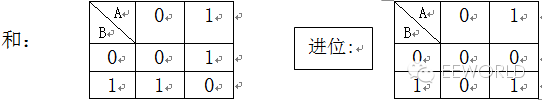

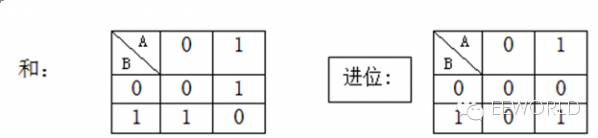

现在将上表分为和和进位俩表如下:

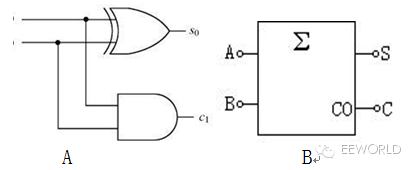

很显然,对于A+B的“和”,就是当AB不一样的时候为1,对于“进位”,就是当AB均为1的时候为1。所以,A+B的运算可以由异或和与门组成,将异或门输出作为“和”,将与门输出作为 “进位”如下图A:

这样A+B的任意情况就都满足了,这个东西有个学名,叫做半加器,如图B, S(sum)是“和”,C(carry-over)是“进位”。为什么叫半加器呢?往下看。

如果A=11,B=11,可以用我们聪明的大脑计算出A+B=110,如何把这个计算用硬件实现呢?用俩个半加器可以吗?是不是感觉无从下手,俩个如何连在一块?对于第一位1+1会产生进位,那这个进位参与第二位的相加,三个数又该如何输入?所以说,半加器是无法实现对进位的处理,更无法进行多位的计算。

估计这就是为什么叫半加器了,它解决不了进位问题啊。所以说,对于多位二进制相加,这个器件需要实现3位数的相加。其中一位是由前一位决定的。怎么实现?所以,现在开始想如何实现三个二进制相加。也就是说,我们要构造一个这样的东西:

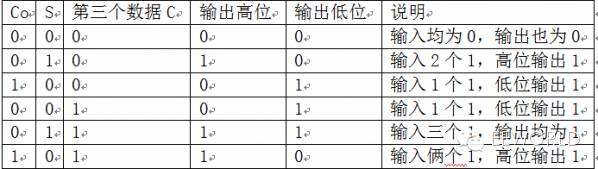

输入是三个数,输出是这三个数相加的结果0(00)到3(11)。而我们要实现的功能如下表:

学过数电的一定知道,通过此表就可以得出全加器的逻辑图,因为我们有万能的韦恩图。但是,太麻烦了,太死板了,不想用,所以咱走走歪门邪道吧,没准还行。

由表可知,对于高位来说,有两个及以上个1则为1,对于低位,有奇数个1则为1。看到这个规律,我是有个想法,就是判断是几个1,来决定高位和低位的输出是什么。三位一起判断,咱不会,可以俩位俩位的判断嘛。这时你有没有想到半加器?为什么我想到他了呢?

再看这图,我想回顿悟的。如果没有看下表,如果有的话goto Loop。

对于AB的三种情况:俩个1、一个1、零个1,和和进位也会不同,恰好满足咱们的需要。

Loop:上面我们已经想到了对于俩个输入数据做判断了,那么接下来就该和第三个判断了,如何判断,看表,省事。

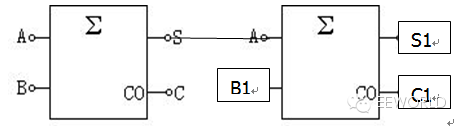

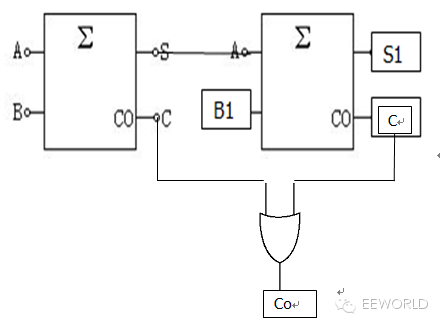

由上表可以得出结论,当Co为1,或者S和C同时为,则高位输出1,这时有俩种情况,S和第三个数据有一个为1,则为1。那么,这又可以用一个半加器了,

把第二个半加器的一个输入端改为B1,令它为第三个数,这样实现了三个数的输入。可是呢?第一个半加器的C怎么处理,当AB不全为1时,C为1,而第二个半加器的C,等等,是否意识到了一个问题,更惊奇的是S1和C1不能同时为1,

这就完成了,

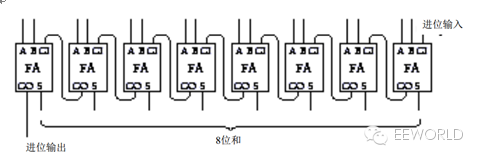

下面,来把它扩展到八位,这个应该很简单了吧。

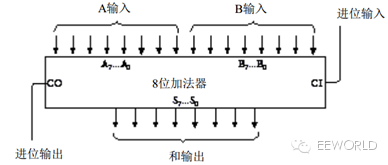

然后,对其进行封装

这就完成了对8位二进制数的相加运算,但须注意的是,这是8位无符号二进制相加。

欢迎观看:

近期精彩内容推荐:

京公网安备 11010802033920号

京公网安备 11010802033920号