1 引言

多次重触发技术应用于多种场合,如一个30齿的齿轮,设齿轮啮台系数为1.2,若测量其中1齿多次啮合时的应力,则1齿的啮合时间只占齿轮转l圈时间的1.2/30,其余28.8/30的时间为空闲态,而空闲态记录无意义。为此开发多次重触发技术,以齿应力作为内触发信号,只记录每次触发后的有用信号,并具有负延迟,而不记录空闲状态.直到占满记录装置存储空间,这样可有效利用存储空间,记录更多的有用信号。

2 多次重触发存储测试系统总体设计

2.1 多次重触发存储测试系统工作原理

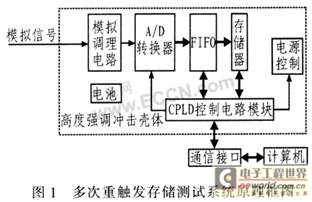

图1为多次重触发存储测试系统原理框图,其工作原理:被测信号经传感器变为电信号后,输入至模拟调理电路,再经放大滤波后输入至A/D转换器,将模拟信号转换为数字信号,然后经过FIFO传输给存储器,计算机通过通信接口读取数据。其中,该存储测试系统的A/D转换器的转换和读时钟、FIFO及存储器的读写时钟、推地址时钟均由CPLD控制产生。

2.2 负延迟的实现

动态信息存储要求真实有效地记录有用信号,根据被测信号特点,需记录下触发前信号在极短时间内的数据,这就要使用负延迟技术。负延迟也称为提前传输,即将触发信号的触发采集时刻提前一段时间作为传输数据的起始点。该系统设计采用FIFO存储器实现负延负延迟。触发信号未到来时,A/D转换器输出的数据不断写入FIFO存储器中,A/D转换器转换的数据不断刷新FIFO存储器的内容。一旦触发信号到来,数据则开始从FIFO写入存储器。

2.3 主要器件选型

该系统设计选用AD7492型A/D转换器。该器件为12位高速、低功耗、逐次逼近式A/D转换器。在5 V电压,速率为1 MS/s时,其平均电流仅1.72 mA,功耗为8.6 mW;在5 V电压和500 kS/s数据传输速率下,消耗电流1.24 mA,因此,该器件能够满足系统低功耗要求。由于该系统设计的存储器总体容量为512 KB,因此选用l片容量为512 KB的N08T163型存储器。并通过静态存储器时序配合实现自制的FIFO存储器,功耗约为同类FIFO存储器的1/10。系统设计的负延迟记录l KB,选用128 KB容量的N02L163WC2A型存储器。针对存储测试系统功耗低,体积小,且控制逻辑较复杂的因素,MAX7000B系列的EPM7128BTCl44-4型CPLD作为控制器。该器件是高性能,低功耗的CMOS型CPLD,2500个可用逻辑门电路,引脚到引脚的传输延时为4.0 ns,系统工作频率高达243.9 MHz。

3 CPLD控制电路的设计

基于CPLD的多次重触发存储测试系统主要由A/D转换器、存储器、FIFO和控制器CPLD等组成,其中CPLD控制电路由时钟、多次重触发、FIFO地址发生、存储器地址发生、存储器计满,电源管理和计算机通信等模块组成,如图2所示。

3.1 控制电路各模块功能

(1)电源管理模块 该模块主要控制系统功耗。当系统处于休眠状态时,只有Vcc对CPLD供电;当系统进入正常工作状态时,Vcc,VDD和VEE同时供电,晶振工作,当采样结束,系统关闭VEE,模拟部分进入休眠状态,晶振停止工作。该模块能够满足系统低功耗要求。

(2)时钟模块 晶振提供的4 MHz信号经4个二分频器,分别得到2 MHz、1 MHz、500 kHz和250 kHz的时钟信号,由这些信号组合得到A/D转换器的采样信号convst、FIFO的写信号、A/D转换器的读信号ffwr_adread以及FIFO的推地址信号ff_dz,均为250 kHz。

(3)多次重触发模块 当外界多次重触发信号m_tri到来后。经D触发器产生的open信号变为高电平,计数器开始计数时钟信号ff_dz,每计8 KB后停止计数,并产生清零信号clr对open信号清零,等待下次触发信号。由时钟信号ff_dz和open信号控制产生的时钟信号clkl作为写存储器时的推地址信号和写信号,open信号取反后接至存储器使能端。

(4)FIFO地址发生模块CPLD对FIFO的地址控制由时钟模块ff_dz信号产生,在时钟信号ff_dz的下降沿开始推FIFO地址。[page]

(5)存储器地址发生模块 多次重触发模块产生clkl信号作为存储器的推地址信号m_dz推地址,将转换数据写入存储器,写满8 KB后停止写操作,等待下次触发信号。存储器存满512。KB后停止推地址和写操作,等待计算机读数。读数时,计算机每向CPLD发送1个读数脉冲,地址信号向前推进1位,CPLD就从存储器中对应的地址单元读取1个数据。

(6)存储器计满模块 当多次重触发信号m_tri到来后,open信号变为高电平,计满8 KB后变为低电平,等待下次触发信号。因此用计数器计数open信号下降沿,计满64个后存储器满信号tc变为高电平。

3.2 CPLD总体控制电路仿真及分析

图3为CPLD总体控制电路仿真图。图3中触发信号m_tri产生3次,由nopen信号看出存储器选通3次,由存储器地址信号m_addr的变化可看出存储器记录每个触发信号8 KB,并不断更新FIFO的数据。第1个触发信号m_tri到来后,nopen信号变为低电平即选通存储器。这时产生存储器的推地址信号和写信号m_dz信号,并且在下降沿时将推地址给存储器,存储器在低电平期间进行写操作。触发信号m_tri到来后计满8 KB,nopen信号产生高电平不选通存储器,且存储器的推地址信号和写信号m_dz变为高电平。

4 实验验证

通过实验验证该测试系统功能。实验中给测试系统加载8次触发信号,连续采集8次。由于该系统设计最多可以采样64次,如果重触发信号次数未达到64次,需手动给测试仪一个强制读数信号使得仪器采样结束。多次重触发信号8次有效后,手动强制读数信号使得仪器结束采样,通过上位机软件判断采集到的波形幅值和手动调节的幅值是否对应。若对应,表明系统采样正常。

实验步骤:测试仪接通电源,此时测试仪采样状态指示灯的红灯亮,和计算机接上编程读数线,打开编程界面,设置多次重触发的采样频率,其他选项均采用默认设置,编程完成后,拔掉编程读数线,测试仪上电(ON=0),红灯开始闪烁,将电荷校准仪的输出接到测试仪面板上的通道端,设置电荷校准仪的输出波形为正弦波,电荷量为2 000 PC,输出信号,给系统一个触发信号(M_TRI=1),红灯闪烁一段时间后停止闪烁,表明系统第一次采样完成,这时调节电荷校准仪的输出电荷量为4 000 PC。再给系统一个触发信号,重复前面过程,每次采样完成后改变电荷量,直到绿灯亮,和计算机连上编程读数线,通过上位机软件读取数据,待数据读取完毕,测试仪掉电(OFF=0),断开测试仪电源。图4为多次重触发波形。对图4中的数据进行转换和处理得到实测的电荷量值如表1所示,从表1看出,采集到的波形幅值与调节的顺序一致,系统设计符合要求。

5 结论

本文设计的基于CPLD的多次重触发存储测试系统性能较稳定,测量精度较高,能在高冲击等恶劣环境下正常工作,并且满足系统的低功耗、微型化要求,实现不失真采样存储信号。此系统能够实时记录多次重触发信号,每次信号的记录均有负延迟,读取数据时,无需程序调整,即可准确复现记录波形,因此存储测试技术在多个瞬态信号的测量中具有广阔前景。

关键字:CPLD 存储测试系统 波形仿真

引用地址:基于CPLD的多次重触发存储测试系统设计

多次重触发技术应用于多种场合,如一个30齿的齿轮,设齿轮啮台系数为1.2,若测量其中1齿多次啮合时的应力,则1齿的啮合时间只占齿轮转l圈时间的1.2/30,其余28.8/30的时间为空闲态,而空闲态记录无意义。为此开发多次重触发技术,以齿应力作为内触发信号,只记录每次触发后的有用信号,并具有负延迟,而不记录空闲状态.直到占满记录装置存储空间,这样可有效利用存储空间,记录更多的有用信号。

2 多次重触发存储测试系统总体设计

2.1 多次重触发存储测试系统工作原理

图1为多次重触发存储测试系统原理框图,其工作原理:被测信号经传感器变为电信号后,输入至模拟调理电路,再经放大滤波后输入至A/D转换器,将模拟信号转换为数字信号,然后经过FIFO传输给存储器,计算机通过通信接口读取数据。其中,该存储测试系统的A/D转换器的转换和读时钟、FIFO及存储器的读写时钟、推地址时钟均由CPLD控制产生。

2.2 负延迟的实现

动态信息存储要求真实有效地记录有用信号,根据被测信号特点,需记录下触发前信号在极短时间内的数据,这就要使用负延迟技术。负延迟也称为提前传输,即将触发信号的触发采集时刻提前一段时间作为传输数据的起始点。该系统设计采用FIFO存储器实现负延负延迟。触发信号未到来时,A/D转换器输出的数据不断写入FIFO存储器中,A/D转换器转换的数据不断刷新FIFO存储器的内容。一旦触发信号到来,数据则开始从FIFO写入存储器。

2.3 主要器件选型

该系统设计选用AD7492型A/D转换器。该器件为12位高速、低功耗、逐次逼近式A/D转换器。在5 V电压,速率为1 MS/s时,其平均电流仅1.72 mA,功耗为8.6 mW;在5 V电压和500 kS/s数据传输速率下,消耗电流1.24 mA,因此,该器件能够满足系统低功耗要求。由于该系统设计的存储器总体容量为512 KB,因此选用l片容量为512 KB的N08T163型存储器。并通过静态存储器时序配合实现自制的FIFO存储器,功耗约为同类FIFO存储器的1/10。系统设计的负延迟记录l KB,选用128 KB容量的N02L163WC2A型存储器。针对存储测试系统功耗低,体积小,且控制逻辑较复杂的因素,MAX7000B系列的EPM7128BTCl44-4型CPLD作为控制器。该器件是高性能,低功耗的CMOS型CPLD,2500个可用逻辑门电路,引脚到引脚的传输延时为4.0 ns,系统工作频率高达243.9 MHz。

3 CPLD控制电路的设计

基于CPLD的多次重触发存储测试系统主要由A/D转换器、存储器、FIFO和控制器CPLD等组成,其中CPLD控制电路由时钟、多次重触发、FIFO地址发生、存储器地址发生、存储器计满,电源管理和计算机通信等模块组成,如图2所示。

3.1 控制电路各模块功能

(1)电源管理模块 该模块主要控制系统功耗。当系统处于休眠状态时,只有Vcc对CPLD供电;当系统进入正常工作状态时,Vcc,VDD和VEE同时供电,晶振工作,当采样结束,系统关闭VEE,模拟部分进入休眠状态,晶振停止工作。该模块能够满足系统低功耗要求。

(2)时钟模块 晶振提供的4 MHz信号经4个二分频器,分别得到2 MHz、1 MHz、500 kHz和250 kHz的时钟信号,由这些信号组合得到A/D转换器的采样信号convst、FIFO的写信号、A/D转换器的读信号ffwr_adread以及FIFO的推地址信号ff_dz,均为250 kHz。

(3)多次重触发模块 当外界多次重触发信号m_tri到来后。经D触发器产生的open信号变为高电平,计数器开始计数时钟信号ff_dz,每计8 KB后停止计数,并产生清零信号clr对open信号清零,等待下次触发信号。由时钟信号ff_dz和open信号控制产生的时钟信号clkl作为写存储器时的推地址信号和写信号,open信号取反后接至存储器使能端。

(4)FIFO地址发生模块CPLD对FIFO的地址控制由时钟模块ff_dz信号产生,在时钟信号ff_dz的下降沿开始推FIFO地址。[page]

(5)存储器地址发生模块 多次重触发模块产生clkl信号作为存储器的推地址信号m_dz推地址,将转换数据写入存储器,写满8 KB后停止写操作,等待下次触发信号。存储器存满512。KB后停止推地址和写操作,等待计算机读数。读数时,计算机每向CPLD发送1个读数脉冲,地址信号向前推进1位,CPLD就从存储器中对应的地址单元读取1个数据。

(6)存储器计满模块 当多次重触发信号m_tri到来后,open信号变为高电平,计满8 KB后变为低电平,等待下次触发信号。因此用计数器计数open信号下降沿,计满64个后存储器满信号tc变为高电平。

3.2 CPLD总体控制电路仿真及分析

图3为CPLD总体控制电路仿真图。图3中触发信号m_tri产生3次,由nopen信号看出存储器选通3次,由存储器地址信号m_addr的变化可看出存储器记录每个触发信号8 KB,并不断更新FIFO的数据。第1个触发信号m_tri到来后,nopen信号变为低电平即选通存储器。这时产生存储器的推地址信号和写信号m_dz信号,并且在下降沿时将推地址给存储器,存储器在低电平期间进行写操作。触发信号m_tri到来后计满8 KB,nopen信号产生高电平不选通存储器,且存储器的推地址信号和写信号m_dz变为高电平。

4 实验验证

通过实验验证该测试系统功能。实验中给测试系统加载8次触发信号,连续采集8次。由于该系统设计最多可以采样64次,如果重触发信号次数未达到64次,需手动给测试仪一个强制读数信号使得仪器采样结束。多次重触发信号8次有效后,手动强制读数信号使得仪器结束采样,通过上位机软件判断采集到的波形幅值和手动调节的幅值是否对应。若对应,表明系统采样正常。

实验步骤:测试仪接通电源,此时测试仪采样状态指示灯的红灯亮,和计算机接上编程读数线,打开编程界面,设置多次重触发的采样频率,其他选项均采用默认设置,编程完成后,拔掉编程读数线,测试仪上电(ON=0),红灯开始闪烁,将电荷校准仪的输出接到测试仪面板上的通道端,设置电荷校准仪的输出波形为正弦波,电荷量为2 000 PC,输出信号,给系统一个触发信号(M_TRI=1),红灯闪烁一段时间后停止闪烁,表明系统第一次采样完成,这时调节电荷校准仪的输出电荷量为4 000 PC。再给系统一个触发信号,重复前面过程,每次采样完成后改变电荷量,直到绿灯亮,和计算机连上编程读数线,通过上位机软件读取数据,待数据读取完毕,测试仪掉电(OFF=0),断开测试仪电源。图4为多次重触发波形。对图4中的数据进行转换和处理得到实测的电荷量值如表1所示,从表1看出,采集到的波形幅值与调节的顺序一致,系统设计符合要求。

5 结论

本文设计的基于CPLD的多次重触发存储测试系统性能较稳定,测量精度较高,能在高冲击等恶劣环境下正常工作,并且满足系统的低功耗、微型化要求,实现不失真采样存储信号。此系统能够实时记录多次重触发信号,每次信号的记录均有负延迟,读取数据时,无需程序调整,即可准确复现记录波形,因此存储测试技术在多个瞬态信号的测量中具有广阔前景。

上一篇:用PLD简化边界扫描测试

下一篇:晶体和掩膜质量控制检测

推荐阅读最新更新时间:2024-03-30 22:51

基于ARM9和CPLD的输入输出系统设计

简介:嵌人式丁业控制系统的突出特点是在高低温、高电磁辐射环境下的抗干扰性和可靠稳定性。和PLC系统相比。其明显的优点是处理速度快、方便进行工业以太网的组建、编程方便、通用性好,而且价格仅仅是PLC的几分之一,具有很好的发展前景。本论文主要论述了以EP9315和MAX2_EPM240为核心的嵌入式输入输出系统的设计。 1 系统构成 整个嵌入式输入输出系统分为嵌入式系统、应用模块(即输入输出模块)和转换模块三部分,总体结构如图1所示。 图1系统结构框图 1.1 嵌入式系统 本设计选择CirrusLogic公司高性能的ARM9嵌入式微处理器EP9315.该微处理器具有ARM920T内核所有的优异性能。丰富的集成外设

[单片机]

基于DSP与CPLD的多通道数据采集系统的设计

用于实时控制系统的嵌入式系统经常需要对模拟量进行测量,通常的方法是以MCU为主产生采集控制时序控制模数转换器,并通过中断或查询的方式读取转换后的结果。由MCU产生采集控制时序将占用较多的系统软硬件资源。而在一般复杂的多路信号测控系统中,MCU需要进行数据存储,通讯,数据处理等多项工作,如果再需要其频繁地产生模数转换控制器的控制时序,将会影响系统的性能,严重时将会成为系统的瓶颈。本文采用CPLD产生A/D转换器的控制时序,使得CPLD主要实现A/D时序控制的功能,DSP主要实现闭环控制算法的功能。 1 系统总体结构 系统以DSP和CPLD为核心,模拟信号从模拟多路开关CD4067接人,利用CPLD进行使能其输入。使用D

[工业控制]

基于CPLD的脉冲密度功率调节高频逆变电源

目前,高频感应加热电源的输出功率调整主要是通过改变逆变器的输出频率或改变逆变器的输入直流电压方式来实现的。改变逆变器的输出频率实现输出功率的调节是目前普遍采用的一种功率调节方式,其缺点是逆变器的负载为感性,特别是在轻载时,逆变器的输出功率因数很低,开关损耗大。通过控制逆变器实现功率控制就能改变这一缺点。脉冲密度调制(Pulse Density Modulated,PDM)DC/AC逆变器是利用串联谐振负载的储能,对逆变器的开关采用脉冲群控制的方式,在一个周期内通过控制连续开通脉冲信号和连续关断脉冲信号的比例(占空比)来控制输出功率。传统的PDM实现方式是用许多计数器以及一些PWM专用芯片来实现的,这种方法稳定成熟,但控制电路复杂。

[电源管理]

采用单片机和CPLD控制的任意波形发生器的设计

在电子工程设计与测试中,常常需要一些复杂的、具有特殊要求的信号,要求其波形可任意产生,频率方便可调。

结合实际需要,我们设计了一种任意波形发生器。电路设计中充分利用MATLAB的仿真功能,将希望得到的波形信号在MATLAB中完成信号的产生、抽样和模数转换,并将得到的数字波形数据存放在数据存储器中,通过单片机和CPLD控制,将波形数据读出,送入后向通道进行A/D转换和放大处理后得到所需的模拟信号波形。利用上述方法设计的任意波形发生器,信号产生灵活方便、功能扩展灵活、信号参数可调,实现了硬件电路的软件化设计。 系统框图 任意波形发生器的设计思想,是利用MATLAB的强大仿真功能,方便、快捷的生成给定频率、周期、脉宽的任意波形

[模拟电子]

CPLD应用航空1l5V/400Hz高频链逆变电源

0 引言 航空配电系统所用l15V/400Hz电源一般是由直流逆变所得,主要供军用飞机、雷达等设备使用。逆变电源中的能量转换过程是,直流电通过逆变电路变换成高频脉冲电压,经滤波电路形成正弦波。近来,高频链逆变技术引起了人们越来越浓的研究兴趣。高频链逆变技术用高频变压器来代替传统逆变器中笨重的工频变压器,大大减小了逆变器的体积和重量。高频链逆变技术是由Mr.Espelage于1977年提出的,它与常规的逆变技术最大的不同在于利用高频变压器实现了输入与输出的电气隔离,减小了变压器的体积和重量。 传统的高频链逆变器由常规数字电路构成,存在设计复杂、抗干扰能力差等缺点。为了解决该问题,本文采用复杂可编程逻辑器件(CPL

[嵌入式]

基于CPLD的驱动数码显示电路设计案例

显示原理: 八段数码显示管如图1.1 所示,八段数码管每一段为一发光二极管,共有a~g 以及小数点dp 八个发光二极管。将八段数码管中的每个二极管的阴极并联在一起,组成公共阴极端。这样把共阴极管脚接地,此时哪个管脚输入高电平,对应发光二极管就被点亮。 图 1.1 八段数码显示管 CL5461AS 数码管管脚图如图1.2 所示,它将四个数码显示管的a~g 及小数点dp 管脚并联在一起,作为数码管数据输入端;分别引出各个数码管的阴极A1~A4。 图1.2 CL5461AS 数码管管脚图 只要在A1~A4 管脚上轮流加低电平其频率大于40Hz,可实现四个数码管同时被点亮的视觉效果。在点亮不同数码管的同时输入不同的数据,

[工业控制]

利用可编程逻辑器件实现灵活的电源管理

电源管理一般是指涉及 电路板 供电方面的相关问题。该相关问题包含: •选择各种DC-DC转换器为电路板供电 •电源供应排序/追踪 •电压监测 •上述全部 在本文中,电源管理被简单定义为:对电路板上的所有电源进行管理(包括DC-DC转换器及LDO等)。电源管理功能包含: •管理电路板上DC-DC控制器——例如热插拔、缓启动、排序、追踪、裕度和微调。 •产生所有电源供应相关状态和控制逻辑讯号——例如重置讯号产生、电源错误指示(监测)和电压管理。图1展示了一个采用CPU或微处理器电路板的典型电源管理功能。 图1:电路板上的典型电源管理功能。 热插拔/缓启动控制功能可用来限制突波电流以减少供应

[电源管理]

可编程逻辑器件APEX20K的原理及应用

摘要:介绍了Altera公司生产的多核架构可编程逻辑器件APEX20K系列芯片的主要特点和结构功能,给出了APEX20K内含的ClockLock以及ClockBoost电路的典型应用实例。

关键词:可编程逻辑器件 在系统设计 FPGA APEX20K

1 主要特点

APEX20K是Altera公司生产的首款带有多核架构的可编程逻辑器件,密度在30 000到1 500 000门,时钟速度高达822MHz。这种多核结构克服了必须用多个器件来实现系统级设计的麻烦,同时也节省了PCB板的空间。由于APEX20K具有功耗低、体积小、集成度高、速度快、费用低、用户可定义功能及可重复编程和擦写等许多优点,因此,可广泛应用于系统板级设计领

[应用]

小广播

热门活动

换一批

更多

最新测试测量文章

更多热门文章

更多每日新闻

- 柔灵科技陈涵:将小型、柔性的脑机接口睡眠设备,做到千家万户

- 微灵医疗李骁健:脑机接口技术正在开启意识与AI融合的新纪元

- USB Type-C® 和 USB Power Delivery:专为扩展功率范围和电池供电型系统而设计

- 景昱医疗耿东:脑机接口DBS治疗技术已实现国产替代

- 首都医科大学王长明:针对癫痫的数字疗法已进入使用阶段

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

- 新型IsoVu™ 隔离电流探头:为电流测量带来全新维度

- 英飞凌推出简化电机控制开发的ModusToolbox™电机套件

- 意法半导体IO-Link执行器电路板为工业监控和设备厂商带来一站式参考设计

更多往期活动

11月22日历史上的今天

厂商技术中心

模拟电子技术基础(第三版) (王远)

模拟电子技术基础(第三版) (王远)

京公网安备 11010802033920号

京公网安备 11010802033920号