频率合成技术是现代通信的重要组成部分,它是将一个高稳定度和高准确度的基准频率经过四则运算,产生同样稳定度和准确度的任意频率。频率合成器是电子系统的心脏,是影响电子系统性能的关键因素之一。本文结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,能够方便地应用于锁相环教学中,有一定的实用价值。

1 PLL频率合成器的基本原理

频率合成器主要有直接式、锁相式、直接数字式和混合式4种。目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

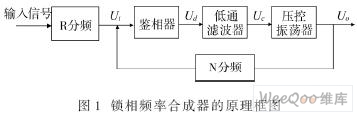

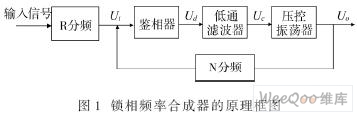

锁相频率合成器是由PLL构成的。一个典型的锁相频率合成器的原理框图如图1所示。

它的工作过程可以简单描述为:鉴相器输出电流的平均直流值乘以环路滤波器的阻抗,形成VCO的输入控制电压。VCO是一种电压—频率变换装置,具有一个比例常数。环路滤波器的控制电压调整了VCO的输出相位,除以N后,等于比较频率的相位。因为相位是频率的积分,所以这个过程同样适用于频率,输出频率可表示为:

公式1只有在PLL处于锁定状态下才成立,而在PLL重新调整到锁定状态的中间过程不成立。在实际应用中,R值是固定的,N值是可变的[2],XTAL为输入信号的频率。

2 系统设计

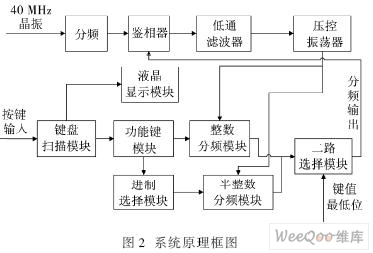

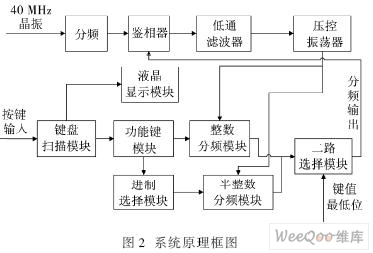

整个系统的功能主要由FPGA芯片EPF10K10 LC84-4控制相关硬件实现。本系统的原理框图如图2所示。

从图2可以看出,一方面,40 MHz有源晶振通过FPGA的控制进行分频,得到1 kHz的频率信号,作为CD4046的输入基准分频,CD4046的VCO的输出信号直接输入整数分频模块和半整数分频模块;另一方面,键盘扫描输出键值,键值送往功能模块。功能模块指示“确定”,那么键值作为分频系数,送到整数分频和半整数分频模块,分别对VCO输入的信号进行分频;功能模块指示“清除”,那么分频系数清零。键值的最后一位直接控制二路选择模块:键值的最后一位是“0”,控制二路选择模块输出整数模块结果;键值的最后一位是“5”,控制二路选择模块输出半整数模块结果。分频输出的结果与锁相环的基准频率在鉴相器中进行比较,产生一个对应于这两个信号相位差的Ud电压信号,再经过环路滤波器滤除Ud中的高频分量与噪声,输出Uc,Uc再输入VCO,使得压控振荡器的振荡频率不断向输入信号的频率靠拢,最后使得环路达到锁定,VCO输出稳定频率。

工作过程中,FPGA控制可预置的N/N+0.5的变化,当N/N+0.5变化时,输出信号频率响应跟着输入信号变化。同时FPGA也实现了键盘扫描与液晶显示的功能。

2.1 系统硬件设计

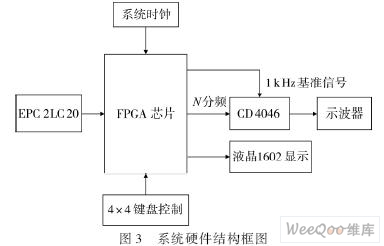

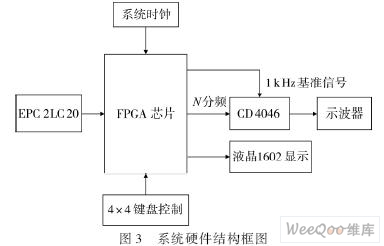

硬件上,如图3所示。该系统部分主要由7大部分组成:外部系统时钟、4×4键盘控制电路、FPGA处理芯片、EPC2LC20型EPROM芯片、PLL芯片CD4046及其外围电路、液晶1602显示模块、示波器。本设计使用FPGA专用配置芯片EPC2,通过下载电缆ByteBlaster MV,把程序多次下载到FPGA芯片中。系统使用FPGA芯片作为控制中心,按键扫描输入控制信息,液晶屏进行显示,能够方便直观地演示PLL芯片CD4046在频率合成技术中的应用,且达到了预期的指标要求。本设计中的主要硬件的具体型号是:液晶TC1602A-01T,FPGA芯片EPF10K10LC84-4,40.000 MHz有源晶振HO-12B。

2.2 系统软件设计

通过编写VHDL程序实现整数/半整数分频,并应用Quartus II和ModelSim,笔者完成了VHDL程序的设计及仿真。

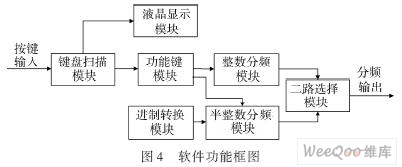

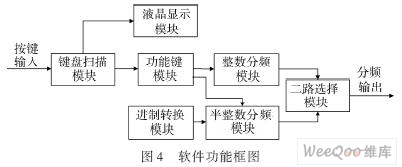

系统软件功能框图如图4所示。 [page]

系统的具体工作过程如下:

键盘扫描模块负责扫描按键,输出键值,键值输入到1602液晶模块中进行显示。同时,通过功能键模块去控制键值输入到FPGA中的分频模块中,功能模块为“确定”时,键值输入到FPGA分频模块中,分频系数N就等于输入的键值。功能模块为“清除”时,FPGA分频模块中,分频系数N就会被清零。

3 系统测试及结果

测试仪器:INSTEK GOS-620(20 MHz模拟示波器)

测试温度:室温

3.1 检测系统是否入锁

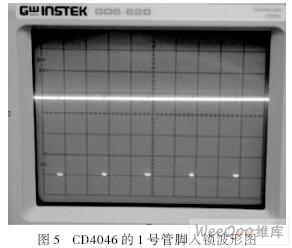

键盘输入从1~999.5时,所测CD4046的1号管脚波形如图5所示,指示PLL处于入锁状态。

3.2 检测较低频的整数/半整数分频

当N=3、9、13、1.5、5.5、9.5,输入为1 kHz的频率时,CD4046的输出波形分别如图6(a)、(b)、(c)、(e)、(f)、(g)所示。从图中可以很明显地读到,输出分别为3 kHz、9 kHz、13 kHz、1.5 kHz、5.5 kHz和9.5 kHz。这与理论上预见的结果是一致的。

3.3 检测较高频的整数/半整数分频

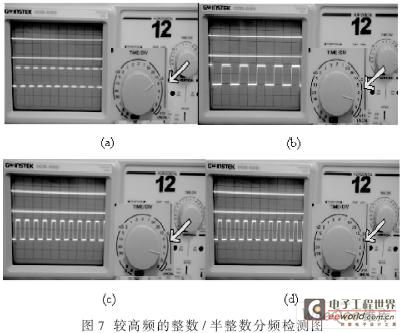

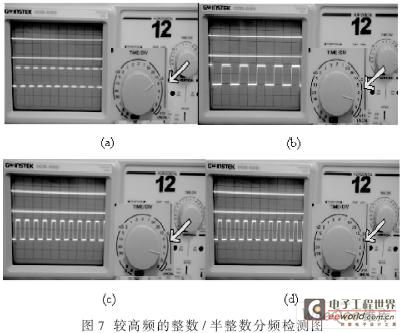

当N为更高的数值时,通过比较CD4046的输入输出波形,很难直接看出来。这时输入仍采用1kHz的频率值,这时直接看输出的频率值。N=100、500、999、999.5时的波形分别如图7(a)、(b)、(c)、(d)所示。

由图7(a)得:所测频率为1/(10×10-6)Hz=100 kHz

由图7(b)得:所测频率为2/(10×10-6)Hz=500 kHz

由图7(c)得:所测频率约为1/(10×10-6)Hz=1 MHz

由图7(d)得:所测频率约为1/(10×10-6)Hz=1 MHz

可见,这时实测值与理论上预见的结果也是一致的。

3.4 误差分析

较低频时的波形之所以占空比不是标准的50%,是由于CD4046输出频率经过FPGA分频模块之后产生的反馈信号只是一个脉冲信号,这个脉冲信号要与出入CD4046的1kHz的标准信号进行相位比较,而标准信号的占空比是50%,这就造成了相位比较之后产生的信号波形占空比不是50%,而本系统测试时所采用的是模拟示波器,对较低频占空比非50%的显示不是很好,这很有可能是由于波形不是非常标准的主要原因。

在测试完成之后,又用数字示波器来专门检测CD4046的输出频率,结果与理论计算几乎吻合。

本系统结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,输出范围为1 kHz~999.5 kHz,步进频率可达到0.5 kHz;与以前的实验装置相比,系统在性能指标、直观性等方面都有所提高,它不仅可以用于教学实验,还可以用作频率源、频率计。

关键字:FPGA PLL 频率合成器

引用地址:基于FPGA的PLL频率合成器设计

1 PLL频率合成器的基本原理

频率合成器主要有直接式、锁相式、直接数字式和混合式4种。目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

锁相频率合成器是由PLL构成的。一个典型的锁相频率合成器的原理框图如图1所示。

它的工作过程可以简单描述为:鉴相器输出电流的平均直流值乘以环路滤波器的阻抗,形成VCO的输入控制电压。VCO是一种电压—频率变换装置,具有一个比例常数。环路滤波器的控制电压调整了VCO的输出相位,除以N后,等于比较频率的相位。因为相位是频率的积分,所以这个过程同样适用于频率,输出频率可表示为:

公式1只有在PLL处于锁定状态下才成立,而在PLL重新调整到锁定状态的中间过程不成立。在实际应用中,R值是固定的,N值是可变的[2],XTAL为输入信号的频率。

2 系统设计

整个系统的功能主要由FPGA芯片EPF10K10 LC84-4控制相关硬件实现。本系统的原理框图如图2所示。

从图2可以看出,一方面,40 MHz有源晶振通过FPGA的控制进行分频,得到1 kHz的频率信号,作为CD4046的输入基准分频,CD4046的VCO的输出信号直接输入整数分频模块和半整数分频模块;另一方面,键盘扫描输出键值,键值送往功能模块。功能模块指示“确定”,那么键值作为分频系数,送到整数分频和半整数分频模块,分别对VCO输入的信号进行分频;功能模块指示“清除”,那么分频系数清零。键值的最后一位直接控制二路选择模块:键值的最后一位是“0”,控制二路选择模块输出整数模块结果;键值的最后一位是“5”,控制二路选择模块输出半整数模块结果。分频输出的结果与锁相环的基准频率在鉴相器中进行比较,产生一个对应于这两个信号相位差的Ud电压信号,再经过环路滤波器滤除Ud中的高频分量与噪声,输出Uc,Uc再输入VCO,使得压控振荡器的振荡频率不断向输入信号的频率靠拢,最后使得环路达到锁定,VCO输出稳定频率。

工作过程中,FPGA控制可预置的N/N+0.5的变化,当N/N+0.5变化时,输出信号频率响应跟着输入信号变化。同时FPGA也实现了键盘扫描与液晶显示的功能。

2.1 系统硬件设计

硬件上,如图3所示。该系统部分主要由7大部分组成:外部系统时钟、4×4键盘控制电路、FPGA处理芯片、EPC2LC20型EPROM芯片、PLL芯片CD4046及其外围电路、液晶1602显示模块、示波器。本设计使用FPGA专用配置芯片EPC2,通过下载电缆ByteBlaster MV,把程序多次下载到FPGA芯片中。系统使用FPGA芯片作为控制中心,按键扫描输入控制信息,液晶屏进行显示,能够方便直观地演示PLL芯片CD4046在频率合成技术中的应用,且达到了预期的指标要求。本设计中的主要硬件的具体型号是:液晶TC1602A-01T,FPGA芯片EPF10K10LC84-4,40.000 MHz有源晶振HO-12B。

2.2 系统软件设计

通过编写VHDL程序实现整数/半整数分频,并应用Quartus II和ModelSim,笔者完成了VHDL程序的设计及仿真。

系统软件功能框图如图4所示。 [page]

系统的具体工作过程如下:

键盘扫描模块负责扫描按键,输出键值,键值输入到1602液晶模块中进行显示。同时,通过功能键模块去控制键值输入到FPGA中的分频模块中,功能模块为“确定”时,键值输入到FPGA分频模块中,分频系数N就等于输入的键值。功能模块为“清除”时,FPGA分频模块中,分频系数N就会被清零。

3 系统测试及结果

测试仪器:INSTEK GOS-620(20 MHz模拟示波器)

测试温度:室温

3.1 检测系统是否入锁

键盘输入从1~999.5时,所测CD4046的1号管脚波形如图5所示,指示PLL处于入锁状态。

3.2 检测较低频的整数/半整数分频

当N=3、9、13、1.5、5.5、9.5,输入为1 kHz的频率时,CD4046的输出波形分别如图6(a)、(b)、(c)、(e)、(f)、(g)所示。从图中可以很明显地读到,输出分别为3 kHz、9 kHz、13 kHz、1.5 kHz、5.5 kHz和9.5 kHz。这与理论上预见的结果是一致的。

3.3 检测较高频的整数/半整数分频

当N为更高的数值时,通过比较CD4046的输入输出波形,很难直接看出来。这时输入仍采用1kHz的频率值,这时直接看输出的频率值。N=100、500、999、999.5时的波形分别如图7(a)、(b)、(c)、(d)所示。

由图7(a)得:所测频率为1/(10×10-6)Hz=100 kHz

由图7(b)得:所测频率为2/(10×10-6)Hz=500 kHz

由图7(c)得:所测频率约为1/(10×10-6)Hz=1 MHz

由图7(d)得:所测频率约为1/(10×10-6)Hz=1 MHz

可见,这时实测值与理论上预见的结果也是一致的。

3.4 误差分析

较低频时的波形之所以占空比不是标准的50%,是由于CD4046输出频率经过FPGA分频模块之后产生的反馈信号只是一个脉冲信号,这个脉冲信号要与出入CD4046的1kHz的标准信号进行相位比较,而标准信号的占空比是50%,这就造成了相位比较之后产生的信号波形占空比不是50%,而本系统测试时所采用的是模拟示波器,对较低频占空比非50%的显示不是很好,这很有可能是由于波形不是非常标准的主要原因。

在测试完成之后,又用数字示波器来专门检测CD4046的输出频率,结果与理论计算几乎吻合。

本系统结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,输出范围为1 kHz~999.5 kHz,步进频率可达到0.5 kHz;与以前的实验装置相比,系统在性能指标、直观性等方面都有所提高,它不仅可以用于教学实验,还可以用作频率源、频率计。

上一篇:一种宽输入范围高精度频率计的设计

下一篇:16位微处理器L80C186-10测试技术研究

推荐阅读最新更新时间:2024-03-30 22:54

用PowerPC860实现FPGA配置

摘要:介绍如何用PowerPC860(MPC860)进行FPGA(Xilinx的Virtex-II系列)的配置;给出进行FPGA配置所需的详细时序图和原理图。本配置基本原理对其它FPGA的配置也适用。 关键词:PowerPC860 FPGA Xilinx 1 概述 MPC860是基于PowerPC结构的通信控制器。它不仅是集成的微处理器,而且将很多外设的功能也集成在一起。MPC860具有存储控制器,其存储控制器的功能很强,可以支持各种存储器,包括各种新型的DRAM和Flash,并可以实现与存储器的无缝接口;而且使用嵌入式操作系统VxWorks和开发环境Tornado开发非常方便。 本设计中用1片Intel W28F1283A150

[半导体设计/制造]

开放式FPGA增加测试灵活性

现在的大多数仪器通过将封闭式FPGA与固定固件相结合来实现仪器的各种功能。如果您看过一个拆解后的示波器,您可能已经看过里面的FPGA.FPGA提高了测试仪器的处理能力,而且如果您会使用仪器中的开放式FPGA,就可以自己编写仪器的测试功能。 仪器厂商早就认识到FPGA的优势,而且也利用其独特的处理能力来实现仪器的各种特性: *在示波器上进行预触发采集 *在矢量信号分析仪上通过信号处理生成I和Q数据 *实时实现模式生成和高速数字仪器的向量比较 测试设备制造商正在致力于帮助用户更好地利用FPGA,以针对更多的特定应用进行优化。为了帮助您理解这一转变的好处,以下几点是FPGA特别适用于测试应用的关键属性: *确定实时的处理 *真正的并行执

[测试测量]

国内FPGA厂商 智多晶完成了亿元C轮融资

9月,西安智多晶微电子有限公司(以下简称“智多晶”)完成亿元C轮融资,盛宇投资旗下人工智能产业基金参投,本轮其他投资方包括超越摩尔基金、临芯投资、深创投等机构。 智多晶成立于2012年,是一家FPGA芯片供应商,总部位于西安,创始团队拥有丰富的FPGA设计制造经验,曾就职于海外该领域领先企业,并担任多个专业方向技术带头人。 FPGA行业高度集中,且技术壁垒较高,但目前中国仍然有多家企业发力布局,智多晶凭借其技术实力,在FPGA市场“崭露头角”。 今年1月,智多晶董事长贾红在接受集微网记者采访时表示,目前智多晶拥有四条产品线,分别为162nm CPLD 产品线、55nm内嵌Flash小容量FPGA 产品、55nm中等逻辑量FPGA

[手机便携]

基于FPGA+DSP技术的Bayer格式图像预处理

高分辨率图像实时处理在通信、医学、军事、航天航空、信息安全等领域有着广泛的应用和发展。在图像实时处理的过程中,下层图像预处理的数据量大,运算简单,但是要求运算速率高,可以用FPGA硬件来处理,上层所处理的数据量少,算法结构复杂,适于运算速度快,寻址灵活的DSP数字信号处理器进行处理。这里提出了一种FPGA+DSP相结合的实时图像处理系统,并应用于传像光线束传递图像。CMOS实际采集的是光线束的出端图像,FPGA将CMOS采集的Bayer格式的图像转换为RGB格式的亮度信号。由于光纤出、入端结构不同,需要DSP准确每根光纤的中心位置,重新排序才能输出正确的图像信息。该系统充分发挥了FPGA和DSP各自的优势,能更好地提高图像处理的实

[嵌入式]

一种基于FPGA的CAN总线通信接口的设计

CAN总线是现场总线的一种,因为其成本低、容错能力强、支持分布式控制、通信速率高等优点在汽车、工业控制、航天等领域得到广泛应用。但是计算机没有CAN总线接口,为了进行CAN总线的调试,必须具有专用的适配卡才能实现与计算机的通信。目前常用的CAN转换器是基于单片机设计的,一般只适用于单路CAN总线的数据转换,可扩展性差。 在小卫星相机下位机系统中使用了多种总线,如CAN总线与卫星管理计算机的通信;RS422(或RS485)总线与成像单元等下行单元的通信。在进行相机下位机系统地面调试时,可能需要多种总线转换器。采用FPGA将不同总线协议转换成USB2.0、RS232等可与计算机直接交换数据的协议,可增强设计的灵活性,降低设计

[嵌入式]

Actel在硅谷嵌入式大会演示 SmartFusion FPGA

爱特公司(Actel Corporation) 于2010年4月26-29日举行的硅谷嵌入式系统大会(Embedded Systems Conference, ESC)上现场演示如何通过使用智能型混合信号FPGA器件SmartFusion™,为高复杂性马达和运动控制应用带来引人注目的解决方案。SmartFusion集成有32位ARM® Cortex™-M3微控制器、可编程模拟资源、片上嵌入式非易失存储器(eNVM),以及经过验证的低功耗快闪FPGA架构,能够直接应对马达控制设计的挑战。 现今马达朝向更小体积和更强功能两方面发展,加上高能电池领域的技术创新,开创了多种马达控制产品的新市场。用于交流和直流马达控制的新设计

[嵌入式]

推出logiCRAFT3小型多媒体显示平台

赛灵思公司 推出 logiCRAFT3 小型多媒体显示开发平台。该平台基于赛灵思公司满足汽车应用标准的低成本 Xilinx® XA Spartan™-3E 系列 现场可编程门阵列器件。与汽车市场开发系统和 IP 产品主要供应商 Xylon 公司合作开发的这一优势平台提供了更大的灵活性和可扩展能力,使得模块设计人员可以在更为广泛的车内显示系统中采用赛灵思 XA 可编程器件。 目前,车内使用的显示屏数量快速增加,例如用于导航、中控面板以及后座娱乐( RSE )系统。此外,混合显示等应用的出现也进一步刺激了市场增长以及对小型快速开发平台的需求。混合显示应用综合了模拟显示、 LCD/TFT

[嵌入式]

采用FPGA数字显示解决方案降低系统成本

如今数字显示设备中引起成本变化的主要因素是显示屏。在设计阶段,不断推进基于平台的显示设计的决策可以大大减少采购成本。如果能支持多种显示屏尺寸,原始设备制造商(OEM)能从一个供应商那里得到较大的折扣。为了支持多种显示屏供应商的规范,OEM可以创建竞争形势以得到较低的价格。这两种方案节省的开支大于由于需要额外的器件而引起价格的上升,例如能实现基于平台设计的FPGA。此外,多个供应商的支持降低了连续供给的风险。 基于平台的显示设计的一些考虑 为了采用基于平台的方法获取最佳的成本节省和灵活性,系统设计者为系统挑选器件时须遵循下列准则:不同地方的对图形处理器的要求不同,可编程特性支持全球的多种标准和格式,加速终端

[嵌入式]

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著)

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著) 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号