实现信号源常用的方法是频率合成法,其中直接数字频率合成法是继直接频率合成法和间接频率合成法之后,随着电子技术迅速发展的第三代频率合成技术。DDS是一种全数字技术,它从相位概念出发直接合成所需频率,它具有频率转换时间短,频率分辨率高,相位变化连续,低相位噪声和低漂移,易于集成、调整、实现正交输出等优点。近年来,DDS技术在频率合成、通信、雷达、电子对抗、仪器测试等领域均有广泛的应用。目前专用的DDS芯片产生的信号波形、功能和控制方式固定,常不能满足具体需要。现场可编程门阵列(FPGA)器件具有规模大、工作速度快及可编程的硬件特点,并且开发周期短,易于升级,因此非常适用于实现DDS。

1 DDS的基本原理

DDS的结构由相位累加器,相位调制器,波形存储ROM和D/A转换器组成,是Tierney,Rader和Gold于1971年提出。一个正弦信号发成器结构图如图1所示。相位累加器是整个DDS的核心,完成相位累加运算,它输入的是相位增量B△θ。相位累加器每溢出一次,就代表输出ROM内的一个完整波形。相位调制器接收相位累加器的相位输出。加上一个相位偏移量,用于信号的相位调制。正弦ROM查找表完成相位到幅度的转换,它的输入是相位调制器的输出,也就是ROM的地址。

2 DDS精度改进方案

ROM查找表实际上是一个存储了正弦信号抽样点幅度编码的只读存储器,将输入的序列转换为正弦信号的幅度编码。ROM查找表地址位数M越靠近相位累加器的位数N,相位寻址时舍去的位数就越小,相位舍位误差也就越小,但ROM表的大小会随地址位数M的增加成指数递增关系。因此,为了使用较小的ROM而满足信号性能,必须采用优化方法压缩ROM。

2.1 正弦波特点

已知正弦波存在下面的关系:

2.2 基于DSP Builder的ROM优化方案

从上面对正弦波特点的分析可得出,查找表ROM中只存储[O,π]或[0,π/2]区间的波形就可得完整周期的正弦信号。这样就有效地利用了ROM存储完间,提高了存储效率。对于ROM中存储[O,π]区间波形的情况,可以利用相位调制器输出的最高位作为符号位,将正弦波合成到[0,2π]区间。而对于ROM中存储[0,π/2]区间波形的情形,利用相位调制器输出的次高位判断象限,将正弦波合成到[O,π]区间;最高位作为符号位,将正弦波合成到[0,2π]区间。图2给出了ROM中存储[O,2π],[0,π],[O,π/2]区间波形时,用DSP Builder实现正弦信号发生器的系统模型。

2.3 仿真分析

图3给出了图2系统模型中3个输出OUTl,OUT2,OUT3的波形。由图3可见,OUT2的频率是OUTl的1/2,而OUT3的频率是OUT2的1/2。这表明,OUT3的频率分辨率最高,0UT2次之,OUTl最低。由此可得出,有着相同地址输入的ROM,在存储空间大小相同情况下,存储正弦波区间越小,输出正弦信号的频率分辨率越高,即输出精度越高。所以,用相同的ROM,当存储1/4周期正弦信号时,合成的正弦信号有着较高的精度。 [page]

Matlab/Simulink对设计好的DDS系统进行编译,通过调用DSP Builder的SignalCompiler工具可直接生成QuartusⅡ的工程文件,再调用QuartusⅡ完成综合、网表生成和适配,直至完成FPGA的配置下载过程。

本设计方案采用的FPGA芯片是APEX20K系列器件EP20K200FC484。所得结果中的数字输出可以输出到SRAM芯片中,然后上载到计算机进行数字信号分析,模拟输出则通过HP示波器测试。图4给出了用QuartusII的仿真结果。图中,clock为系统时钟,sclrp为高电平复位信号,PWORD,FWORD,AWORD的值分别设为十进制数0,9000000和50。仿真得到的3个输出OUTl,OUT2和OUT3与Matlab/Simulink中的仿真结果在相位、频率和幅度上基本一致。实验表明,利用FPGA所计设的DDS在满足性能的条件下,节约了芯片资源,提高了输出的精度。

本文介绍了一种改进了的基于DSP Builder的正弦信号发生器设计方法,应用APEX20K系列FPGA芯片实现。继承了传统DDS设计中调频、调相迅速的优点,同时,采用了查找表压缩方案,使芯片在节约资源的基础上达到了较高的输出精度。

关键字:信号源 正弦信号 DSP FPGA

引用地址:基于DSP Builder的正弦信号源优化设计及其FPGA实现

1 DDS的基本原理

DDS的结构由相位累加器,相位调制器,波形存储ROM和D/A转换器组成,是Tierney,Rader和Gold于1971年提出。一个正弦信号发成器结构图如图1所示。相位累加器是整个DDS的核心,完成相位累加运算,它输入的是相位增量B△θ。相位累加器每溢出一次,就代表输出ROM内的一个完整波形。相位调制器接收相位累加器的相位输出。加上一个相位偏移量,用于信号的相位调制。正弦ROM查找表完成相位到幅度的转换,它的输入是相位调制器的输出,也就是ROM的地址。

2 DDS精度改进方案

ROM查找表实际上是一个存储了正弦信号抽样点幅度编码的只读存储器,将输入的序列转换为正弦信号的幅度编码。ROM查找表地址位数M越靠近相位累加器的位数N,相位寻址时舍去的位数就越小,相位舍位误差也就越小,但ROM表的大小会随地址位数M的增加成指数递增关系。因此,为了使用较小的ROM而满足信号性能,必须采用优化方法压缩ROM。

2.1 正弦波特点

已知正弦波存在下面的关系:

2.2 基于DSP Builder的ROM优化方案

从上面对正弦波特点的分析可得出,查找表ROM中只存储[O,π]或[0,π/2]区间的波形就可得完整周期的正弦信号。这样就有效地利用了ROM存储完间,提高了存储效率。对于ROM中存储[O,π]区间波形的情况,可以利用相位调制器输出的最高位作为符号位,将正弦波合成到[0,2π]区间。而对于ROM中存储[0,π/2]区间波形的情形,利用相位调制器输出的次高位判断象限,将正弦波合成到[O,π]区间;最高位作为符号位,将正弦波合成到[0,2π]区间。图2给出了ROM中存储[O,2π],[0,π],[O,π/2]区间波形时,用DSP Builder实现正弦信号发生器的系统模型。

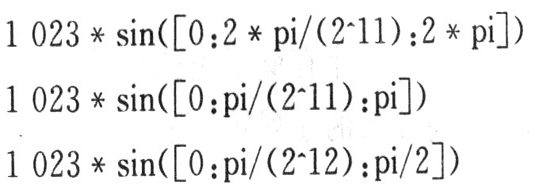

其中,PWORD为相位字输入,其值设置为O;FWORD为频率字输入,其值设置为9000000;AWORD为幅度控制输入,其值设置为50;adder为相位累加器;adderl为相位调制器。LUTl,LUT2,LUT3分别为存储[O,2 π],[O,π],[0,π/2]区间正弦信号的具有相同存储空间的ROM,它们模块参数“MATLAB Array”分别设置为:

2.3 仿真分析

图3给出了图2系统模型中3个输出OUTl,OUT2,OUT3的波形。由图3可见,OUT2的频率是OUTl的1/2,而OUT3的频率是OUT2的1/2。这表明,OUT3的频率分辨率最高,0UT2次之,OUTl最低。由此可得出,有着相同地址输入的ROM,在存储空间大小相同情况下,存储正弦波区间越小,输出正弦信号的频率分辨率越高,即输出精度越高。所以,用相同的ROM,当存储1/4周期正弦信号时,合成的正弦信号有着较高的精度。 [page]

Matlab/Simulink对设计好的DDS系统进行编译,通过调用DSP Builder的SignalCompiler工具可直接生成QuartusⅡ的工程文件,再调用QuartusⅡ完成综合、网表生成和适配,直至完成FPGA的配置下载过程。

本设计方案采用的FPGA芯片是APEX20K系列器件EP20K200FC484。所得结果中的数字输出可以输出到SRAM芯片中,然后上载到计算机进行数字信号分析,模拟输出则通过HP示波器测试。图4给出了用QuartusII的仿真结果。图中,clock为系统时钟,sclrp为高电平复位信号,PWORD,FWORD,AWORD的值分别设为十进制数0,9000000和50。仿真得到的3个输出OUTl,OUT2和OUT3与Matlab/Simulink中的仿真结果在相位、频率和幅度上基本一致。实验表明,利用FPGA所计设的DDS在满足性能的条件下,节约了芯片资源,提高了输出的精度。

本文介绍了一种改进了的基于DSP Builder的正弦信号发生器设计方法,应用APEX20K系列FPGA芯片实现。继承了传统DDS设计中调频、调相迅速的优点,同时,采用了查找表压缩方案,使芯片在节约资源的基础上达到了较高的输出精度。

上一篇:频谱分析基本原理:快速完成高效率测量

下一篇:基于FPGA和DDS的信号源设计

推荐阅读最新更新时间:2024-03-30 23:01

采用DSP的谐波控制器的设计方案

当今电力系统中的电能质量问题越来越突出,一方面,大量敏感性负荷对电能质量的要求越来越高,而另一方面,越来越多的非线性负荷不断接入电网,使电力系统总体的电能质量状况不断恶化。 谐波是电能质量中很重要的一个方面,谐波的存在对电力系统产生的危害有以下几个方面: 1)可能使电力系统继电保护装置和自动装置产生误动或拒动; 2)使各种电气设备产生附加损耗和发热,使电机产生机械振动及噪声; 3)谐波电流在电网中流动增加损耗,影响电网及各种电气设备的经济运行; 4)谐波电流通过电磁感应、电容耦合以及电气传导等作用,对周围的通信系统产生干扰; 5)谐波使电网中广泛使用的各种测量仪表产生误差; 6)增加了

[嵌入式]

基于FPGA的高速FIR数字滤波器的设计

1 引 言 目前FIR滤波器的实现方法主要有3种:利用单片通用数字滤波器集成电路、DSP器件和可编程逻辑器件实现。单片通用数字滤波器使用方便,但由于字长和阶数的规格较少,不能完全满足实际需要。使用DSP器件实现虽然简单,但由于程序顺序执行,执行速度必然不快。 FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好。但长期以来,FPGA一直被用于系统逻辑或时序控制上,很少有信号处理方面的应用,其原因主要是因为在FPGA中缺乏实现乘法运算的有效结构。本文利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器,使FPGA在数字信号处理方面有

[应用]

京微雅格发布“云”系列首颗两千万门级FPGA芯片CME-C1

2016年1月19日 北京讯--京微雅格(北京)科技有限公司今日召开 国家科技重大专项核高基项目首颗高性能FPGA芯片暨京微雅格CME-C1(祥云)系列新品发布会 ,宣布其面向大容量FPGA市场的 云 系列首款FPGA芯片,CME-C1(祥云)正式发布。武汉虹信通信技术有限公司、普天信息技术研究院、辽宁聚龙金融设备股份有限公司等产业代表,媒体代表近百名嘉宾出席了此次发布活动。 CME-C1采用了TSMC 40nm CMOS工艺,逻辑容量从30K 200K不等。该系列产品使用了全新的LUT 6架构和32路全时钟网络,运行速度可达到700MHz。此外,针对高速大容量市场的应用需求,CME-C1还整合了高速Serdes接

[嵌入式]

40亿美元市场保持8年没变,可编程逻辑FPGA到底怎么了

FPGA 市场在2008年是40亿美元规模,到了2016年还是40亿美元。似乎显而易见,当 ASIC 越来越贵,可编程应该要增长才对。然而事实并非如此。下面就随嵌入式小编一起来了解一下相关内容吧。 在1996年 FPGA 市场容量为19亿美元,当年赛灵思预测到2001年市场能达到58亿美元。到了2001年,市场增长到20亿美元。 回到2008年,赛灵思的帅印由WimRoelandts交接给MosheGavrielov,该公司开始寻求在工业市场的新出路,这块市场一直被寄予厚望却从未实现预期的增长。 “过去四年里ASSP/ ASIC 的设计型初创公司减少了40%,”在2008年4月Gavrielov如是说,“为什么

[嵌入式]

Altera设计解决方案满足FPGA架构的设计创新

Altera宣布启动其设计解决方案网路(DSN),此一全球辅助支援系统将稳健的设计服务网路、IP、电路板和商用现有产品(COTS)等公司统一合并到一个计画之中。该计画连接客户与网路成员,透过统一的搜寻网站,提供Altera CPLD、FPGA、SoC和Enpirion电源元件相关的产品或者设计服务,协助客户加速产品创新。 该公司的DSN成员能方便的使用最新的开发工具、软体、IP和技术支援,进而加速客户FPGA和嵌入式设计以及产品开发。为确保技术水准,将要求DSN成员完成技术培训。该计画根据受过Altera培训的DSN成员的专业水准和成就,而将其评为白金或者黄金级成员。 该计画将包括由五十五个国家和地区的一百八十多家公

[嵌入式]

Tensilica将于CES 2013上展示采用了Waves的MaxxAudio®音效增强技术的HiFi音频 DSP内核

美国内华达州拉斯维加斯国际消费电子展(CES) 2013年1月8日–Tensilica今日宣布,Waves消费电子部门(LVH 1430),业界领先的专业音频数字信号处理及格莱美®技术奖的获得者,与Tensilica(拉斯维加斯会议中心南厅2,展厅号为MP25060),业界领先的数据处理器IP核授权商达成新的合作关系。Tensilica的HiFi音频DSP内核现可采用Waves的MaxxAudio®音效增强技术。Tensilica的HiFi DSP内核是业界领先的音频平台,广泛应用于消费类电子产品,包括便携式音乐播放器、智能手机、电脑、平板电脑、数字电视以及其他相关设备。 MaxxAudio采用了大量获得专利的信号处理技术,通过

[嵌入式]

一种基于DSP的中文语音合成系统设计

0 引言 随着语音信号处理技术的不断发展与成熟,语音合成正逐步成为信息技术中人机接口的关键技术。DSP芯片,即数字信号处理器,是专门为快速实现各种信号处理算法而设计的、具有特殊结构的微处理器,其处理速度比最快的CPU还快10~50倍。本文介绍的就是一种基于DSP的中文语音合成系统的实现方法。 1 系统总体方案 语音合成的最大特点就是要从有限的存储单元中合成出无限字汇的连续语句来 。为了做到这一点,本系统设计了由(1)前端预处理模块将输入文本文件转换成系统可以处理的标准格式;(2)韵律规则库给出当前语言环境下各个音节的韵律特征参数;(3)语音合成器根据给定的韵律特征参数对原始语音库中相应语音单元的声学参数进行调整;(4)将经过

[嵌入式]

基于DSP的雷达视频信号数字采集与检测

引 言 反应速度更快、精度更高、目标的自动录取、使操作员能够同时处理多批目标,是现代雷达所追求的技术指标。雷达视频信号的数字采集和检测是达成这样目标的前提条件。众所周知,雷达对目标位置的测量,主要是依据目标回波相对于发射电波的延迟时间以及雷达天线的方向来决定的。电波的传播速度极快,传播l海里的时间大约只有12.35μs,雷达发射电波的间隔一般在ms数量级。在此间隔时间内,理论上最多会有成百上千个目标的回波。要在如此短的时间之内,对这么多的目标回波信号进行数字采集和处理,快速的采集器件及高速计算机处理器必不可少。DSP(Digital Signal Processor)芯片,即数字信号处理器,就是这样一种特别适用于进行这

[嵌入式]

模拟电子技术基础(第3版) (赵进全,杨拴科)

模拟电子技术基础(第3版) (赵进全,杨拴科) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号