引言

随着人们对实时信号处理要求的不断提高和大规模集成电路的迅速发展,作为数字信号处理核心和标志的数字信号处理器DSP芯片得到了快速的发展和应用。它不但可以广泛应用于通信系统、图形/图像处理、雷达声纳、医学信号处理等实时信号处理领域。就ADI公司而言,继16-bit定点ADSP21xx和32-bit浮点ADSP21xxx系列之后,日前又推出了TigerSHARC系列的新型器件。本文介绍使用该系列中的ADSP-TS201S芯片实现一个图像采集处理系统的设计方案。

系统总体方案

该系统可以完成图像的采集、处理和显示,从而实现目标识别与跟踪的智能信号处理。该系统是对摄像机数字,模拟两路视频数据进行采集,处理后通过PCI总线在PC机上显示出来。整个系统主要由视频信号采集模块、DSP图像处理模块、PCI接口模块三个部分组成(图1)。

图1 图像采集处理系统框图系统的各个功能模块电路设计

%26;#183;视频信号采集模块

摄像机提供两路视频信号:一路模拟视频,一路数字视频。

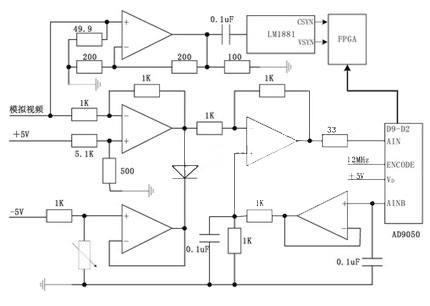

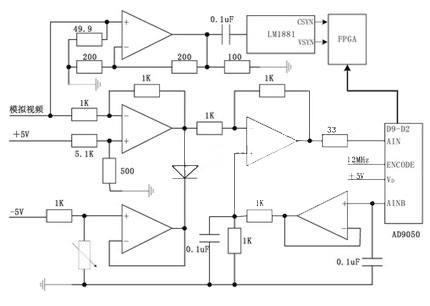

模拟视频信号经过钳位校正、放大后,将信号送入到A/D转换器,再经FPGA锁存后将视频信号发送给DSP1;经视频同步分离电路,由LM1881分离出模拟视频的行、场同步信号,用于控制视频数据采集到DSP1,以便进行图像处理。钳位校正、视频同步电路如图2所示。模拟视频经运放输入,将中心电平调到3.3V,加到A/D输入端。A/D转换后的数据进入FPGA锁存。运放均采用ADI公司的AD8047AR,A/D转换器采用ADI公司的AD9050。AD9050为10位A/D转换器,取其高8位进入FPGA。采样时钟12MHz,与数字视频信号相同。由FPGA对48MHz时钟四分频产生。

图1 图像采集处理系统框图系统的各个功能模块电路设计

%26;#183;视频信号采集模块

摄像机提供两路视频信号:一路模拟视频,一路数字视频。

模拟视频信号经过钳位校正、放大后,将信号送入到A/D转换器,再经FPGA锁存后将视频信号发送给DSP1;经视频同步分离电路,由LM1881分离出模拟视频的行、场同步信号,用于控制视频数据采集到DSP1,以便进行图像处理。钳位校正、视频同步电路如图2所示。模拟视频经运放输入,将中心电平调到3.3V,加到A/D输入端。A/D转换后的数据进入FPGA锁存。运放均采用ADI公司的AD8047AR,A/D转换器采用ADI公司的AD9050。AD9050为10位A/D转换器,取其高8位进入FPGA。采样时钟12MHz,与数字视频信号相同。由FPGA对48MHz时钟四分频产生。

图2 模拟视频输入转换电路

摄像机的数字视频信号为14对差分信号,经FPGA将差分信号转换为单端信号,并锁存数据。每个象素14位,每帧320%26;#215;240。

FPGA采用ALTERA公司的CYCLONE系列EP1C3T144C-6,配置芯片采用EPC2LC20。EP1C3T144C-6具有将差分信号转单端信号的专用I/O口。锁存在FPGA的数字,模拟两路视频信号根据工作模式选择输出到DSP1数据总线上,由DSP1读入处理,数据速率与模拟视频的采样速率,数字视频的数据速率相同。工作模式选择,开关控制通过PIC9054引入到FPGA。

%26;#183;DSP处理器模块

DSP处理器阵列模块主要由4片高速高性能的DSP处理芯片ADSP-TS201S组成多DSP处理器系统,ADSP-TS201S性能如下:

基本性能指标如下:

600MHz运行速度时,内核指令周期1.67ns

24M bits片上DRAM,分为6个4M bits块(128K words X 32 bits)

片内双运算模块,每个都包含一个ALU、一个乘法器、一个移位器和一个寄存器组

双整数ALU提供数据寻址和指针操作功能

片内提供14通道DMA、外部口、4个链路口、SDRAM控制器、可编程标志引脚、2个定时器

片上仲裁系统可实现8个TigerSHARC DSP的无缝连接

内部3条互相独立的128位总线

外部数据总线64位,地址总线32位

每秒48亿次40位宽的MAC运算或每秒12亿次80位宽的MAC运算;1024点复数FFT(基2)时间15.7us

外部端口 1G字节每秒;链路口(每个)1G字节每秒

DSP处理器阵列模块中DSP1是用来整理所收集到的视频信号,并进行相应的预处理后,将数据分发送到后面的DSP,进行进一步的处理。

DSP1并行口应接FPGA输出的视频数据,还要接FLASH,完成DSP加载。DSP1的IRQ0,IRQ1分别作视频输入的帧中断和行中断,接到FPGA。其连接电路如下图3所示。

FLASH选用AMD公司的AM29LV017D,为2M x 8-Bit的存储器,可通过DSP1对FLASH编程,要保证在FLASH读写时,FPGA的数据输出总线D0~D13为高阻,反之,在数据通道运行时,也应使FLASH输出为高阻,故用BMS来选片FLASH。

图2 模拟视频输入转换电路

摄像机的数字视频信号为14对差分信号,经FPGA将差分信号转换为单端信号,并锁存数据。每个象素14位,每帧320%26;#215;240。

FPGA采用ALTERA公司的CYCLONE系列EP1C3T144C-6,配置芯片采用EPC2LC20。EP1C3T144C-6具有将差分信号转单端信号的专用I/O口。锁存在FPGA的数字,模拟两路视频信号根据工作模式选择输出到DSP1数据总线上,由DSP1读入处理,数据速率与模拟视频的采样速率,数字视频的数据速率相同。工作模式选择,开关控制通过PIC9054引入到FPGA。

%26;#183;DSP处理器模块

DSP处理器阵列模块主要由4片高速高性能的DSP处理芯片ADSP-TS201S组成多DSP处理器系统,ADSP-TS201S性能如下:

基本性能指标如下:

600MHz运行速度时,内核指令周期1.67ns

24M bits片上DRAM,分为6个4M bits块(128K words X 32 bits)

片内双运算模块,每个都包含一个ALU、一个乘法器、一个移位器和一个寄存器组

双整数ALU提供数据寻址和指针操作功能

片内提供14通道DMA、外部口、4个链路口、SDRAM控制器、可编程标志引脚、2个定时器

片上仲裁系统可实现8个TigerSHARC DSP的无缝连接

内部3条互相独立的128位总线

外部数据总线64位,地址总线32位

每秒48亿次40位宽的MAC运算或每秒12亿次80位宽的MAC运算;1024点复数FFT(基2)时间15.7us

外部端口 1G字节每秒;链路口(每个)1G字节每秒

DSP处理器阵列模块中DSP1是用来整理所收集到的视频信号,并进行相应的预处理后,将数据分发送到后面的DSP,进行进一步的处理。

DSP1并行口应接FPGA输出的视频数据,还要接FLASH,完成DSP加载。DSP1的IRQ0,IRQ1分别作视频输入的帧中断和行中断,接到FPGA。其连接电路如下图3所示。

FLASH选用AMD公司的AM29LV017D,为2M x 8-Bit的存储器,可通过DSP1对FLASH编程,要保证在FLASH读写时,FPGA的数据输出总线D0~D13为高阻,反之,在数据通道运行时,也应使FLASH输出为高阻,故用BMS来选片FLASH。

图3 DSP1与FPGA,FLASH 连接图

DSP处理器阵列模块中DSP2和DSP3是用来实现图像处理中的主要算法。DSP2和DSP3分别用链路口与DSP1连接,接收由DSP1传送来的数据,DSP2和DSP3也分别用链路口连接DSP4,通过链路口将处理的数据传送给DSP4,进行下一步处理和数据整理。另外,DSP2和DSP3也直接采用链路口连接,实现DSP2和DSP3之间的通道,从而可以方便地将DSP2和DSP3配置成流水线或并行处理模式。

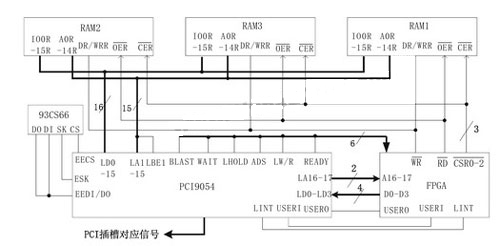

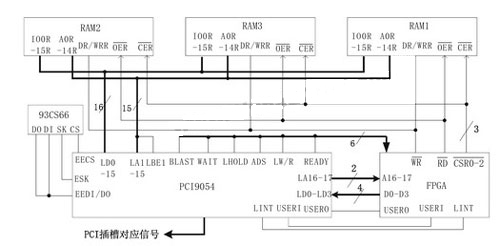

DSP处理器阵列模块中DSP4接收DSP2和DSP3发送来的数据,进行进一步处理后,将最后处理的数据通过数据总线发送到双端口RAM,通过PCI接口芯片PCI9054,将数据发送给PC机。该双端口RAM采用3片IDT70LV27(32K x 16-Bit),组成96K x 16-Bit方式,保证一次写完一帧(320%26;#215;240个象素,每个象素两个字节),当DSP4写满一帧图像数据后,向PC机产生中断,请求PC机将数据读走,当PC机读取完一帧图像数据后,应提供相应的应答,允许DSP4刷新双口RAM。DSP阵列机互连电路如图1所示,DSP4与双口RAM的连接如图4所示。DSP4接3片双口RAM,与PCI9054形成接口。DSP4的FLAG0作为通过PCI9054输出的视频传输握手信号。

ADSP-TS201S阵列机采用链路口互连方式,在主要的数据传输方向设置了数据传输启动FLAG信号到接收方的IRQ产生中断,以便更好的实现时序的匹配。

DSP1引入了工作/关闭选择(FLAG1输入),数据模式(数字/模拟)选择由DATA14引脚读入,可以在一帧数据开始输入时,读入一次数据选择模式,此后就可以不再处理了。

图3 DSP1与FPGA,FLASH 连接图

DSP处理器阵列模块中DSP2和DSP3是用来实现图像处理中的主要算法。DSP2和DSP3分别用链路口与DSP1连接,接收由DSP1传送来的数据,DSP2和DSP3也分别用链路口连接DSP4,通过链路口将处理的数据传送给DSP4,进行下一步处理和数据整理。另外,DSP2和DSP3也直接采用链路口连接,实现DSP2和DSP3之间的通道,从而可以方便地将DSP2和DSP3配置成流水线或并行处理模式。

DSP处理器阵列模块中DSP4接收DSP2和DSP3发送来的数据,进行进一步处理后,将最后处理的数据通过数据总线发送到双端口RAM,通过PCI接口芯片PCI9054,将数据发送给PC机。该双端口RAM采用3片IDT70LV27(32K x 16-Bit),组成96K x 16-Bit方式,保证一次写完一帧(320%26;#215;240个象素,每个象素两个字节),当DSP4写满一帧图像数据后,向PC机产生中断,请求PC机将数据读走,当PC机读取完一帧图像数据后,应提供相应的应答,允许DSP4刷新双口RAM。DSP阵列机互连电路如图1所示,DSP4与双口RAM的连接如图4所示。DSP4接3片双口RAM,与PCI9054形成接口。DSP4的FLAG0作为通过PCI9054输出的视频传输握手信号。

ADSP-TS201S阵列机采用链路口互连方式,在主要的数据传输方向设置了数据传输启动FLAG信号到接收方的IRQ产生中断,以便更好的实现时序的匹配。

DSP1引入了工作/关闭选择(FLAG1输入),数据模式(数字/模拟)选择由DATA14引脚读入,可以在一帧数据开始输入时,读入一次数据选择模式,此后就可以不再处理了。

图4 DSP4与双口RAM接口

%26;#183;PCI接口模块

PCI接口采用PLX公司的PCI9054接口芯片,32位,33MHZ数据总线。RAM1,2,3三片双口RAM(IDT70LV27)作DSP4数据输出缓存。由PCI9054读入到PC机。在双口RAM内,相当于右半边接口,PCI9054其电路连接如图5所示。PCI9054对应着PCI槽的信号,按PCI槽名称对应连接,加载EEPROM选用93CS66。 将LD0~LD3引入到FPGA内,可以单次I/O写方式,输出4位状态,作主机控制。开、关机,数字视频/模拟视频选择以A16~17的译码之一作地址选择。FPGA读入后,译码成控制信号输出。

图4 DSP4与双口RAM接口

%26;#183;PCI接口模块

PCI接口采用PLX公司的PCI9054接口芯片,32位,33MHZ数据总线。RAM1,2,3三片双口RAM(IDT70LV27)作DSP4数据输出缓存。由PCI9054读入到PC机。在双口RAM内,相当于右半边接口,PCI9054其电路连接如图5所示。PCI9054对应着PCI槽的信号,按PCI槽名称对应连接,加载EEPROM选用93CS66。 将LD0~LD3引入到FPGA内,可以单次I/O写方式,输出4位状态,作主机控制。开、关机,数字视频/模拟视频选择以A16~17的译码之一作地址选择。FPGA读入后,译码成控制信号输出。

图5 PCI9054与双口RAM,FPGA连接 结语

基于ADSP-TS201S的图像采集处理系统能够完成图像的高速处理,实现图像的实时显示,目标跟踪。在实际应用中该系统工作稳定,达到预想效果。

图5 PCI9054与双口RAM,FPGA连接 结语

基于ADSP-TS201S的图像采集处理系统能够完成图像的高速处理,实现图像的实时显示,目标跟踪。在实际应用中该系统工作稳定,达到预想效果。

引用地址:基于ADSP-TS201S的图像采集处理系统

图1 图像采集处理系统框图系统的各个功能模块电路设计

%26;#183;视频信号采集模块

摄像机提供两路视频信号:一路模拟视频,一路数字视频。

模拟视频信号经过钳位校正、放大后,将信号送入到A/D转换器,再经FPGA锁存后将视频信号发送给DSP1;经视频同步分离电路,由LM1881分离出模拟视频的行、场同步信号,用于控制视频数据采集到DSP1,以便进行图像处理。钳位校正、视频同步电路如图2所示。模拟视频经运放输入,将中心电平调到3.3V,加到A/D输入端。A/D转换后的数据进入FPGA锁存。运放均采用ADI公司的AD8047AR,A/D转换器采用ADI公司的AD9050。AD9050为10位A/D转换器,取其高8位进入FPGA。采样时钟12MHz,与数字视频信号相同。由FPGA对48MHz时钟四分频产生。

图1 图像采集处理系统框图系统的各个功能模块电路设计

%26;#183;视频信号采集模块

摄像机提供两路视频信号:一路模拟视频,一路数字视频。

模拟视频信号经过钳位校正、放大后,将信号送入到A/D转换器,再经FPGA锁存后将视频信号发送给DSP1;经视频同步分离电路,由LM1881分离出模拟视频的行、场同步信号,用于控制视频数据采集到DSP1,以便进行图像处理。钳位校正、视频同步电路如图2所示。模拟视频经运放输入,将中心电平调到3.3V,加到A/D输入端。A/D转换后的数据进入FPGA锁存。运放均采用ADI公司的AD8047AR,A/D转换器采用ADI公司的AD9050。AD9050为10位A/D转换器,取其高8位进入FPGA。采样时钟12MHz,与数字视频信号相同。由FPGA对48MHz时钟四分频产生。

图2 模拟视频输入转换电路

摄像机的数字视频信号为14对差分信号,经FPGA将差分信号转换为单端信号,并锁存数据。每个象素14位,每帧320%26;#215;240。

FPGA采用ALTERA公司的CYCLONE系列EP1C3T144C-6,配置芯片采用EPC2LC20。EP1C3T144C-6具有将差分信号转单端信号的专用I/O口。锁存在FPGA的数字,模拟两路视频信号根据工作模式选择输出到DSP1数据总线上,由DSP1读入处理,数据速率与模拟视频的采样速率,数字视频的数据速率相同。工作模式选择,开关控制通过PIC9054引入到FPGA。

%26;#183;DSP处理器模块

DSP处理器阵列模块主要由4片高速高性能的DSP处理芯片ADSP-TS201S组成多DSP处理器系统,ADSP-TS201S性能如下:

基本性能指标如下:

600MHz运行速度时,内核指令周期1.67ns

24M bits片上DRAM,分为6个4M bits块(128K words X 32 bits)

片内双运算模块,每个都包含一个ALU、一个乘法器、一个移位器和一个寄存器组

双整数ALU提供数据寻址和指针操作功能

片内提供14通道DMA、外部口、4个链路口、SDRAM控制器、可编程标志引脚、2个定时器

片上仲裁系统可实现8个TigerSHARC DSP的无缝连接

内部3条互相独立的128位总线

外部数据总线64位,地址总线32位

每秒48亿次40位宽的MAC运算或每秒12亿次80位宽的MAC运算;1024点复数FFT(基2)时间15.7us

外部端口 1G字节每秒;链路口(每个)1G字节每秒

DSP处理器阵列模块中DSP1是用来整理所收集到的视频信号,并进行相应的预处理后,将数据分发送到后面的DSP,进行进一步的处理。

DSP1并行口应接FPGA输出的视频数据,还要接FLASH,完成DSP加载。DSP1的IRQ0,IRQ1分别作视频输入的帧中断和行中断,接到FPGA。其连接电路如下图3所示。

FLASH选用AMD公司的AM29LV017D,为2M x 8-Bit的存储器,可通过DSP1对FLASH编程,要保证在FLASH读写时,FPGA的数据输出总线D0~D13为高阻,反之,在数据通道运行时,也应使FLASH输出为高阻,故用BMS来选片FLASH。

图2 模拟视频输入转换电路

摄像机的数字视频信号为14对差分信号,经FPGA将差分信号转换为单端信号,并锁存数据。每个象素14位,每帧320%26;#215;240。

FPGA采用ALTERA公司的CYCLONE系列EP1C3T144C-6,配置芯片采用EPC2LC20。EP1C3T144C-6具有将差分信号转单端信号的专用I/O口。锁存在FPGA的数字,模拟两路视频信号根据工作模式选择输出到DSP1数据总线上,由DSP1读入处理,数据速率与模拟视频的采样速率,数字视频的数据速率相同。工作模式选择,开关控制通过PIC9054引入到FPGA。

%26;#183;DSP处理器模块

DSP处理器阵列模块主要由4片高速高性能的DSP处理芯片ADSP-TS201S组成多DSP处理器系统,ADSP-TS201S性能如下:

基本性能指标如下:

600MHz运行速度时,内核指令周期1.67ns

24M bits片上DRAM,分为6个4M bits块(128K words X 32 bits)

片内双运算模块,每个都包含一个ALU、一个乘法器、一个移位器和一个寄存器组

双整数ALU提供数据寻址和指针操作功能

片内提供14通道DMA、外部口、4个链路口、SDRAM控制器、可编程标志引脚、2个定时器

片上仲裁系统可实现8个TigerSHARC DSP的无缝连接

内部3条互相独立的128位总线

外部数据总线64位,地址总线32位

每秒48亿次40位宽的MAC运算或每秒12亿次80位宽的MAC运算;1024点复数FFT(基2)时间15.7us

外部端口 1G字节每秒;链路口(每个)1G字节每秒

DSP处理器阵列模块中DSP1是用来整理所收集到的视频信号,并进行相应的预处理后,将数据分发送到后面的DSP,进行进一步的处理。

DSP1并行口应接FPGA输出的视频数据,还要接FLASH,完成DSP加载。DSP1的IRQ0,IRQ1分别作视频输入的帧中断和行中断,接到FPGA。其连接电路如下图3所示。

FLASH选用AMD公司的AM29LV017D,为2M x 8-Bit的存储器,可通过DSP1对FLASH编程,要保证在FLASH读写时,FPGA的数据输出总线D0~D13为高阻,反之,在数据通道运行时,也应使FLASH输出为高阻,故用BMS来选片FLASH。

图3 DSP1与FPGA,FLASH 连接图

DSP处理器阵列模块中DSP2和DSP3是用来实现图像处理中的主要算法。DSP2和DSP3分别用链路口与DSP1连接,接收由DSP1传送来的数据,DSP2和DSP3也分别用链路口连接DSP4,通过链路口将处理的数据传送给DSP4,进行下一步处理和数据整理。另外,DSP2和DSP3也直接采用链路口连接,实现DSP2和DSP3之间的通道,从而可以方便地将DSP2和DSP3配置成流水线或并行处理模式。

DSP处理器阵列模块中DSP4接收DSP2和DSP3发送来的数据,进行进一步处理后,将最后处理的数据通过数据总线发送到双端口RAM,通过PCI接口芯片PCI9054,将数据发送给PC机。该双端口RAM采用3片IDT70LV27(32K x 16-Bit),组成96K x 16-Bit方式,保证一次写完一帧(320%26;#215;240个象素,每个象素两个字节),当DSP4写满一帧图像数据后,向PC机产生中断,请求PC机将数据读走,当PC机读取完一帧图像数据后,应提供相应的应答,允许DSP4刷新双口RAM。DSP阵列机互连电路如图1所示,DSP4与双口RAM的连接如图4所示。DSP4接3片双口RAM,与PCI9054形成接口。DSP4的FLAG0作为通过PCI9054输出的视频传输握手信号。

ADSP-TS201S阵列机采用链路口互连方式,在主要的数据传输方向设置了数据传输启动FLAG信号到接收方的IRQ产生中断,以便更好的实现时序的匹配。

DSP1引入了工作/关闭选择(FLAG1输入),数据模式(数字/模拟)选择由DATA14引脚读入,可以在一帧数据开始输入时,读入一次数据选择模式,此后就可以不再处理了。

图3 DSP1与FPGA,FLASH 连接图

DSP处理器阵列模块中DSP2和DSP3是用来实现图像处理中的主要算法。DSP2和DSP3分别用链路口与DSP1连接,接收由DSP1传送来的数据,DSP2和DSP3也分别用链路口连接DSP4,通过链路口将处理的数据传送给DSP4,进行下一步处理和数据整理。另外,DSP2和DSP3也直接采用链路口连接,实现DSP2和DSP3之间的通道,从而可以方便地将DSP2和DSP3配置成流水线或并行处理模式。

DSP处理器阵列模块中DSP4接收DSP2和DSP3发送来的数据,进行进一步处理后,将最后处理的数据通过数据总线发送到双端口RAM,通过PCI接口芯片PCI9054,将数据发送给PC机。该双端口RAM采用3片IDT70LV27(32K x 16-Bit),组成96K x 16-Bit方式,保证一次写完一帧(320%26;#215;240个象素,每个象素两个字节),当DSP4写满一帧图像数据后,向PC机产生中断,请求PC机将数据读走,当PC机读取完一帧图像数据后,应提供相应的应答,允许DSP4刷新双口RAM。DSP阵列机互连电路如图1所示,DSP4与双口RAM的连接如图4所示。DSP4接3片双口RAM,与PCI9054形成接口。DSP4的FLAG0作为通过PCI9054输出的视频传输握手信号。

ADSP-TS201S阵列机采用链路口互连方式,在主要的数据传输方向设置了数据传输启动FLAG信号到接收方的IRQ产生中断,以便更好的实现时序的匹配。

DSP1引入了工作/关闭选择(FLAG1输入),数据模式(数字/模拟)选择由DATA14引脚读入,可以在一帧数据开始输入时,读入一次数据选择模式,此后就可以不再处理了。

图4 DSP4与双口RAM接口

%26;#183;PCI接口模块

PCI接口采用PLX公司的PCI9054接口芯片,32位,33MHZ数据总线。RAM1,2,3三片双口RAM(IDT70LV27)作DSP4数据输出缓存。由PCI9054读入到PC机。在双口RAM内,相当于右半边接口,PCI9054其电路连接如图5所示。PCI9054对应着PCI槽的信号,按PCI槽名称对应连接,加载EEPROM选用93CS66。 将LD0~LD3引入到FPGA内,可以单次I/O写方式,输出4位状态,作主机控制。开、关机,数字视频/模拟视频选择以A16~17的译码之一作地址选择。FPGA读入后,译码成控制信号输出。

图4 DSP4与双口RAM接口

%26;#183;PCI接口模块

PCI接口采用PLX公司的PCI9054接口芯片,32位,33MHZ数据总线。RAM1,2,3三片双口RAM(IDT70LV27)作DSP4数据输出缓存。由PCI9054读入到PC机。在双口RAM内,相当于右半边接口,PCI9054其电路连接如图5所示。PCI9054对应着PCI槽的信号,按PCI槽名称对应连接,加载EEPROM选用93CS66。 将LD0~LD3引入到FPGA内,可以单次I/O写方式,输出4位状态,作主机控制。开、关机,数字视频/模拟视频选择以A16~17的译码之一作地址选择。FPGA读入后,译码成控制信号输出。

图5 PCI9054与双口RAM,FPGA连接 结语

基于ADSP-TS201S的图像采集处理系统能够完成图像的高速处理,实现图像的实时显示,目标跟踪。在实际应用中该系统工作稳定,达到预想效果。

图5 PCI9054与双口RAM,FPGA连接 结语

基于ADSP-TS201S的图像采集处理系统能够完成图像的高速处理,实现图像的实时显示,目标跟踪。在实际应用中该系统工作稳定,达到预想效果。

上一篇:EDMA在实时图像处理系统中的应用

下一篇:TMS320VC5402 DSP与ISD4004语音录放芯片的接谏杓萍捌湫畔⒐芾?

硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术 TLC2264INSR

TLC2264INSR

京公网安备 11010802033920号

京公网安备 11010802033920号