摘 要 通过对TI公司TMS320C5000系列DSP HPI总线和PC104总线时序的分析,以VHDL语言为工具,使用Altera的FPGA芯片EP1K50,设计完成PCI04总线和DSP HPI总线之间的通信接口,并在一款以TMS320VC5409DSP为数据采集处理器、研华嵌入式工控主板PCM-5825为系统主板组成的嵌入式数据采集系统申得到了运用;给出与整个接口设计相关的VHDL源代码和在PCM-5825上验证接口设计的X86汇编语言程序。

关键词 DSP HPI PC104总线 FPGA VHDL源代码

在一款嵌入式数据采集系统的设计中,采用TMS320VC5409 DSP作为对多路信号的采集与预处理,处理后的数据送至12.7 Cm(5in)的工控计算机中进行分析与保存。因为工控机的总线为PC104,因此需要设计PC104与DSP之间的通信接口。系统中以Altera公司的一片FPGA芯片EPlK50来对该接口和数据采集过程中的逻辑控制与FIFO进行设计。下面主要阐述该通信接口的设计。

1 DSP的HP0接口

TMS320VC5409 DSP的HPI是一个8位的并行接口,主要用来与主设备或主处理器接口。DSP内部有一定数量的双访问RAM,除了DSP本身可以访问该RAM区域外,主机也可以通过HPI口实现对双访问RAM的访问,从而实现主机与DSP的通信。

HPI接口通过HPI控制寄存器HPIC、地址寄存器HPIA、数据寄存器HPID等3个HPI寄存器进行控制和实现数据传输。这3个寄存器都是16位的,因此主机访问这些寄存器时需要分两次操作才能完成。

HPIC只有4位用于控制HPI的操作,这4位分别位于高字节和低字节的低4位,并规定HPIC的高低字节必须相同:

Bit0/8(BOB)一一用于字节顺序控制,BOB=1表示第1个字节为低字节,否则第1个字节为高字节;

Bitl/9(SMOD)一一访问模式控制,SMOD=l表示共享访问模式(SAM),否则为主机访问模式(HOM);

Bit2/10(DSPINT)一一主机通过将该位写l来向DSP发送1次HPI中断;

Bit3/11(H1NT)一一DSP通过向该位置l,使外部引脚HINT产生一个低电子作为给主机的中断,中断的清除必须由主机向该位写l来清除。

HPID是数据寄存器,主机通过读写该寄存器来实现对共享RAM的读写,RAM的地址则由HPIA地址寄存器的内容来决定。因此,主机对DSP的访问过程是,先往HPI地址寄存器HPIA写入欲访问的地址,然后再对数据寄存器HPID进行读或写访问。

HPI接口信号包括:

HAS一一输入,地址锁存信号,可连接到高电平;

HBIL一一输入,字节识别信号,用来识别传输的是高电平还是低电平;

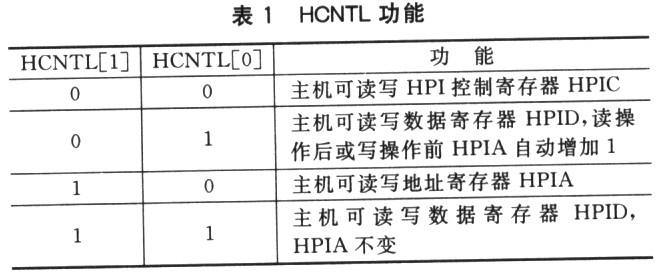

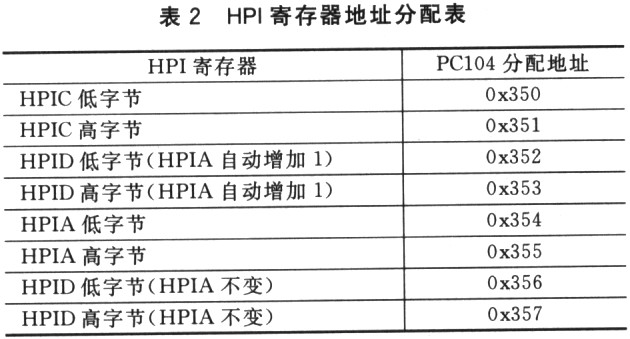

HCNTL[1..0]一一输入,HPI寄存器的访问地址信号,主机用来选择访问的HPI寄存器。如表l所列;

HCS一一输入,HPI片选信号,低电平有效;

HD[7..0]一一双向三态数据总线;

HDS1/HDS2一一数据输入选通信号,可将其中一个接低电平,另一个接逻辑控制;

HINT一一输出,给主机的中断信号,由HPIC寄存器的HINT位控制;

HRDY一一输出,HPI准备好,高电子有效;

HR/W一一输入,读写控制信号,高电子表示主机进行读操作,低电子表示主机进行写操作。

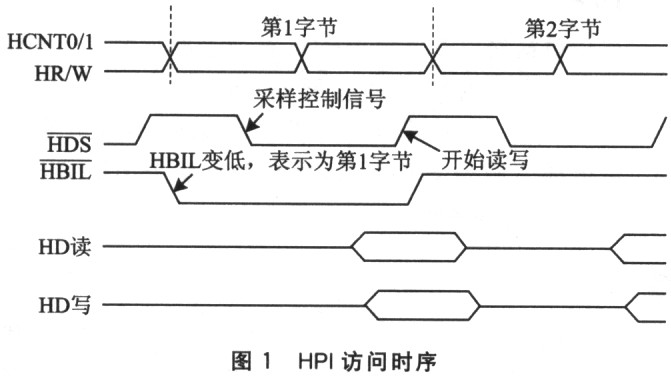

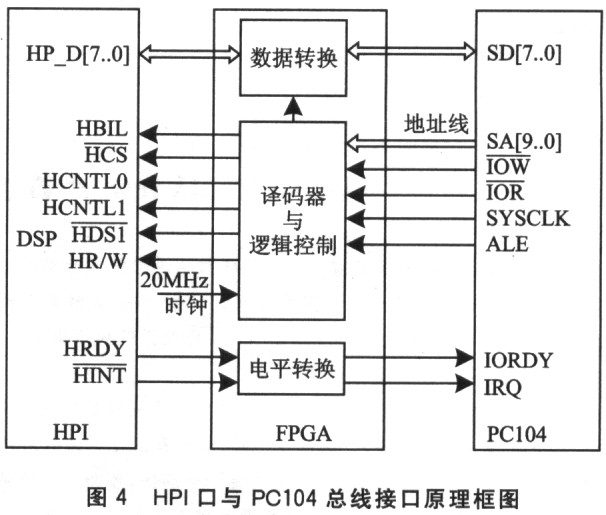

HPI的访问时序如图l所示。如前所述,访问寄存器时需要分两次操作才能完成。

HCS一一输入,HPI片选信号,低电平有效;

HD[7..0]一一双向三态数据总线;

HDS1/HDS2一一数据输入选通信号,可将其中一个接低电平,另一个接逻辑控制;

HINT一一输出,给主机的中断信号,由HPIC寄存器的HINT位控制;

HRDY一一输出,HPI准备好,高电子有效;

HR/W一一输入,读写控制信号,高电子表示主机进行读操作,低电子表示主机进行写操作。

HPI的访问时序如图l所示。如前所述,访问寄存器时需要分两次操作才能完成。

2 PC104总线

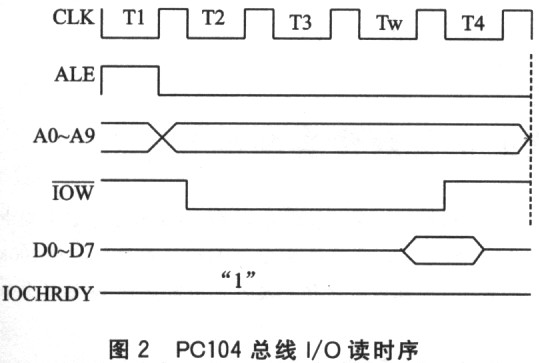

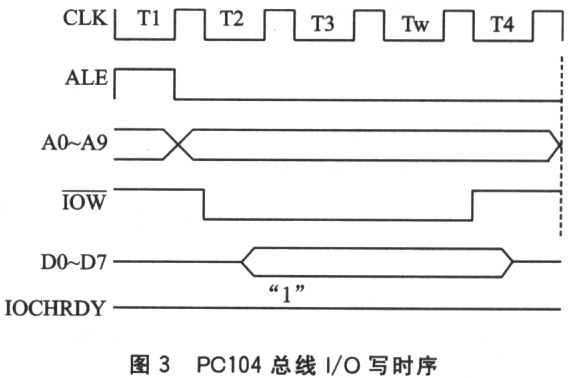

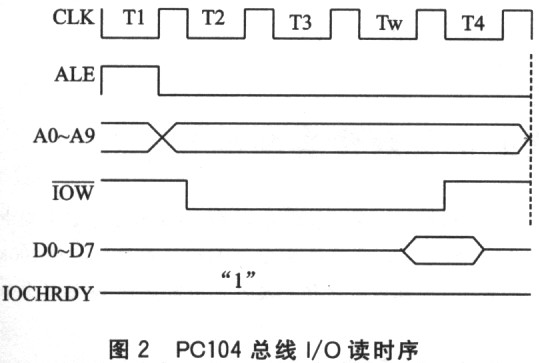

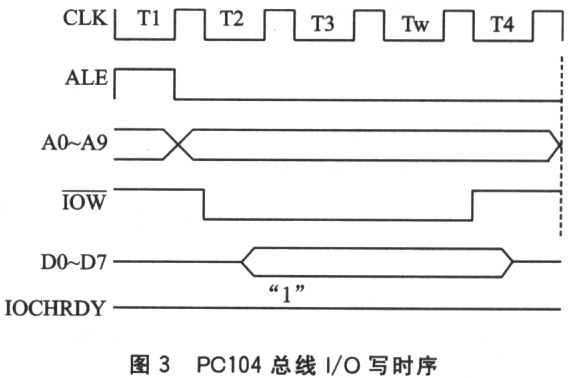

PC104总线是从ISA总线衍生而来的,主要是为了适应嵌入式系统的需要。在8.89 cm(3.5 in)和12.7cm(5in)工控主板中,大多使用PC104总线作为标准接口总线。PC104总线共有104根引脚,其中绝大多数与ISA总线信号特性完全一致,只有极个别的信号有区别,因此在应用中完全可以按ISA总线使用。PC104总线与ISA总线一样,是一个16位和8位同时兼容的总线。在本系统中,使用的是8位的方式,将DSP的HPI口作为PC104总线的8位I/O设备。PC104总线的I/O访问时序如图2和图3所示。

2 PC104总线

PC104总线是从ISA总线衍生而来的,主要是为了适应嵌入式系统的需要。在8.89 cm(3.5 in)和12.7cm(5in)工控主板中,大多使用PC104总线作为标准接口总线。PC104总线共有104根引脚,其中绝大多数与ISA总线信号特性完全一致,只有极个别的信号有区别,因此在应用中完全可以按ISA总线使用。PC104总线与ISA总线一样,是一个16位和8位同时兼容的总线。在本系统中,使用的是8位的方式,将DSP的HPI口作为PC104总线的8位I/O设备。PC104总线的I/O访问时序如图2和图3所示。

根据PC104总线的I/O访问时序,只需使用以下的总线信号,即可完成8位总线的通信设计:

SD[7..0]一一PC104数据总线;

SA[9..0]一一PC104地址总线;

IOW一一PC104端口写控制,低电平有效,表示对I/0口写操作,由OUT指令执行;

IOR一PC104端口读控制,低电子有效,表示对I/O口读操作,由IN指令执行;

SYSCLK一一PC104总线时钟;

ALE一一地址锁存信号,在此不用作地址锁存,而是用作总线周期的开始同步,它的下降沿表示总线周期开始;

IOCHRDY一一I/0设备就绪信号,当将该电平为低(无效状态)时,表示I/0设备要延长总线周期,信号由三态门或集电极开路门驱动;

IRQ一一中断请求信号,当I/O设备需要向PC机通信或是采集的信号已经准备好后,向PC发起中断,申请通信,PC将数据读走。

3 接口设计

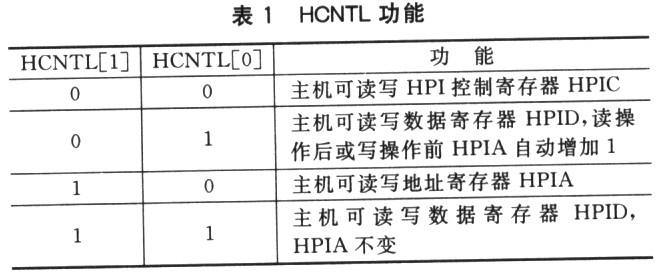

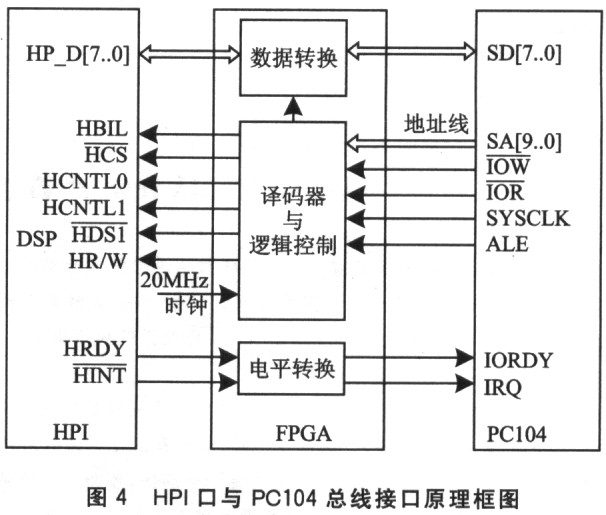

根据前面的分析,得出接口原理如图4所示。

根据PC104总线的I/O访问时序,只需使用以下的总线信号,即可完成8位总线的通信设计:

SD[7..0]一一PC104数据总线;

SA[9..0]一一PC104地址总线;

IOW一一PC104端口写控制,低电平有效,表示对I/0口写操作,由OUT指令执行;

IOR一PC104端口读控制,低电子有效,表示对I/O口读操作,由IN指令执行;

SYSCLK一一PC104总线时钟;

ALE一一地址锁存信号,在此不用作地址锁存,而是用作总线周期的开始同步,它的下降沿表示总线周期开始;

IOCHRDY一一I/0设备就绪信号,当将该电平为低(无效状态)时,表示I/0设备要延长总线周期,信号由三态门或集电极开路门驱动;

IRQ一一中断请求信号,当I/O设备需要向PC机通信或是采集的信号已经准备好后,向PC发起中断,申请通信,PC将数据读走。

3 接口设计

根据前面的分析,得出接口原理如图4所示。

图4中,FPGA为EPlK50。EPlK50内部拥有2880个逻辑单元,40 960位的RAM。在本系统中,不仅作为HPI和PC104的接口逻辑,还有其他功能,如FIFO、A/D控制等。

EP1K50的内核供电电压为2.5 V,I/O供电电压为3.3 V,可以直接与I/O供电电压也是3.3 V的TMS320VC5409 DSP相连.另外,EPIK50能承受-0.7"5.75V的输入电子,输出则与TTL电平兼容,因此EP1K50也可以直接与5 VTTL电平的PC104总线相连,从而在DSP和PC104总线之间起电平转换的作用,不需再使用其他的电子转换器件,简化了电路设计。

对于接口设计来说,最主要的就是时序设计。时序设计正确了,系统就能正确地工作。在综合了HPI的访问时序与PC104总线的读写时序后,得出以下设计方法:

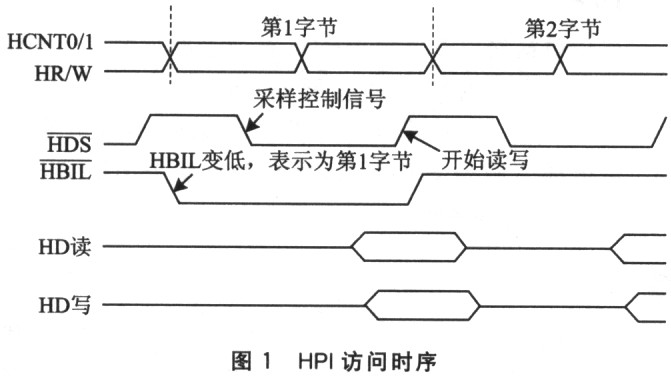

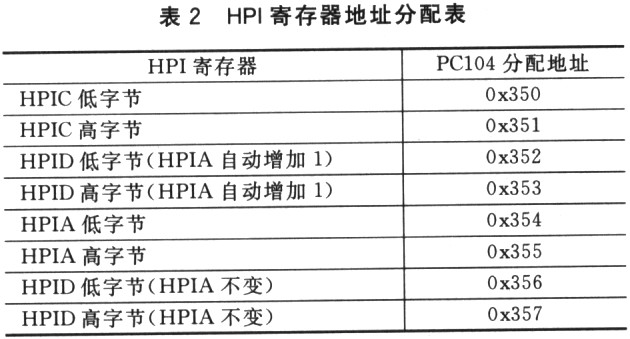

①对于HPI寄存器的访问可以通过地址编码实现,偶地址对应寄存器的低字节,奇地址对应寄存器的高字节,如表2所列。

图4中,FPGA为EPlK50。EPlK50内部拥有2880个逻辑单元,40 960位的RAM。在本系统中,不仅作为HPI和PC104的接口逻辑,还有其他功能,如FIFO、A/D控制等。

EP1K50的内核供电电压为2.5 V,I/O供电电压为3.3 V,可以直接与I/O供电电压也是3.3 V的TMS320VC5409 DSP相连.另外,EPIK50能承受-0.7"5.75V的输入电子,输出则与TTL电平兼容,因此EP1K50也可以直接与5 VTTL电平的PC104总线相连,从而在DSP和PC104总线之间起电平转换的作用,不需再使用其他的电子转换器件,简化了电路设计。

对于接口设计来说,最主要的就是时序设计。时序设计正确了,系统就能正确地工作。在综合了HPI的访问时序与PC104总线的读写时序后,得出以下设计方法:

①对于HPI寄存器的访问可以通过地址编码实现,偶地址对应寄存器的低字节,奇地址对应寄存器的高字节,如表2所列。

于是相应信号关系为:

HCNTL[1..0]=SA[2..1]

HBIL=SA[0]

当SA[9..0]=0x350"0x357时,HCS=0,SA[9..0]

为其他值时,HCS=1。

②HD[7..O]和SD[7..0]设计成双向总线。

③HR/W的产生:当PCI04进行读操作时,HR/W=1;当PC104进行写操作时,HR/W=0。于是:

HR/W=0,当IOR=1且IOW=0时;

HR/W=1,当IOR=0且IOW=1时。

④在DSP上将HDS2直接接低电子,HDSl在HBIL为0和HBIL为1时,分别产生一个变化沿,用以选通数据。该信号的产生是接口设计成功的关键。在此使用PCI04总线的系统时钟信号SYSCLK来计数产生。详细过程可参见VHDL代码。

⑤PCI04总线的中断请求信号IRQ=HINT取非。因为PC104设置为上升沿中断。

⑥PC104总线的外部I/0准备好信号IORDY在地址选通有效过程中接HPI口的HRDY信号,地址选通无效时置为高阻态。

4 代码设计

代码包括接口设计的VHDL源码和验证的X86汇编语言代码,代码内容见本刊网站(WWW.dpj.com.cn)。VHDL代码在Altera公司的开发工具QuartusII下编译,经下载电缆下载到FPGA后,可在Debug中用汇编语言对DSP进行读写验证。

结 语

本文使用VHDL语言和FPGA,设计了PC104总线与DSP之间的接口。之所以使用FPGA,是因为在系统中FPGA还包含有其他的功能设计。如果只有PC104总线与DSP之间的接口设计,使用CPLD即可完成,而不必浪费FPGA的资源。

于是相应信号关系为:

HCNTL[1..0]=SA[2..1]

HBIL=SA[0]

当SA[9..0]=0x350"0x357时,HCS=0,SA[9..0]

为其他值时,HCS=1。

②HD[7..O]和SD[7..0]设计成双向总线。

③HR/W的产生:当PCI04进行读操作时,HR/W=1;当PC104进行写操作时,HR/W=0。于是:

HR/W=0,当IOR=1且IOW=0时;

HR/W=1,当IOR=0且IOW=1时。

④在DSP上将HDS2直接接低电子,HDSl在HBIL为0和HBIL为1时,分别产生一个变化沿,用以选通数据。该信号的产生是接口设计成功的关键。在此使用PCI04总线的系统时钟信号SYSCLK来计数产生。详细过程可参见VHDL代码。

⑤PCI04总线的中断请求信号IRQ=HINT取非。因为PC104设置为上升沿中断。

⑥PC104总线的外部I/0准备好信号IORDY在地址选通有效过程中接HPI口的HRDY信号,地址选通无效时置为高阻态。

4 代码设计

代码包括接口设计的VHDL源码和验证的X86汇编语言代码,代码内容见本刊网站(WWW.dpj.com.cn)。VHDL代码在Altera公司的开发工具QuartusII下编译,经下载电缆下载到FPGA后,可在Debug中用汇编语言对DSP进行读写验证。

结 语

本文使用VHDL语言和FPGA,设计了PC104总线与DSP之间的接口。之所以使用FPGA,是因为在系统中FPGA还包含有其他的功能设计。如果只有PC104总线与DSP之间的接口设计,使用CPLD即可完成,而不必浪费FPGA的资源。

引用地址:DSP HPI口与PC104总线接口的FPGA设计

HCS一一输入,HPI片选信号,低电平有效;

HD[7..0]一一双向三态数据总线;

HDS1/HDS2一一数据输入选通信号,可将其中一个接低电平,另一个接逻辑控制;

HINT一一输出,给主机的中断信号,由HPIC寄存器的HINT位控制;

HRDY一一输出,HPI准备好,高电子有效;

HR/W一一输入,读写控制信号,高电子表示主机进行读操作,低电子表示主机进行写操作。

HPI的访问时序如图l所示。如前所述,访问寄存器时需要分两次操作才能完成。

HCS一一输入,HPI片选信号,低电平有效;

HD[7..0]一一双向三态数据总线;

HDS1/HDS2一一数据输入选通信号,可将其中一个接低电平,另一个接逻辑控制;

HINT一一输出,给主机的中断信号,由HPIC寄存器的HINT位控制;

HRDY一一输出,HPI准备好,高电子有效;

HR/W一一输入,读写控制信号,高电子表示主机进行读操作,低电子表示主机进行写操作。

HPI的访问时序如图l所示。如前所述,访问寄存器时需要分两次操作才能完成。

2 PC104总线

PC104总线是从ISA总线衍生而来的,主要是为了适应嵌入式系统的需要。在8.89 cm(3.5 in)和12.7cm(5in)工控主板中,大多使用PC104总线作为标准接口总线。PC104总线共有104根引脚,其中绝大多数与ISA总线信号特性完全一致,只有极个别的信号有区别,因此在应用中完全可以按ISA总线使用。PC104总线与ISA总线一样,是一个16位和8位同时兼容的总线。在本系统中,使用的是8位的方式,将DSP的HPI口作为PC104总线的8位I/O设备。PC104总线的I/O访问时序如图2和图3所示。

2 PC104总线

PC104总线是从ISA总线衍生而来的,主要是为了适应嵌入式系统的需要。在8.89 cm(3.5 in)和12.7cm(5in)工控主板中,大多使用PC104总线作为标准接口总线。PC104总线共有104根引脚,其中绝大多数与ISA总线信号特性完全一致,只有极个别的信号有区别,因此在应用中完全可以按ISA总线使用。PC104总线与ISA总线一样,是一个16位和8位同时兼容的总线。在本系统中,使用的是8位的方式,将DSP的HPI口作为PC104总线的8位I/O设备。PC104总线的I/O访问时序如图2和图3所示。

根据PC104总线的I/O访问时序,只需使用以下的总线信号,即可完成8位总线的通信设计:

SD[7..0]一一PC104数据总线;

SA[9..0]一一PC104地址总线;

IOW一一PC104端口写控制,低电平有效,表示对I/0口写操作,由OUT指令执行;

IOR一PC104端口读控制,低电子有效,表示对I/O口读操作,由IN指令执行;

SYSCLK一一PC104总线时钟;

ALE一一地址锁存信号,在此不用作地址锁存,而是用作总线周期的开始同步,它的下降沿表示总线周期开始;

IOCHRDY一一I/0设备就绪信号,当将该电平为低(无效状态)时,表示I/0设备要延长总线周期,信号由三态门或集电极开路门驱动;

IRQ一一中断请求信号,当I/O设备需要向PC机通信或是采集的信号已经准备好后,向PC发起中断,申请通信,PC将数据读走。

3 接口设计

根据前面的分析,得出接口原理如图4所示。

根据PC104总线的I/O访问时序,只需使用以下的总线信号,即可完成8位总线的通信设计:

SD[7..0]一一PC104数据总线;

SA[9..0]一一PC104地址总线;

IOW一一PC104端口写控制,低电平有效,表示对I/0口写操作,由OUT指令执行;

IOR一PC104端口读控制,低电子有效,表示对I/O口读操作,由IN指令执行;

SYSCLK一一PC104总线时钟;

ALE一一地址锁存信号,在此不用作地址锁存,而是用作总线周期的开始同步,它的下降沿表示总线周期开始;

IOCHRDY一一I/0设备就绪信号,当将该电平为低(无效状态)时,表示I/0设备要延长总线周期,信号由三态门或集电极开路门驱动;

IRQ一一中断请求信号,当I/O设备需要向PC机通信或是采集的信号已经准备好后,向PC发起中断,申请通信,PC将数据读走。

3 接口设计

根据前面的分析,得出接口原理如图4所示。

图4中,FPGA为EPlK50。EPlK50内部拥有2880个逻辑单元,40 960位的RAM。在本系统中,不仅作为HPI和PC104的接口逻辑,还有其他功能,如FIFO、A/D控制等。

EP1K50的内核供电电压为2.5 V,I/O供电电压为3.3 V,可以直接与I/O供电电压也是3.3 V的TMS320VC5409 DSP相连.另外,EPIK50能承受-0.7"5.75V的输入电子,输出则与TTL电平兼容,因此EP1K50也可以直接与5 VTTL电平的PC104总线相连,从而在DSP和PC104总线之间起电平转换的作用,不需再使用其他的电子转换器件,简化了电路设计。

对于接口设计来说,最主要的就是时序设计。时序设计正确了,系统就能正确地工作。在综合了HPI的访问时序与PC104总线的读写时序后,得出以下设计方法:

①对于HPI寄存器的访问可以通过地址编码实现,偶地址对应寄存器的低字节,奇地址对应寄存器的高字节,如表2所列。

图4中,FPGA为EPlK50。EPlK50内部拥有2880个逻辑单元,40 960位的RAM。在本系统中,不仅作为HPI和PC104的接口逻辑,还有其他功能,如FIFO、A/D控制等。

EP1K50的内核供电电压为2.5 V,I/O供电电压为3.3 V,可以直接与I/O供电电压也是3.3 V的TMS320VC5409 DSP相连.另外,EPIK50能承受-0.7"5.75V的输入电子,输出则与TTL电平兼容,因此EP1K50也可以直接与5 VTTL电平的PC104总线相连,从而在DSP和PC104总线之间起电平转换的作用,不需再使用其他的电子转换器件,简化了电路设计。

对于接口设计来说,最主要的就是时序设计。时序设计正确了,系统就能正确地工作。在综合了HPI的访问时序与PC104总线的读写时序后,得出以下设计方法:

①对于HPI寄存器的访问可以通过地址编码实现,偶地址对应寄存器的低字节,奇地址对应寄存器的高字节,如表2所列。

于是相应信号关系为:

HCNTL[1..0]=SA[2..1]

HBIL=SA[0]

当SA[9..0]=0x350"0x357时,HCS=0,SA[9..0]

为其他值时,HCS=1。

②HD[7..O]和SD[7..0]设计成双向总线。

③HR/W的产生:当PCI04进行读操作时,HR/W=1;当PC104进行写操作时,HR/W=0。于是:

HR/W=0,当IOR=1且IOW=0时;

HR/W=1,当IOR=0且IOW=1时。

④在DSP上将HDS2直接接低电子,HDSl在HBIL为0和HBIL为1时,分别产生一个变化沿,用以选通数据。该信号的产生是接口设计成功的关键。在此使用PCI04总线的系统时钟信号SYSCLK来计数产生。详细过程可参见VHDL代码。

⑤PCI04总线的中断请求信号IRQ=HINT取非。因为PC104设置为上升沿中断。

⑥PC104总线的外部I/0准备好信号IORDY在地址选通有效过程中接HPI口的HRDY信号,地址选通无效时置为高阻态。

4 代码设计

代码包括接口设计的VHDL源码和验证的X86汇编语言代码,代码内容见本刊网站(WWW.dpj.com.cn)。VHDL代码在Altera公司的开发工具QuartusII下编译,经下载电缆下载到FPGA后,可在Debug中用汇编语言对DSP进行读写验证。

结 语

本文使用VHDL语言和FPGA,设计了PC104总线与DSP之间的接口。之所以使用FPGA,是因为在系统中FPGA还包含有其他的功能设计。如果只有PC104总线与DSP之间的接口设计,使用CPLD即可完成,而不必浪费FPGA的资源。

于是相应信号关系为:

HCNTL[1..0]=SA[2..1]

HBIL=SA[0]

当SA[9..0]=0x350"0x357时,HCS=0,SA[9..0]

为其他值时,HCS=1。

②HD[7..O]和SD[7..0]设计成双向总线。

③HR/W的产生:当PCI04进行读操作时,HR/W=1;当PC104进行写操作时,HR/W=0。于是:

HR/W=0,当IOR=1且IOW=0时;

HR/W=1,当IOR=0且IOW=1时。

④在DSP上将HDS2直接接低电子,HDSl在HBIL为0和HBIL为1时,分别产生一个变化沿,用以选通数据。该信号的产生是接口设计成功的关键。在此使用PCI04总线的系统时钟信号SYSCLK来计数产生。详细过程可参见VHDL代码。

⑤PCI04总线的中断请求信号IRQ=HINT取非。因为PC104设置为上升沿中断。

⑥PC104总线的外部I/0准备好信号IORDY在地址选通有效过程中接HPI口的HRDY信号,地址选通无效时置为高阻态。

4 代码设计

代码包括接口设计的VHDL源码和验证的X86汇编语言代码,代码内容见本刊网站(WWW.dpj.com.cn)。VHDL代码在Altera公司的开发工具QuartusII下编译,经下载电缆下载到FPGA后,可在Debug中用汇编语言对DSP进行读写验证。

结 语

本文使用VHDL语言和FPGA,设计了PC104总线与DSP之间的接口。之所以使用FPGA,是因为在系统中FPGA还包含有其他的功能设计。如果只有PC104总线与DSP之间的接口设计,使用CPLD即可完成,而不必浪费FPGA的资源。

上一篇:CF卡与双核DSP的实现

下一篇:基于DSP的程控交流电源的研制

小广播

热门活动

换一批

更多

最新应用文章

更多热门文章

更多每日新闻

更多往期活动

- 有奖直播 | 与英飞凌一同革新您的电动汽车温控系统:集成热管理系统(低压侧)

- 【抢楼有礼】TI TMS320F28377S 入门经验大搜集!

- 兆易创新 GD32E231 DIY 大赛,百套超值型开发板免费申请+重磅豪礼!

- 您的无人机安全吗?使用电路保护应对安全隐患

- ADI有奖下载活动之12 ADI基于视觉的占用检测解决方案

- MSP430 多款开发工具优惠促销,总有一款会适合你!

- 【开工大吉,抢楼有礼】聊一聊你感兴趣的技术和板子

- Keysight教你如何提高测试精度,答对问题还有礼品相送,速速参与!

- Discover mmWave 走进 TI 毫米波雷达世界 快速获得设计技能

- 评论有礼:用混合信号示波器探索总线的秘密

厂商技术中心

硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术 CA748CSX

CA748CSX

京公网安备 11010802033920号

京公网安备 11010802033920号