摘要:VirtexE系列是XILINX公司生产的新型FPGA芯片,可用来进行数十万逻辑门级的系统设计和百兆赫兹级的高速电路设计。文中介绍了XCV50E芯片的结构特性、设计流程和配置过程,给出了具体的电路图和配置流程图。

关键词:FPGA 可配置逻辑块 设计流程 配置

XCV50E是XILINX公司VirtexE系列系统级FPGA芯片中的一员。其主要资源有71693个系统门、65536位块内存和176个用户I/O口(其中包括83对差分I/O口)。

主要特性有:1.8V超低核心电压、支持20种高速总线标准、八个全数字延迟锁定环、0.18微米6层金属工艺、支持IEEE 1149.1边界扫描。VirtexE系列FPGA芯片具有卓越的整体性能和高速特性,是实现高速系统级设计的优选芯片。下面以XCV50E为例,介绍VirtexE系列FPGA的结构特性和开发流程。

1 XCV50E芯片的结构

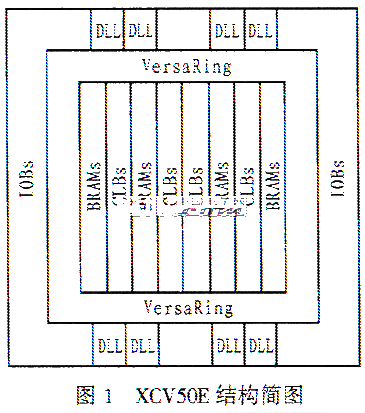

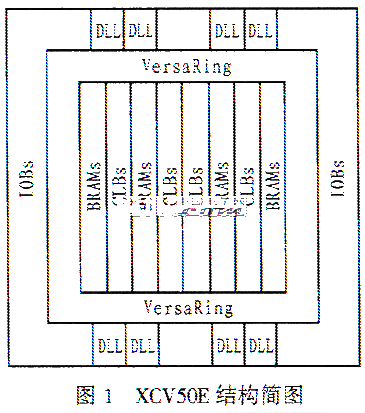

XCV50E芯片主要由四部分组成,其结构图如图1所示,芯片中央是由16%26;#215;24个可编程逻辑块(CLB)构成的CLB阵列,用以实现芯片的主要逻辑功能。芯片中16个4kB的块内存(Block RAM

或BRAM)组成4个块内存槽,位于CLK阵列的两端及接近芯片中心的位置。块内存可用作高速RAM或FIFO。环绕CLB阵列的是叫做VersaRing的布线资源,它连接内部的逻辑信号到输入输出单元。输入输出单元位于芯片周边,用以实现不同标准信号(如LVDS、CMOS、GTL)间的和转换。

1.1 可配置逻辑块

可配置逻辑块是FPGA的核心部分,主要用来实现各种逻辑功能。其内部结构见图2所示。每个可配置逻辑块包括左右两个功能片。每个功能片包括两个逻辑单元。每个逻辑单元由一个四输入查找表(LUT)、一个进位逻辑和一个寄存器组成。查找表可作为函数产生器来使用,也可用作高速16位移位寄存器或16%26;#215;1的随机存取内存(RAM)。为扩展芯片的逻辑功能,在每个功能片中还设有一个F5复选器,在每个逻辑块中设有一个F6复选器,可分别用以实现9输入的函数和19输入的函数。

1.2 通用布线资源

芯片内部与可配置逻辑块阵列相匹配的是通用布线矩阵阵列(GRM)。GRM是开关矩阵,它用足够的连线将对应的可配置逻辑连接到相邻可配置逻辑块和部分远端的可配置逻辑块。芯片内有许多双向长线分别横贯和纵贯整个芯片,利用它们可以快速高效地分配信号。通过通用布线资源,各个可配置逻辑块和块内存构成了一个高速动作的统一整体。

图2

1.3 VersaRing布线资源

VersaRing环绕着芯片中央的CLB阵列,它将阵列信号与芯片I/O管脚相连。VersaRing以毫微秒级的速度将任一内部逻辑信号连接到芯片的任一I/O管脚。正是由于XCV50E这种信号分配的任意性,使得XCV50E的设计工作可以与电路板制版并行进行,从而大大缩短了开发周期。

1.4 延迟锁存环(DLL)

芯片内有八个延迟锁定环,借助它们可以实现高速零时延的时钟信号,延迟锁定环的输入时钟范围是25MHz"350MHz,输出时钟的传输时延为零,边沿抖动小于60ps。锁定环可对时钟进行二倍频或2"16倍分频,并可进行90o、180o、270o的移相操作。使用延迟锁定环可有效解决高速应用中信号的时滞和抖动问题。

主要特性有:1.8V超低核心电压、支持20种高速总线标准、八个全数字延迟锁定环、0.18微米6层金属工艺、支持IEEE 1149.1边界扫描。VirtexE系列FPGA芯片具有卓越的整体性能和高速特性,是实现高速系统级设计的优选芯片。下面以XCV50E为例,介绍VirtexE系列FPGA的结构特性和开发流程。

1 XCV50E芯片的结构

XCV50E芯片主要由四部分组成,其结构图如图1所示,芯片中央是由16%26;#215;24个可编程逻辑块(CLB)构成的CLB阵列,用以实现芯片的主要逻辑功能。芯片中16个4kB的块内存(Block RAM

或BRAM)组成4个块内存槽,位于CLK阵列的两端及接近芯片中心的位置。块内存可用作高速RAM或FIFO。环绕CLB阵列的是叫做VersaRing的布线资源,它连接内部的逻辑信号到输入输出单元。输入输出单元位于芯片周边,用以实现不同标准信号(如LVDS、CMOS、GTL)间的和转换。

1.1 可配置逻辑块

可配置逻辑块是FPGA的核心部分,主要用来实现各种逻辑功能。其内部结构见图2所示。每个可配置逻辑块包括左右两个功能片。每个功能片包括两个逻辑单元。每个逻辑单元由一个四输入查找表(LUT)、一个进位逻辑和一个寄存器组成。查找表可作为函数产生器来使用,也可用作高速16位移位寄存器或16%26;#215;1的随机存取内存(RAM)。为扩展芯片的逻辑功能,在每个功能片中还设有一个F5复选器,在每个逻辑块中设有一个F6复选器,可分别用以实现9输入的函数和19输入的函数。

1.2 通用布线资源

芯片内部与可配置逻辑块阵列相匹配的是通用布线矩阵阵列(GRM)。GRM是开关矩阵,它用足够的连线将对应的可配置逻辑连接到相邻可配置逻辑块和部分远端的可配置逻辑块。芯片内有许多双向长线分别横贯和纵贯整个芯片,利用它们可以快速高效地分配信号。通过通用布线资源,各个可配置逻辑块和块内存构成了一个高速动作的统一整体。

图2

1.3 VersaRing布线资源

VersaRing环绕着芯片中央的CLB阵列,它将阵列信号与芯片I/O管脚相连。VersaRing以毫微秒级的速度将任一内部逻辑信号连接到芯片的任一I/O管脚。正是由于XCV50E这种信号分配的任意性,使得XCV50E的设计工作可以与电路板制版并行进行,从而大大缩短了开发周期。

1.4 延迟锁存环(DLL)

芯片内有八个延迟锁定环,借助它们可以实现高速零时延的时钟信号,延迟锁定环的输入时钟范围是25MHz"350MHz,输出时钟的传输时延为零,边沿抖动小于60ps。锁定环可对时钟进行二倍频或2"16倍分频,并可进行90o、180o、270o的移相操作。使用延迟锁定环可有效解决高速应用中信号的时滞和抖动问题。

2 XCV50E的开发

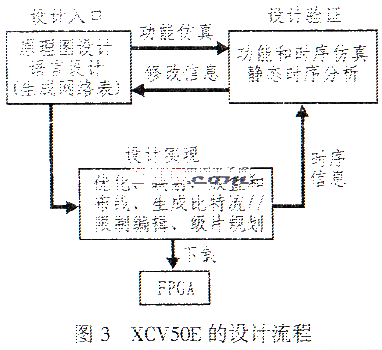

笔者使用Xilin Foundation F4.1来开发

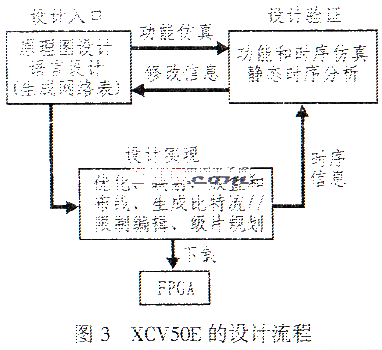

XCV50E芯片。Xilin Foundation F4.1是Xilinx公司主要的FPGA芯片开发平台之一。基于该平台可实现XCV50E芯片从设备构想到此特流下载的全部过程。图3所示是基于该平台开发XCV50E的设计流程。该平台的由设计入口工具、设计实现工具、设计验证工具三大部分构成。设计入口工具接收各种图形或文字的设计输入,并最终生成网络表文件。设计实现工具将网络表转化为配置比特流,并下载到器件。设计验证工具用来对设计中的逻辑关系及输出结果进行仿真和时序阻制分析。

2 XCV50E的开发

笔者使用Xilin Foundation F4.1来开发

XCV50E芯片。Xilin Foundation F4.1是Xilinx公司主要的FPGA芯片开发平台之一。基于该平台可实现XCV50E芯片从设备构想到此特流下载的全部过程。图3所示是基于该平台开发XCV50E的设计流程。该平台的由设计入口工具、设计实现工具、设计验证工具三大部分构成。设计入口工具接收各种图形或文字的设计输入,并最终生成网络表文件。设计实现工具将网络表转化为配置比特流,并下载到器件。设计验证工具用来对设计中的逻辑关系及输出结果进行仿真和时序阻制分析。

对于系统级设计,一般可以使用基于原理图的层次化设计,过程如下:先以系统结构原理图作为顶层图,自上而下的构造基于模块的结构子图,同时自下而上的将结构子图的结构子图,同时自下而上的将结构子图具体体(用VHDL评议或元件互连关系表示出来),

对于系统级设计,一般可以使用基于原理图的层次化设计,过程如下:先以系统结构原理图作为顶层图,自上而下的构造基于模块的结构子图,同时自下而上的将结构子图的结构子图,同时自下而上的将结构子图具体体(用VHDL评议或元件互连关系表示出来),

并对每个模块和子图进行功能性仿零点,以保证每层逻辑关系都是正确进行功能性仿真,以保证每层逻辑关系都是正确的。顶层原理图具体化并完成功能仿真后,再添加必要的输入输出元件,即可合成系统网络表。之后,对系统网络表进行翻译、映射、放置和布线,并利用流程引擎产生的时序信息进行时序仿真和时序分析。然后采用修改入口设计、设置各种属性和限制、调整其片布局等方法完善设计,直到达到设计要求,最后将优化后的配置比特流下载到FPGA芯片中。

3 XCV50E的应用配置

XCV50E芯片是基于静态RAM(SRAM)的FPGA,其配置信息必须固化到另外的可编程ROM(PROM)芯片中。系统加电后,XCV50E芯片首先从PROM中读取配置信息并加载到配置内存中。VirtexE系列芯片中支持四种配置模式,分别为主串行模式、从串行模式、并行模式和边界扫描模式。

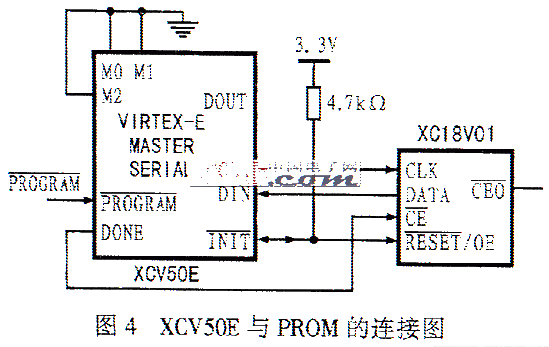

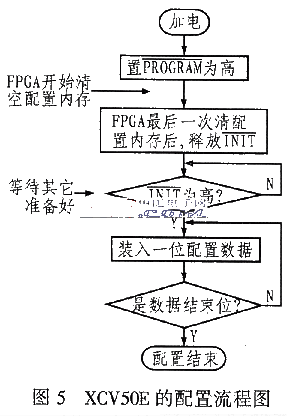

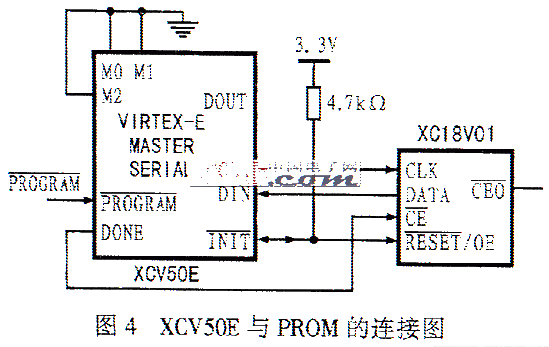

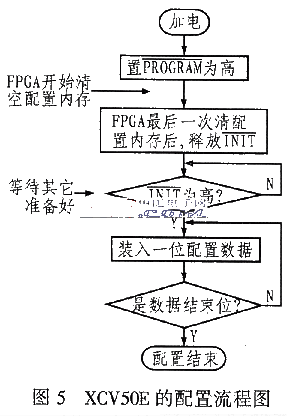

图4是XCV50E在主串行模式的配置电路图。图中配置模式选择位M2、M1、M0均连接到地;PROGRAM为FPGA配置控制信号;FPGA的配置数据输入管脚DIN连接到PROM芯片XC18V01的数据输出脚DATA;初始化指示信号INIT用作XC08V01的复位信号;配置完成信号DONE用作PROM的片选信号。配置过程如下:当系统加电并且PROGRAM首脚升高后,配置过程开始,XCV50E首先进行内部的初始经,初始化完成后,VCV50E释放INIT管脚,并从下一个配置时钟的上升沿开始从PROM中读入配置数据流;全部数据读完后,FPGA发出配置结束信号DONE来关闭PROM,配置过程结束。下一个时钟起,XCV50E运行启动进程,之后就可以按设定的程序工作了。图5给出了XCV50E的配置流程图。

并对每个模块和子图进行功能性仿零点,以保证每层逻辑关系都是正确进行功能性仿真,以保证每层逻辑关系都是正确的。顶层原理图具体化并完成功能仿真后,再添加必要的输入输出元件,即可合成系统网络表。之后,对系统网络表进行翻译、映射、放置和布线,并利用流程引擎产生的时序信息进行时序仿真和时序分析。然后采用修改入口设计、设置各种属性和限制、调整其片布局等方法完善设计,直到达到设计要求,最后将优化后的配置比特流下载到FPGA芯片中。

3 XCV50E的应用配置

XCV50E芯片是基于静态RAM(SRAM)的FPGA,其配置信息必须固化到另外的可编程ROM(PROM)芯片中。系统加电后,XCV50E芯片首先从PROM中读取配置信息并加载到配置内存中。VirtexE系列芯片中支持四种配置模式,分别为主串行模式、从串行模式、并行模式和边界扫描模式。

图4是XCV50E在主串行模式的配置电路图。图中配置模式选择位M2、M1、M0均连接到地;PROGRAM为FPGA配置控制信号;FPGA的配置数据输入管脚DIN连接到PROM芯片XC18V01的数据输出脚DATA;初始化指示信号INIT用作XC08V01的复位信号;配置完成信号DONE用作PROM的片选信号。配置过程如下:当系统加电并且PROGRAM首脚升高后,配置过程开始,XCV50E首先进行内部的初始经,初始化完成后,VCV50E释放INIT管脚,并从下一个配置时钟的上升沿开始从PROM中读入配置数据流;全部数据读完后,FPGA发出配置结束信号DONE来关闭PROM,配置过程结束。下一个时钟起,XCV50E运行启动进程,之后就可以按设定的程序工作了。图5给出了XCV50E的配置流程图。

引用地址:集系统级FPGA芯片XCV50E的结构与开发

主要特性有:1.8V超低核心电压、支持20种高速总线标准、八个全数字延迟锁定环、0.18微米6层金属工艺、支持IEEE 1149.1边界扫描。VirtexE系列FPGA芯片具有卓越的整体性能和高速特性,是实现高速系统级设计的优选芯片。下面以XCV50E为例,介绍VirtexE系列FPGA的结构特性和开发流程。

1 XCV50E芯片的结构

XCV50E芯片主要由四部分组成,其结构图如图1所示,芯片中央是由16%26;#215;24个可编程逻辑块(CLB)构成的CLB阵列,用以实现芯片的主要逻辑功能。芯片中16个4kB的块内存(Block RAM

或BRAM)组成4个块内存槽,位于CLK阵列的两端及接近芯片中心的位置。块内存可用作高速RAM或FIFO。环绕CLB阵列的是叫做VersaRing的布线资源,它连接内部的逻辑信号到输入输出单元。输入输出单元位于芯片周边,用以实现不同标准信号(如LVDS、CMOS、GTL)间的和转换。

1.1 可配置逻辑块

可配置逻辑块是FPGA的核心部分,主要用来实现各种逻辑功能。其内部结构见图2所示。每个可配置逻辑块包括左右两个功能片。每个功能片包括两个逻辑单元。每个逻辑单元由一个四输入查找表(LUT)、一个进位逻辑和一个寄存器组成。查找表可作为函数产生器来使用,也可用作高速16位移位寄存器或16%26;#215;1的随机存取内存(RAM)。为扩展芯片的逻辑功能,在每个功能片中还设有一个F5复选器,在每个逻辑块中设有一个F6复选器,可分别用以实现9输入的函数和19输入的函数。

1.2 通用布线资源

芯片内部与可配置逻辑块阵列相匹配的是通用布线矩阵阵列(GRM)。GRM是开关矩阵,它用足够的连线将对应的可配置逻辑连接到相邻可配置逻辑块和部分远端的可配置逻辑块。芯片内有许多双向长线分别横贯和纵贯整个芯片,利用它们可以快速高效地分配信号。通过通用布线资源,各个可配置逻辑块和块内存构成了一个高速动作的统一整体。

图2

1.3 VersaRing布线资源

VersaRing环绕着芯片中央的CLB阵列,它将阵列信号与芯片I/O管脚相连。VersaRing以毫微秒级的速度将任一内部逻辑信号连接到芯片的任一I/O管脚。正是由于XCV50E这种信号分配的任意性,使得XCV50E的设计工作可以与电路板制版并行进行,从而大大缩短了开发周期。

1.4 延迟锁存环(DLL)

芯片内有八个延迟锁定环,借助它们可以实现高速零时延的时钟信号,延迟锁定环的输入时钟范围是25MHz"350MHz,输出时钟的传输时延为零,边沿抖动小于60ps。锁定环可对时钟进行二倍频或2"16倍分频,并可进行90o、180o、270o的移相操作。使用延迟锁定环可有效解决高速应用中信号的时滞和抖动问题。

主要特性有:1.8V超低核心电压、支持20种高速总线标准、八个全数字延迟锁定环、0.18微米6层金属工艺、支持IEEE 1149.1边界扫描。VirtexE系列FPGA芯片具有卓越的整体性能和高速特性,是实现高速系统级设计的优选芯片。下面以XCV50E为例,介绍VirtexE系列FPGA的结构特性和开发流程。

1 XCV50E芯片的结构

XCV50E芯片主要由四部分组成,其结构图如图1所示,芯片中央是由16%26;#215;24个可编程逻辑块(CLB)构成的CLB阵列,用以实现芯片的主要逻辑功能。芯片中16个4kB的块内存(Block RAM

或BRAM)组成4个块内存槽,位于CLK阵列的两端及接近芯片中心的位置。块内存可用作高速RAM或FIFO。环绕CLB阵列的是叫做VersaRing的布线资源,它连接内部的逻辑信号到输入输出单元。输入输出单元位于芯片周边,用以实现不同标准信号(如LVDS、CMOS、GTL)间的和转换。

1.1 可配置逻辑块

可配置逻辑块是FPGA的核心部分,主要用来实现各种逻辑功能。其内部结构见图2所示。每个可配置逻辑块包括左右两个功能片。每个功能片包括两个逻辑单元。每个逻辑单元由一个四输入查找表(LUT)、一个进位逻辑和一个寄存器组成。查找表可作为函数产生器来使用,也可用作高速16位移位寄存器或16%26;#215;1的随机存取内存(RAM)。为扩展芯片的逻辑功能,在每个功能片中还设有一个F5复选器,在每个逻辑块中设有一个F6复选器,可分别用以实现9输入的函数和19输入的函数。

1.2 通用布线资源

芯片内部与可配置逻辑块阵列相匹配的是通用布线矩阵阵列(GRM)。GRM是开关矩阵,它用足够的连线将对应的可配置逻辑连接到相邻可配置逻辑块和部分远端的可配置逻辑块。芯片内有许多双向长线分别横贯和纵贯整个芯片,利用它们可以快速高效地分配信号。通过通用布线资源,各个可配置逻辑块和块内存构成了一个高速动作的统一整体。

图2

1.3 VersaRing布线资源

VersaRing环绕着芯片中央的CLB阵列,它将阵列信号与芯片I/O管脚相连。VersaRing以毫微秒级的速度将任一内部逻辑信号连接到芯片的任一I/O管脚。正是由于XCV50E这种信号分配的任意性,使得XCV50E的设计工作可以与电路板制版并行进行,从而大大缩短了开发周期。

1.4 延迟锁存环(DLL)

芯片内有八个延迟锁定环,借助它们可以实现高速零时延的时钟信号,延迟锁定环的输入时钟范围是25MHz"350MHz,输出时钟的传输时延为零,边沿抖动小于60ps。锁定环可对时钟进行二倍频或2"16倍分频,并可进行90o、180o、270o的移相操作。使用延迟锁定环可有效解决高速应用中信号的时滞和抖动问题。

2 XCV50E的开发

笔者使用Xilin Foundation F4.1来开发

XCV50E芯片。Xilin Foundation F4.1是Xilinx公司主要的FPGA芯片开发平台之一。基于该平台可实现XCV50E芯片从设备构想到此特流下载的全部过程。图3所示是基于该平台开发XCV50E的设计流程。该平台的由设计入口工具、设计实现工具、设计验证工具三大部分构成。设计入口工具接收各种图形或文字的设计输入,并最终生成网络表文件。设计实现工具将网络表转化为配置比特流,并下载到器件。设计验证工具用来对设计中的逻辑关系及输出结果进行仿真和时序阻制分析。

2 XCV50E的开发

笔者使用Xilin Foundation F4.1来开发

XCV50E芯片。Xilin Foundation F4.1是Xilinx公司主要的FPGA芯片开发平台之一。基于该平台可实现XCV50E芯片从设备构想到此特流下载的全部过程。图3所示是基于该平台开发XCV50E的设计流程。该平台的由设计入口工具、设计实现工具、设计验证工具三大部分构成。设计入口工具接收各种图形或文字的设计输入,并最终生成网络表文件。设计实现工具将网络表转化为配置比特流,并下载到器件。设计验证工具用来对设计中的逻辑关系及输出结果进行仿真和时序阻制分析。

对于系统级设计,一般可以使用基于原理图的层次化设计,过程如下:先以系统结构原理图作为顶层图,自上而下的构造基于模块的结构子图,同时自下而上的将结构子图的结构子图,同时自下而上的将结构子图具体体(用VHDL评议或元件互连关系表示出来),

对于系统级设计,一般可以使用基于原理图的层次化设计,过程如下:先以系统结构原理图作为顶层图,自上而下的构造基于模块的结构子图,同时自下而上的将结构子图的结构子图,同时自下而上的将结构子图具体体(用VHDL评议或元件互连关系表示出来),

并对每个模块和子图进行功能性仿零点,以保证每层逻辑关系都是正确进行功能性仿真,以保证每层逻辑关系都是正确的。顶层原理图具体化并完成功能仿真后,再添加必要的输入输出元件,即可合成系统网络表。之后,对系统网络表进行翻译、映射、放置和布线,并利用流程引擎产生的时序信息进行时序仿真和时序分析。然后采用修改入口设计、设置各种属性和限制、调整其片布局等方法完善设计,直到达到设计要求,最后将优化后的配置比特流下载到FPGA芯片中。

3 XCV50E的应用配置

XCV50E芯片是基于静态RAM(SRAM)的FPGA,其配置信息必须固化到另外的可编程ROM(PROM)芯片中。系统加电后,XCV50E芯片首先从PROM中读取配置信息并加载到配置内存中。VirtexE系列芯片中支持四种配置模式,分别为主串行模式、从串行模式、并行模式和边界扫描模式。

图4是XCV50E在主串行模式的配置电路图。图中配置模式选择位M2、M1、M0均连接到地;PROGRAM为FPGA配置控制信号;FPGA的配置数据输入管脚DIN连接到PROM芯片XC18V01的数据输出脚DATA;初始化指示信号INIT用作XC08V01的复位信号;配置完成信号DONE用作PROM的片选信号。配置过程如下:当系统加电并且PROGRAM首脚升高后,配置过程开始,XCV50E首先进行内部的初始经,初始化完成后,VCV50E释放INIT管脚,并从下一个配置时钟的上升沿开始从PROM中读入配置数据流;全部数据读完后,FPGA发出配置结束信号DONE来关闭PROM,配置过程结束。下一个时钟起,XCV50E运行启动进程,之后就可以按设定的程序工作了。图5给出了XCV50E的配置流程图。

并对每个模块和子图进行功能性仿零点,以保证每层逻辑关系都是正确进行功能性仿真,以保证每层逻辑关系都是正确的。顶层原理图具体化并完成功能仿真后,再添加必要的输入输出元件,即可合成系统网络表。之后,对系统网络表进行翻译、映射、放置和布线,并利用流程引擎产生的时序信息进行时序仿真和时序分析。然后采用修改入口设计、设置各种属性和限制、调整其片布局等方法完善设计,直到达到设计要求,最后将优化后的配置比特流下载到FPGA芯片中。

3 XCV50E的应用配置

XCV50E芯片是基于静态RAM(SRAM)的FPGA,其配置信息必须固化到另外的可编程ROM(PROM)芯片中。系统加电后,XCV50E芯片首先从PROM中读取配置信息并加载到配置内存中。VirtexE系列芯片中支持四种配置模式,分别为主串行模式、从串行模式、并行模式和边界扫描模式。

图4是XCV50E在主串行模式的配置电路图。图中配置模式选择位M2、M1、M0均连接到地;PROGRAM为FPGA配置控制信号;FPGA的配置数据输入管脚DIN连接到PROM芯片XC18V01的数据输出脚DATA;初始化指示信号INIT用作XC08V01的复位信号;配置完成信号DONE用作PROM的片选信号。配置过程如下:当系统加电并且PROGRAM首脚升高后,配置过程开始,XCV50E首先进行内部的初始经,初始化完成后,VCV50E释放INIT管脚,并从下一个配置时钟的上升沿开始从PROM中读入配置数据流;全部数据读完后,FPGA发出配置结束信号DONE来关闭PROM,配置过程结束。下一个时钟起,XCV50E运行启动进程,之后就可以按设定的程序工作了。图5给出了XCV50E的配置流程图。

上一篇:使用Verilog实现基于FPGA的SDRAM控制器

下一篇:基于FPGA的四阶IIR数字滤波器

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 EL5420TILZ-T7

EL5420TILZ-T7

京公网安备 11010802033920号

京公网安备 11010802033920号