摘要:介绍了基于可编程逻辑器件CPLD和直接数字频率合成技术(DDS)的三相多波形函数发生器的基本原理,并在此基础上给出了基于CPLD的各模块设计方法及其VHDL源程序。

关键词:CPLD;直接数字频率合成;函数发生器;VHDL

1 引言

直接数字频率合成 Direct Digital Synthesis ,DDS是20世纪60年代末出现的第三代频率合成技术。该技术从相位概念出发,以Nyquist时域采样定理为基础,在时域中进行频率合成。DDS频率转换速度快,频率分辨率高,并在频率转换时可保持相位的连续,因而易于实现多种调制功能。DDS是全数字化技术,其幅度、相位、频率均可实现程控,并可通过更换波形数据灵活实现任意波形。此外,DDS易于单片集成,体积小,价格低,功耗小,因此DDS技术近年来得到了飞速发展,其应用也越来越广泛。

基于CPLD和DDS技术的函数发生器可以实现信号波形的多样化,而且方便可靠,简单经济,系统易于扩展,同时可大大提高输出信号的带宽。

2 系统原理

2.1 CPLD内部设计

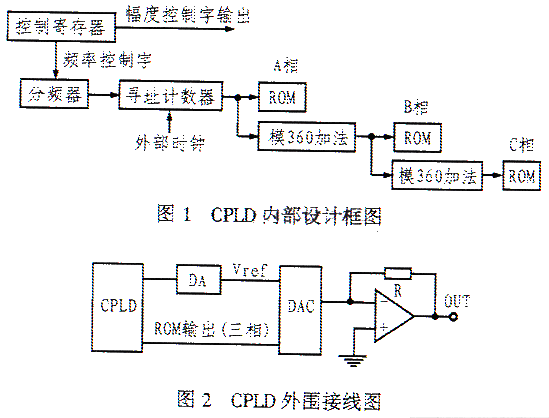

CPLD的内部结构框图如图1所示,图中,首先由控制寄存器将外部控制器(如单片机)送入的数据转换为频率和幅度控制字;然后再由分频器根据频率控制字进行分频并将输出作为寻址计数器的时钟;寻址计数器的寻址空间为360字节,可对ROM中的查找表进行寻址;而通过模360加法器可以产生120%26;#176;的相位差。

2.2 CPLD的外围电路

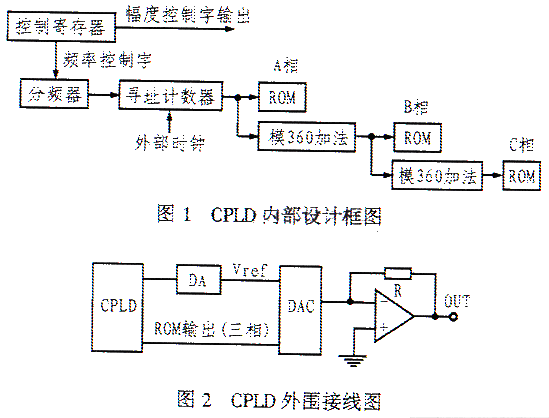

图2所示是CPLD的外围电路连接图。图中,CPLD幅度控制字经D/A转换输出后,可作为查找表输出DAC的参考电压,该参考电压可通过改变幅度控制字来进行改变,从而改变输出信号的幅度。

3 CPLD各模块的设计

3.1 控制寄存器的设计

控制寄存器设计主要是将外部控制器输入的数据转换为频率和幅度控制字。其程序代码如下:

--////////////调库////////////--

entity controller is

port(clk:in std_logic;

datain:in std_logic;

ad:out std_logic_vector(16 down to 0);

freq:out std_logic_ vector(16 down to 0));

end;

architecture dataflow of controller is

signal out1:std_logic_vector(16 down to 0);

begin

s2p:process(clk,datain)

variable temp:std_logic_vector(16 down to 0);

begin

if clk'event and clk=‘1’ then

temp:=temp(15 down to 0)&datain;

end if;

out1<=temp;

end process s2p;

mux:process(out1(16))

begin

if out1(16)=‘1’ then

ad<=out1(15 down to 0); --1号寄存器为幅度控制字

else

freq<=out1(15 downto 0); --0号寄存器为频率控制字

end if;

end process mux;

end;

图3

3.2 分频比可变的分频器模块设计

该设计主要是根据频率控制字决定分频倍数,从而输出与频率控制字相对应的频率时钟,此模块的输出可作为寻址计数器的时钟。具体代码如下:

processclk --clk为外部时钟(如晶振)

variable temp,fen:std_logic_vector(15 down to 0);

constant temp1:std_logic_vector(15 down to 0):=“1111111111111111”;

variable a:std_logic;

begin

fen:=temp1-fen_in; --使分频后的频率正比于频率控制字

if clk=‘1’ and clk'event then

if temp=(‘0’&fen(15 down to 1)) then --相当于除2运算

a:=not a;

temp:=temp+1;

elsif temp=fen then

a:=not a;

temp:=“0000000000000000”;

else

temp:=temp+1;

end if;

end if;

fen out<=a; --fen out 为输入时钟的频率fen倍分频

end process;

3.3 寻址计数器设计

寻址计数器主要用于产生对ROM寻址输出波形数据的寻址信号,寻址空间为360字节,具体的程序代码如下:

process(clk)

variable temp:integer range 0 to 359;

begin

if clk=‘1' and clk'event then

if temp<359 then

temp:=temp+1;

else

temp:=0;

end if;

end if;

adress<=temp;

end process;

3.4 模360加法器设计

此模块用来产生120%26;#176;的相移,以形成三相相差为120%26;#176;的输出波形。由于寻址空间为360字节,故在输出寻址数大于360时,须对360取模。程序如下:

process(adress_in)

variable tempinteger range 0 to 511;

begin

temp:=adress in+120;--相移120%26;#176;

if temp<360 then;

adress out<=temp

else

adress_out<=temp-360;--综合工具不支持取模运算,故采用减法器来实现

end if;

end process;

3.5 查找表ROM设计

此模块主要用于存储各种波形数据,以便通过寻址计数器寻址输出并经D/A转换来输出各种波形,其中包括正弦波、三角波、方波以及锯齿波。代码如下:

process(adress,sel)

begin

if sel=“00” then --sel为波形选择端口,选择输出波形,00为正弦波

case adress is

when 000=>data<=0; when 001=>data<=4; ......--正弦波查找表

when others=>null;

end case;

else if sel=“01” then --01输出方波,

if adress<180 then

data<=255;

else

data<=0;

end if;

else if sel=“10” then --锯齿波

data<=adress/2;

else --三角波

if adress<180 then

data<=adress;

else

data<=adress-180;

end if;

end if;

end process;

由以上各模块组成的三相波形发生器原理图如图3所示。

4 结束语

此方案可以方便地输出多种三相波形,而且,由于CPLD具有可编程重置特性,因而可以方便地改变控制方式或更换波形数据,而且简单易行,易于系统升级,同时具有很高的性价比。

2.2 CPLD的外围电路

图2所示是CPLD的外围电路连接图。图中,CPLD幅度控制字经D/A转换输出后,可作为查找表输出DAC的参考电压,该参考电压可通过改变幅度控制字来进行改变,从而改变输出信号的幅度。

3 CPLD各模块的设计

3.1 控制寄存器的设计

控制寄存器设计主要是将外部控制器输入的数据转换为频率和幅度控制字。其程序代码如下:

--////////////调库////////////--

entity controller is

port(clk:in std_logic;

datain:in std_logic;

ad:out std_logic_vector(16 down to 0);

freq:out std_logic_ vector(16 down to 0));

end;

architecture dataflow of controller is

signal out1:std_logic_vector(16 down to 0);

begin

s2p:process(clk,datain)

variable temp:std_logic_vector(16 down to 0);

begin

if clk'event and clk=‘1’ then

temp:=temp(15 down to 0)&datain;

end if;

out1<=temp;

end process s2p;

mux:process(out1(16))

begin

if out1(16)=‘1’ then

ad<=out1(15 down to 0); --1号寄存器为幅度控制字

else

freq<=out1(15 downto 0); --0号寄存器为频率控制字

end if;

end process mux;

end;

图3

3.2 分频比可变的分频器模块设计

该设计主要是根据频率控制字决定分频倍数,从而输出与频率控制字相对应的频率时钟,此模块的输出可作为寻址计数器的时钟。具体代码如下:

processclk --clk为外部时钟(如晶振)

variable temp,fen:std_logic_vector(15 down to 0);

constant temp1:std_logic_vector(15 down to 0):=“1111111111111111”;

variable a:std_logic;

begin

fen:=temp1-fen_in; --使分频后的频率正比于频率控制字

if clk=‘1’ and clk'event then

if temp=(‘0’&fen(15 down to 1)) then --相当于除2运算

a:=not a;

temp:=temp+1;

elsif temp=fen then

a:=not a;

temp:=“0000000000000000”;

else

temp:=temp+1;

end if;

end if;

fen out<=a; --fen out 为输入时钟的频率fen倍分频

end process;

3.3 寻址计数器设计

寻址计数器主要用于产生对ROM寻址输出波形数据的寻址信号,寻址空间为360字节,具体的程序代码如下:

process(clk)

variable temp:integer range 0 to 359;

begin

if clk=‘1' and clk'event then

if temp<359 then

temp:=temp+1;

else

temp:=0;

end if;

end if;

adress<=temp;

end process;

3.4 模360加法器设计

此模块用来产生120%26;#176;的相移,以形成三相相差为120%26;#176;的输出波形。由于寻址空间为360字节,故在输出寻址数大于360时,须对360取模。程序如下:

process(adress_in)

variable tempinteger range 0 to 511;

begin

temp:=adress in+120;--相移120%26;#176;

if temp<360 then;

adress out<=temp

else

adress_out<=temp-360;--综合工具不支持取模运算,故采用减法器来实现

end if;

end process;

3.5 查找表ROM设计

此模块主要用于存储各种波形数据,以便通过寻址计数器寻址输出并经D/A转换来输出各种波形,其中包括正弦波、三角波、方波以及锯齿波。代码如下:

process(adress,sel)

begin

if sel=“00” then --sel为波形选择端口,选择输出波形,00为正弦波

case adress is

when 000=>data<=0; when 001=>data<=4; ......--正弦波查找表

when others=>null;

end case;

else if sel=“01” then --01输出方波,

if adress<180 then

data<=255;

else

data<=0;

end if;

else if sel=“10” then --锯齿波

data<=adress/2;

else --三角波

if adress<180 then

data<=adress;

else

data<=adress-180;

end if;

end if;

end process;

由以上各模块组成的三相波形发生器原理图如图3所示。

4 结束语

此方案可以方便地输出多种三相波形,而且,由于CPLD具有可编程重置特性,因而可以方便地改变控制方式或更换波形数据,而且简单易行,易于系统升级,同时具有很高的性价比。

引用地址:基于CPLD的三相多波形函数发生器设计

2.2 CPLD的外围电路

图2所示是CPLD的外围电路连接图。图中,CPLD幅度控制字经D/A转换输出后,可作为查找表输出DAC的参考电压,该参考电压可通过改变幅度控制字来进行改变,从而改变输出信号的幅度。

3 CPLD各模块的设计

3.1 控制寄存器的设计

控制寄存器设计主要是将外部控制器输入的数据转换为频率和幅度控制字。其程序代码如下:

--////////////调库////////////--

entity controller is

port(clk:in std_logic;

datain:in std_logic;

ad:out std_logic_vector(16 down to 0);

freq:out std_logic_ vector(16 down to 0));

end;

architecture dataflow of controller is

signal out1:std_logic_vector(16 down to 0);

begin

s2p:process(clk,datain)

variable temp:std_logic_vector(16 down to 0);

begin

if clk'event and clk=‘1’ then

temp:=temp(15 down to 0)&datain;

end if;

out1<=temp;

end process s2p;

mux:process(out1(16))

begin

if out1(16)=‘1’ then

ad<=out1(15 down to 0); --1号寄存器为幅度控制字

else

freq<=out1(15 downto 0); --0号寄存器为频率控制字

end if;

end process mux;

end;

图3

3.2 分频比可变的分频器模块设计

该设计主要是根据频率控制字决定分频倍数,从而输出与频率控制字相对应的频率时钟,此模块的输出可作为寻址计数器的时钟。具体代码如下:

processclk --clk为外部时钟(如晶振)

variable temp,fen:std_logic_vector(15 down to 0);

constant temp1:std_logic_vector(15 down to 0):=“1111111111111111”;

variable a:std_logic;

begin

fen:=temp1-fen_in; --使分频后的频率正比于频率控制字

if clk=‘1’ and clk'event then

if temp=(‘0’&fen(15 down to 1)) then --相当于除2运算

a:=not a;

temp:=temp+1;

elsif temp=fen then

a:=not a;

temp:=“0000000000000000”;

else

temp:=temp+1;

end if;

end if;

fen out<=a; --fen out 为输入时钟的频率fen倍分频

end process;

3.3 寻址计数器设计

寻址计数器主要用于产生对ROM寻址输出波形数据的寻址信号,寻址空间为360字节,具体的程序代码如下:

process(clk)

variable temp:integer range 0 to 359;

begin

if clk=‘1' and clk'event then

if temp<359 then

temp:=temp+1;

else

temp:=0;

end if;

end if;

adress<=temp;

end process;

3.4 模360加法器设计

此模块用来产生120%26;#176;的相移,以形成三相相差为120%26;#176;的输出波形。由于寻址空间为360字节,故在输出寻址数大于360时,须对360取模。程序如下:

process(adress_in)

variable tempinteger range 0 to 511;

begin

temp:=adress in+120;--相移120%26;#176;

if temp<360 then;

adress out<=temp

else

adress_out<=temp-360;--综合工具不支持取模运算,故采用减法器来实现

end if;

end process;

3.5 查找表ROM设计

此模块主要用于存储各种波形数据,以便通过寻址计数器寻址输出并经D/A转换来输出各种波形,其中包括正弦波、三角波、方波以及锯齿波。代码如下:

process(adress,sel)

begin

if sel=“00” then --sel为波形选择端口,选择输出波形,00为正弦波

case adress is

when 000=>data<=0; when 001=>data<=4; ......--正弦波查找表

when others=>null;

end case;

else if sel=“01” then --01输出方波,

if adress<180 then

data<=255;

else

data<=0;

end if;

else if sel=“10” then --锯齿波

data<=adress/2;

else --三角波

if adress<180 then

data<=adress;

else

data<=adress-180;

end if;

end if;

end process;

由以上各模块组成的三相波形发生器原理图如图3所示。

4 结束语

此方案可以方便地输出多种三相波形,而且,由于CPLD具有可编程重置特性,因而可以方便地改变控制方式或更换波形数据,而且简单易行,易于系统升级,同时具有很高的性价比。

2.2 CPLD的外围电路

图2所示是CPLD的外围电路连接图。图中,CPLD幅度控制字经D/A转换输出后,可作为查找表输出DAC的参考电压,该参考电压可通过改变幅度控制字来进行改变,从而改变输出信号的幅度。

3 CPLD各模块的设计

3.1 控制寄存器的设计

控制寄存器设计主要是将外部控制器输入的数据转换为频率和幅度控制字。其程序代码如下:

--////////////调库////////////--

entity controller is

port(clk:in std_logic;

datain:in std_logic;

ad:out std_logic_vector(16 down to 0);

freq:out std_logic_ vector(16 down to 0));

end;

architecture dataflow of controller is

signal out1:std_logic_vector(16 down to 0);

begin

s2p:process(clk,datain)

variable temp:std_logic_vector(16 down to 0);

begin

if clk'event and clk=‘1’ then

temp:=temp(15 down to 0)&datain;

end if;

out1<=temp;

end process s2p;

mux:process(out1(16))

begin

if out1(16)=‘1’ then

ad<=out1(15 down to 0); --1号寄存器为幅度控制字

else

freq<=out1(15 downto 0); --0号寄存器为频率控制字

end if;

end process mux;

end;

图3

3.2 分频比可变的分频器模块设计

该设计主要是根据频率控制字决定分频倍数,从而输出与频率控制字相对应的频率时钟,此模块的输出可作为寻址计数器的时钟。具体代码如下:

processclk --clk为外部时钟(如晶振)

variable temp,fen:std_logic_vector(15 down to 0);

constant temp1:std_logic_vector(15 down to 0):=“1111111111111111”;

variable a:std_logic;

begin

fen:=temp1-fen_in; --使分频后的频率正比于频率控制字

if clk=‘1’ and clk'event then

if temp=(‘0’&fen(15 down to 1)) then --相当于除2运算

a:=not a;

temp:=temp+1;

elsif temp=fen then

a:=not a;

temp:=“0000000000000000”;

else

temp:=temp+1;

end if;

end if;

fen out<=a; --fen out 为输入时钟的频率fen倍分频

end process;

3.3 寻址计数器设计

寻址计数器主要用于产生对ROM寻址输出波形数据的寻址信号,寻址空间为360字节,具体的程序代码如下:

process(clk)

variable temp:integer range 0 to 359;

begin

if clk=‘1' and clk'event then

if temp<359 then

temp:=temp+1;

else

temp:=0;

end if;

end if;

adress<=temp;

end process;

3.4 模360加法器设计

此模块用来产生120%26;#176;的相移,以形成三相相差为120%26;#176;的输出波形。由于寻址空间为360字节,故在输出寻址数大于360时,须对360取模。程序如下:

process(adress_in)

variable tempinteger range 0 to 511;

begin

temp:=adress in+120;--相移120%26;#176;

if temp<360 then;

adress out<=temp

else

adress_out<=temp-360;--综合工具不支持取模运算,故采用减法器来实现

end if;

end process;

3.5 查找表ROM设计

此模块主要用于存储各种波形数据,以便通过寻址计数器寻址输出并经D/A转换来输出各种波形,其中包括正弦波、三角波、方波以及锯齿波。代码如下:

process(adress,sel)

begin

if sel=“00” then --sel为波形选择端口,选择输出波形,00为正弦波

case adress is

when 000=>data<=0; when 001=>data<=4; ......--正弦波查找表

when others=>null;

end case;

else if sel=“01” then --01输出方波,

if adress<180 then

data<=255;

else

data<=0;

end if;

else if sel=“10” then --锯齿波

data<=adress/2;

else --三角波

if adress<180 then

data<=adress;

else

data<=adress-180;

end if;

end if;

end process;

由以上各模块组成的三相波形发生器原理图如图3所示。

4 结束语

此方案可以方便地输出多种三相波形,而且,由于CPLD具有可编程重置特性,因而可以方便地改变控制方式或更换波形数据,而且简单易行,易于系统升级,同时具有很高的性价比。

上一篇:基于CPLD/FPGA的出租车计费器

下一篇:基于FPGA的超高速雷达住处实时采集存储系统

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新应用文章

更多精选电路图

更多热门文章

更多每日新闻

- 芯启源(上海)将持续发力,“做深做精”EDA及IP产品

- 本田严厉警告日产:若与鸿海合作,那么本田与日产的合作将终止

- Microchip推出新款交钥匙电容式触摸控制器产品 MTCH2120

- Matter对AIoT的意义:连接AIoT设备开发人员指南

- 我国科学家建立生成式模型为医学AI训练提供技术支持

- Diodes 推出符合车用标准的电流分流监测器,通过高精度电压感测快速检测系统故障

- Power Integrations面向800V汽车应用推出新型宽爬电距离开关IC

- 打破台积电垄断!联电夺下高通先进封装订单

- Ampere 年度展望:2025年重塑IT格局的四大关键趋势

- 存储巨头铠侠正式挂牌上市:首日股价上涨超10%

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 SE521F

SE521F

京公网安备 11010802033920号

京公网安备 11010802033920号