摘要:介绍了声纳脉冲侦察模块的测向测距原理、硬件设计及其实现。声纳脉冲侦察模块硬件电路以数字信号处理器为核心,通过可编程门阵列实现逻辑控制,再配以适当的片外存储器及其它外围电路,从而构成一个嵌入式系统。通过对设计需求的分析,提出了设计思路,给出了设计的具体方案。本模块已通过各项指标测试,工作稳定、性能优良。

关键词:声纳脉冲侦察 测向测距 数字信号处理器 可编程门阵列

测定水下以及水面目标的位置是块纳系统的重要任务,目标的位置由目标的弦角(或方位角)和距离决定。声纳脉冲侦察模块作为声纳侦察系统的一部分,担负着测向和测距的任务。声纳脉冲侦察模块通过测定三路信号的时延差以及时延差的差来测定目标的方位和距离。

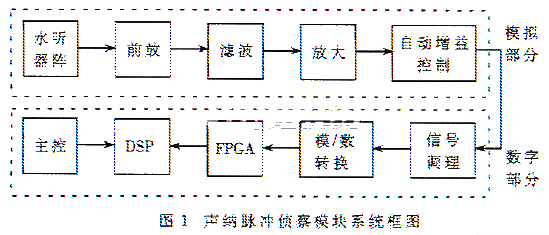

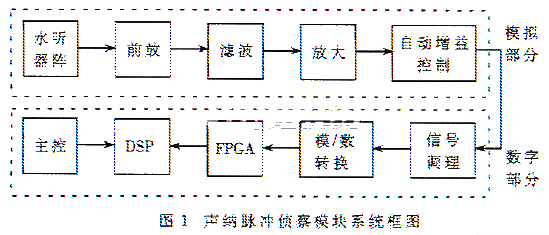

随着电子技术的发展,水声设备也加速了更新换代的步伐。水声设备的发展方向应该是现代化、小型化、智能化,一些原来用硬件实现的功能可以由软件来完成,这为功能的更新和发展提供了极大的便利。正是顺应这一趋势,作者结合实际进行了声纳脉冲模块的改造。如图1所示,声纳脉冲侦察模块可以分为两大部分:模拟冲毁和数字部分。现只就声纳脉冲侦察模块数字部分的设计进行阐述。下面介绍声纳脉冲侦察模块的测向测距原理、硬件设计及其实现。

1 声纳脉冲侦察模块测向测距原理

目前,被动测距声纳主要有两种类型:共形阵和拖曳式线列阵,它们都是直线阵。共形阵在舰艇壳体上配置三对(左、右舷侧各三个)子阵。阵元的布放可分为对称阵和非对称阵。对称阵的三个阵元在直线上等间距布放,非对称阵的三个阵元的间距之比是1:2。对于三元阵来说,对称阵和非对称阵的测向、测距原理是相同的。由于阵型的差异,非对称阵和对称阵在测距计算、距离模糊的范围、时延测量误差对测距误差的影响等方面也存在差异。

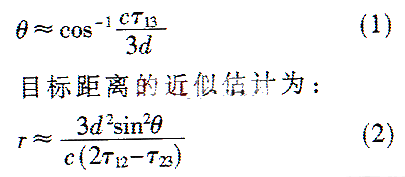

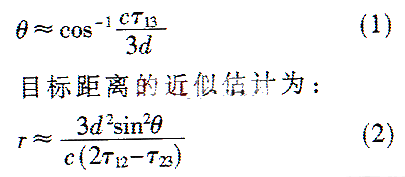

下面以非对称阵为例给出测向测距原理。如图2所示,设三元非对称阵首中阵元的间距为d,目标方向角为θ目标到各阵元的距离分别为r1、r2、r3,其中,r2为要测定的目标距离r。

在极坐标系中,设目标的坐丁二烯为S(r, θ),三个阵元的坐标分别为1:(d,0),2:(0,0),3:(2d, π),声速为c,目标信号到达各个阵元的时延差分别为τ12、τ23、τ13。其中,τ12表示阵元1、2接收信号的时间差,τ23表示阵元2、3接收信号的时间差,阵元1、3接收信号的时间差τ13为τ12和τ23两者之和。稍加分析和推导可得到在远场的目标方位的近似公式为:

1 声纳脉冲侦察模块测向测距原理

目前,被动测距声纳主要有两种类型:共形阵和拖曳式线列阵,它们都是直线阵。共形阵在舰艇壳体上配置三对(左、右舷侧各三个)子阵。阵元的布放可分为对称阵和非对称阵。对称阵的三个阵元在直线上等间距布放,非对称阵的三个阵元的间距之比是1:2。对于三元阵来说,对称阵和非对称阵的测向、测距原理是相同的。由于阵型的差异,非对称阵和对称阵在测距计算、距离模糊的范围、时延测量误差对测距误差的影响等方面也存在差异。

下面以非对称阵为例给出测向测距原理。如图2所示,设三元非对称阵首中阵元的间距为d,目标方向角为θ目标到各阵元的距离分别为r1、r2、r3,其中,r2为要测定的目标距离r。

在极坐标系中,设目标的坐丁二烯为S(r, θ),三个阵元的坐标分别为1:(d,0),2:(0,0),3:(2d, π),声速为c,目标信号到达各个阵元的时延差分别为τ12、τ23、τ13。其中,τ12表示阵元1、2接收信号的时间差,τ23表示阵元2、3接收信号的时间差,阵元1、3接收信号的时间差τ13为τ12和τ23两者之和。稍加分析和推导可得到在远场的目标方位的近似公式为:

2 设计需求分析

2.1 声纳脉冲侦察模块的主要任务

声纳脉冲侦察模块需要完成的任务主要为:在搜索状态下实时检测声纳脉冲的到达,并快速测量声纳脉冲的频率和目标的方位;在跟踪状态下,进一步解算出目标的距离以及声纳脉冲的重复周期,给出置信度。

2.2 输入输出接口

声纳脉冲模块的输入信号包括:左右舷的艏、舯、艉共六路已放大滤波的阵元信号;存储在EPROM中的阵长、水听器阵基线和舰艇的艏艉线之间的夹角和误差修正表;实时测得的水中声音的传播速度;跟踪命令。输出信息包括:搜索状态和跟踪状态显示信息;解算出的频率、方位、距离等数据;故障自检结果。

2 设计需求分析

2.1 声纳脉冲侦察模块的主要任务

声纳脉冲侦察模块需要完成的任务主要为:在搜索状态下实时检测声纳脉冲的到达,并快速测量声纳脉冲的频率和目标的方位;在跟踪状态下,进一步解算出目标的距离以及声纳脉冲的重复周期,给出置信度。

2.2 输入输出接口

声纳脉冲模块的输入信号包括:左右舷的艏、舯、艉共六路已放大滤波的阵元信号;存储在EPROM中的阵长、水听器阵基线和舰艇的艏艉线之间的夹角和误差修正表;实时测得的水中声音的传播速度;跟踪命令。输出信息包括:搜索状态和跟踪状态显示信息;解算出的频率、方位、距离等数据;故障自检结果。

2.3 软件对硬件的要求

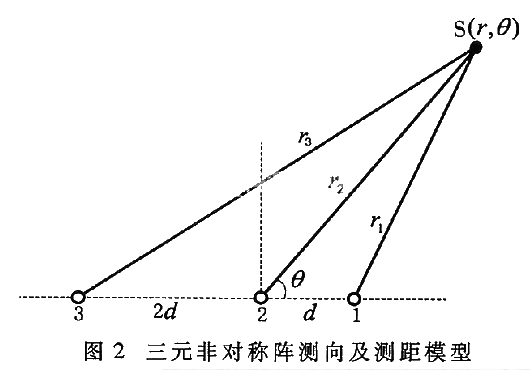

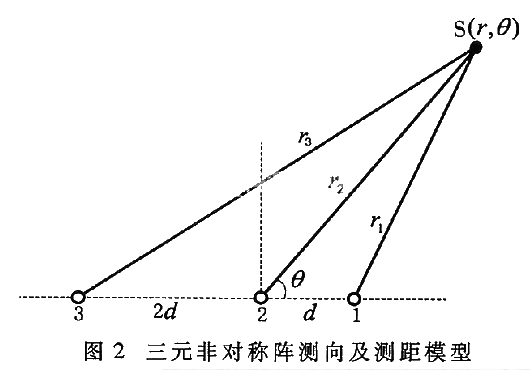

按照侦察模块功能要求,系统软件的工作主要由三个进程构成,如图3所示。系统平时工作在实时检测进程;一旦检测到声纳脉冲,系统就进入数据存储进程,将由模/数转换器输入的数据存入存储器;完成数据存储之后进行数据解算进程,解算之后的结果输出给显控台,然后重新进入检测进程。上述过程将一直循环往复。

2.3.1 实时检测计算量

在实时检测进程中,外部六路阵元输入信号由模/数转换器进行同步并行采样。根据系统要求,每路采样频率为1MHz。数字信号处理器在进行实时检测时要对数据进行降采样处理,使采样频率降为100kHz。数字信号处理器对其中的四路信号(左右舷的艏艉通道)进行实时自适应线谱增强(ALE)运算,以检测声纳脉冲。根据算法分析,计算单路ALE约需要300个指令周期,四通道共需1200个指令周期,若采样频率为100kHz,则数字信号处理器的运算能力应大于120MIPS。

2.3.2 数据存储器

当检测到信号时,数字信号处理器开始将六路数据中的三路(左舷或右舷的艏、舯、艉阵元)存入数据存储器中。存储单元的大小是由解算所需的最大数据量、系统的采样速率、三路信号间的最大延时等因素决定的。假设阵长D=45m,取声速c=1500m/s,则在%26;#177;60%26;#176;扇面内,艏艉阵元之间信号到达的最大延时为:

Dsin60%26;#176;≈26(ms) (3)

若系统的采样速率为1MSPS,系统解算数据至少需要30ms长的样本,则在数据存储过程中至少要存储的数据量(从信号到达时刻算起)为:

(26ms+30ms)%26;#215;3%26;#215;1MSPS=168Kword (4)

2.3.3 数据解算运算量

数据存储完毕后,数字信号处理器开始进行参数的解算。解算内容主要包括:粗测时延、频率估计、相位估计、目标跟踪关联等。数字信号处理器在解算过程中不再响应外部的中断,此时是系统工作的盲区。根据声纳使用要求,这个盲区越小越好,这意味着主处理器的运算速度越大越好。据粗略估计,若要求盲区为100毫秒,则160MHz的处理器是能够完成任务的。

2.3 软件对硬件的要求

按照侦察模块功能要求,系统软件的工作主要由三个进程构成,如图3所示。系统平时工作在实时检测进程;一旦检测到声纳脉冲,系统就进入数据存储进程,将由模/数转换器输入的数据存入存储器;完成数据存储之后进行数据解算进程,解算之后的结果输出给显控台,然后重新进入检测进程。上述过程将一直循环往复。

2.3.1 实时检测计算量

在实时检测进程中,外部六路阵元输入信号由模/数转换器进行同步并行采样。根据系统要求,每路采样频率为1MHz。数字信号处理器在进行实时检测时要对数据进行降采样处理,使采样频率降为100kHz。数字信号处理器对其中的四路信号(左右舷的艏艉通道)进行实时自适应线谱增强(ALE)运算,以检测声纳脉冲。根据算法分析,计算单路ALE约需要300个指令周期,四通道共需1200个指令周期,若采样频率为100kHz,则数字信号处理器的运算能力应大于120MIPS。

2.3.2 数据存储器

当检测到信号时,数字信号处理器开始将六路数据中的三路(左舷或右舷的艏、舯、艉阵元)存入数据存储器中。存储单元的大小是由解算所需的最大数据量、系统的采样速率、三路信号间的最大延时等因素决定的。假设阵长D=45m,取声速c=1500m/s,则在%26;#177;60%26;#176;扇面内,艏艉阵元之间信号到达的最大延时为:

Dsin60%26;#176;≈26(ms) (3)

若系统的采样速率为1MSPS,系统解算数据至少需要30ms长的样本,则在数据存储过程中至少要存储的数据量(从信号到达时刻算起)为:

(26ms+30ms)%26;#215;3%26;#215;1MSPS=168Kword (4)

2.3.3 数据解算运算量

数据存储完毕后,数字信号处理器开始进行参数的解算。解算内容主要包括:粗测时延、频率估计、相位估计、目标跟踪关联等。数字信号处理器在解算过程中不再响应外部的中断,此时是系统工作的盲区。根据声纳使用要求,这个盲区越小越好,这意味着主处理器的运算速度越大越好。据粗略估计,若要求盲区为100毫秒,则160MHz的处理器是能够完成任务的。

2.4 输入信号动态范围

根据环境噪声谱级的分析,系统背景噪声的动态范围不超过42d B,再考虑到信噪比要大于13dB,系统输入的动态范围应大于55dB,则ADC的精度应该不低于10比特。

3 硬件设计方案

本系统硬件电路采用模块化的设计方案,如图4所示。按照功能大致可以分为四个大的模块:模/数转换模块、逻辑控制模块、数字信号处理器模块、数据存储模块。下面就各个模块的功能及实现方法进行详细介绍。

3.1 模/数转换模块

模/数转换模块的功能是完成信号从模拟形式到数字形式的转换。如图4所示,模/数转换器通过逻辑控制芯片与数字信号处理器相连接。模/数转换器的转换需要的时钟由逻辑控制芯片对数字信号处理器的时钟输出信号进行分频得到。

由前面的分析可知,模/数转换器的转换速率需要在1MSPS以上,转换精度不能低于10比特。这里选用TI公司的THS1206,其主要特性为:精度为12比特;总的采样速率为6MSPS;可四路同步采样。

3.2 逻辑控制模块

逻辑控制模块的功能包括模/数转换器的设置;模/数转换器数据的输入接口;9比特声速数据的输入接口;1比特的控制线输入接口;1比特的故障自检信号接口;静态RAM与主处理器的接口。在逻辑控制芯片上实现了一块双口数据RAM,用以实现解算数据的存储。本系统中的逻辑控制芯片选用Altera公司的FLEX10K系列器件中的EPF10K10AI144-3,其主要特性如下:逻辑门数为10,000,最高工作速率为125MHz。

3.3 数字信号处理器模块

数字信号处理器是本系统的核心,由它完成各种控制、检测和解算等。数字信号处理器在实时检测过程中实现对信号的检测。当检测到声纳脉冲时,系统转入数据存储进程,这时数字信号处理器负责进行数据存储的控制;当数据存储结束时,系统进行数据的解算,数字信号处理器从片外RAM中读取数据,完成解算,并负责将结果输出。本系统选用TI公司生产的TMS320VC5416-160芯片,其主要特性如下:指令周期峰值运算速度达160MIPS;128K%26;#215;16的片内RAM;16bit定点DSP;8M程序/64K数据存储空间。

3.4 数据存储模块

数据存储模块由静态RAM构成,完成数据的存储。根据数据存储容量,选用Cypress公司生产的CY7C1041BV33-Z15芯片,其最快存储速度为15ns。

另外,其它部分还包括:逻辑控制芯片初始化所需的EEPROM;存放数字信号处理器工作程序的EEPROM;电源管理模块,用以实现电源的管理;一片EPROM,其中存有阵长、水听器基线与舰艇艏艉线之间的夹角和误差修正信息。

图4

4 系统的工作流程

首先是数字信号处理器引导自己的程序,对其内部进行各种设置、对各种寄存器进行初始化及内部自检,同时逻辑控制芯片引导程序进行初始化。初始化以后进行板级自检,由TMS320VC5416完成。自检的内容包括:片外的静态RAM(CY7C1041)、片外的EPROM(2716)、模/数转换器(THS1206)等是否工作正常。完成自检后,将自检的结果通过逻辑控制芯片输出。板级自检之后的工作是读入声速参数及从EPROM(2716)中读进所需的参数。上述工作完成之后,系统就进入如图3所示的工作进程中。

5 实验结果

在实验室里,用电信号目标模拟器测试声纳脉冲侦察模块的性能,输出结果显示在显控台。表1和表2分别给出了方位和距离测量实验的结果。实验结果的测量条件为:6级海况,信噪比为20dB,声速为1500m/s,目标距离为15km,起始方位为30%26;#176;,每秒递增0.2%26;#176;,脉宽为200ms,脉冲重复周期为4s。显控台上频率的显示只精确到0.1kHz,而实际测频误差小于1%,所以对4kHz、8kHz、12kHz的信号进行频率测量时,显示的测量值分别为4.0kHz、8.0kHz、12.0kHz,误差为0%。

表1 方位测量实验结果(均方误差)

频率

右舷

左舷

4.0(kHz)

0.40%26;#176;

0.26%26;#176;

8.0(kHz)

0.28%26;#176;

0.25%26;#176;

12.0(kHz)

0.27%26;#176;

0.27%26;#176;

表2 距离测量实验结果(均方误差)

频率

右舷

左舷

4.0(kHz)

3.88%

3.03%

8.0(kHz)

5.02%

2.21%

12.0(kHz)

3.5%

4.6%

脉冲侦察模块是以TMS320VC5416为核心数据处理单元,以FLEX10K10A作为逻辑控制单元的硬件处理系统,具有可靠性高、结构简单灵活、适应性强、运算能力强的特点。该声纳脉冲侦察设计方案经过实验室的各项性能指标测试,达到了某型声纳技术条件规定的各项需要,工作稳定、性能优良。

2.4 输入信号动态范围

根据环境噪声谱级的分析,系统背景噪声的动态范围不超过42d B,再考虑到信噪比要大于13dB,系统输入的动态范围应大于55dB,则ADC的精度应该不低于10比特。

3 硬件设计方案

本系统硬件电路采用模块化的设计方案,如图4所示。按照功能大致可以分为四个大的模块:模/数转换模块、逻辑控制模块、数字信号处理器模块、数据存储模块。下面就各个模块的功能及实现方法进行详细介绍。

3.1 模/数转换模块

模/数转换模块的功能是完成信号从模拟形式到数字形式的转换。如图4所示,模/数转换器通过逻辑控制芯片与数字信号处理器相连接。模/数转换器的转换需要的时钟由逻辑控制芯片对数字信号处理器的时钟输出信号进行分频得到。

由前面的分析可知,模/数转换器的转换速率需要在1MSPS以上,转换精度不能低于10比特。这里选用TI公司的THS1206,其主要特性为:精度为12比特;总的采样速率为6MSPS;可四路同步采样。

3.2 逻辑控制模块

逻辑控制模块的功能包括模/数转换器的设置;模/数转换器数据的输入接口;9比特声速数据的输入接口;1比特的控制线输入接口;1比特的故障自检信号接口;静态RAM与主处理器的接口。在逻辑控制芯片上实现了一块双口数据RAM,用以实现解算数据的存储。本系统中的逻辑控制芯片选用Altera公司的FLEX10K系列器件中的EPF10K10AI144-3,其主要特性如下:逻辑门数为10,000,最高工作速率为125MHz。

3.3 数字信号处理器模块

数字信号处理器是本系统的核心,由它完成各种控制、检测和解算等。数字信号处理器在实时检测过程中实现对信号的检测。当检测到声纳脉冲时,系统转入数据存储进程,这时数字信号处理器负责进行数据存储的控制;当数据存储结束时,系统进行数据的解算,数字信号处理器从片外RAM中读取数据,完成解算,并负责将结果输出。本系统选用TI公司生产的TMS320VC5416-160芯片,其主要特性如下:指令周期峰值运算速度达160MIPS;128K%26;#215;16的片内RAM;16bit定点DSP;8M程序/64K数据存储空间。

3.4 数据存储模块

数据存储模块由静态RAM构成,完成数据的存储。根据数据存储容量,选用Cypress公司生产的CY7C1041BV33-Z15芯片,其最快存储速度为15ns。

另外,其它部分还包括:逻辑控制芯片初始化所需的EEPROM;存放数字信号处理器工作程序的EEPROM;电源管理模块,用以实现电源的管理;一片EPROM,其中存有阵长、水听器基线与舰艇艏艉线之间的夹角和误差修正信息。

图4

4 系统的工作流程

首先是数字信号处理器引导自己的程序,对其内部进行各种设置、对各种寄存器进行初始化及内部自检,同时逻辑控制芯片引导程序进行初始化。初始化以后进行板级自检,由TMS320VC5416完成。自检的内容包括:片外的静态RAM(CY7C1041)、片外的EPROM(2716)、模/数转换器(THS1206)等是否工作正常。完成自检后,将自检的结果通过逻辑控制芯片输出。板级自检之后的工作是读入声速参数及从EPROM(2716)中读进所需的参数。上述工作完成之后,系统就进入如图3所示的工作进程中。

5 实验结果

在实验室里,用电信号目标模拟器测试声纳脉冲侦察模块的性能,输出结果显示在显控台。表1和表2分别给出了方位和距离测量实验的结果。实验结果的测量条件为:6级海况,信噪比为20dB,声速为1500m/s,目标距离为15km,起始方位为30%26;#176;,每秒递增0.2%26;#176;,脉宽为200ms,脉冲重复周期为4s。显控台上频率的显示只精确到0.1kHz,而实际测频误差小于1%,所以对4kHz、8kHz、12kHz的信号进行频率测量时,显示的测量值分别为4.0kHz、8.0kHz、12.0kHz,误差为0%。

表1 方位测量实验结果(均方误差)

频率

右舷

左舷

4.0(kHz)

0.40%26;#176;

0.26%26;#176;

8.0(kHz)

0.28%26;#176;

0.25%26;#176;

12.0(kHz)

0.27%26;#176;

0.27%26;#176;

表2 距离测量实验结果(均方误差)

频率

右舷

左舷

4.0(kHz)

3.88%

3.03%

8.0(kHz)

5.02%

2.21%

12.0(kHz)

3.5%

4.6%

脉冲侦察模块是以TMS320VC5416为核心数据处理单元,以FLEX10K10A作为逻辑控制单元的硬件处理系统,具有可靠性高、结构简单灵活、适应性强、运算能力强的特点。该声纳脉冲侦察设计方案经过实验室的各项性能指标测试,达到了某型声纳技术条件规定的各项需要,工作稳定、性能优良。

引用地址:声纳脉冲侦察模块的硬件设计及实现

1 声纳脉冲侦察模块测向测距原理

目前,被动测距声纳主要有两种类型:共形阵和拖曳式线列阵,它们都是直线阵。共形阵在舰艇壳体上配置三对(左、右舷侧各三个)子阵。阵元的布放可分为对称阵和非对称阵。对称阵的三个阵元在直线上等间距布放,非对称阵的三个阵元的间距之比是1:2。对于三元阵来说,对称阵和非对称阵的测向、测距原理是相同的。由于阵型的差异,非对称阵和对称阵在测距计算、距离模糊的范围、时延测量误差对测距误差的影响等方面也存在差异。

下面以非对称阵为例给出测向测距原理。如图2所示,设三元非对称阵首中阵元的间距为d,目标方向角为θ目标到各阵元的距离分别为r1、r2、r3,其中,r2为要测定的目标距离r。

在极坐标系中,设目标的坐丁二烯为S(r, θ),三个阵元的坐标分别为1:(d,0),2:(0,0),3:(2d, π),声速为c,目标信号到达各个阵元的时延差分别为τ12、τ23、τ13。其中,τ12表示阵元1、2接收信号的时间差,τ23表示阵元2、3接收信号的时间差,阵元1、3接收信号的时间差τ13为τ12和τ23两者之和。稍加分析和推导可得到在远场的目标方位的近似公式为:

1 声纳脉冲侦察模块测向测距原理

目前,被动测距声纳主要有两种类型:共形阵和拖曳式线列阵,它们都是直线阵。共形阵在舰艇壳体上配置三对(左、右舷侧各三个)子阵。阵元的布放可分为对称阵和非对称阵。对称阵的三个阵元在直线上等间距布放,非对称阵的三个阵元的间距之比是1:2。对于三元阵来说,对称阵和非对称阵的测向、测距原理是相同的。由于阵型的差异,非对称阵和对称阵在测距计算、距离模糊的范围、时延测量误差对测距误差的影响等方面也存在差异。

下面以非对称阵为例给出测向测距原理。如图2所示,设三元非对称阵首中阵元的间距为d,目标方向角为θ目标到各阵元的距离分别为r1、r2、r3,其中,r2为要测定的目标距离r。

在极坐标系中,设目标的坐丁二烯为S(r, θ),三个阵元的坐标分别为1:(d,0),2:(0,0),3:(2d, π),声速为c,目标信号到达各个阵元的时延差分别为τ12、τ23、τ13。其中,τ12表示阵元1、2接收信号的时间差,τ23表示阵元2、3接收信号的时间差,阵元1、3接收信号的时间差τ13为τ12和τ23两者之和。稍加分析和推导可得到在远场的目标方位的近似公式为:

2 设计需求分析

2.1 声纳脉冲侦察模块的主要任务

声纳脉冲侦察模块需要完成的任务主要为:在搜索状态下实时检测声纳脉冲的到达,并快速测量声纳脉冲的频率和目标的方位;在跟踪状态下,进一步解算出目标的距离以及声纳脉冲的重复周期,给出置信度。

2.2 输入输出接口

声纳脉冲模块的输入信号包括:左右舷的艏、舯、艉共六路已放大滤波的阵元信号;存储在EPROM中的阵长、水听器阵基线和舰艇的艏艉线之间的夹角和误差修正表;实时测得的水中声音的传播速度;跟踪命令。输出信息包括:搜索状态和跟踪状态显示信息;解算出的频率、方位、距离等数据;故障自检结果。

2 设计需求分析

2.1 声纳脉冲侦察模块的主要任务

声纳脉冲侦察模块需要完成的任务主要为:在搜索状态下实时检测声纳脉冲的到达,并快速测量声纳脉冲的频率和目标的方位;在跟踪状态下,进一步解算出目标的距离以及声纳脉冲的重复周期,给出置信度。

2.2 输入输出接口

声纳脉冲模块的输入信号包括:左右舷的艏、舯、艉共六路已放大滤波的阵元信号;存储在EPROM中的阵长、水听器阵基线和舰艇的艏艉线之间的夹角和误差修正表;实时测得的水中声音的传播速度;跟踪命令。输出信息包括:搜索状态和跟踪状态显示信息;解算出的频率、方位、距离等数据;故障自检结果。

2.3 软件对硬件的要求

按照侦察模块功能要求,系统软件的工作主要由三个进程构成,如图3所示。系统平时工作在实时检测进程;一旦检测到声纳脉冲,系统就进入数据存储进程,将由模/数转换器输入的数据存入存储器;完成数据存储之后进行数据解算进程,解算之后的结果输出给显控台,然后重新进入检测进程。上述过程将一直循环往复。

2.3.1 实时检测计算量

在实时检测进程中,外部六路阵元输入信号由模/数转换器进行同步并行采样。根据系统要求,每路采样频率为1MHz。数字信号处理器在进行实时检测时要对数据进行降采样处理,使采样频率降为100kHz。数字信号处理器对其中的四路信号(左右舷的艏艉通道)进行实时自适应线谱增强(ALE)运算,以检测声纳脉冲。根据算法分析,计算单路ALE约需要300个指令周期,四通道共需1200个指令周期,若采样频率为100kHz,则数字信号处理器的运算能力应大于120MIPS。

2.3.2 数据存储器

当检测到信号时,数字信号处理器开始将六路数据中的三路(左舷或右舷的艏、舯、艉阵元)存入数据存储器中。存储单元的大小是由解算所需的最大数据量、系统的采样速率、三路信号间的最大延时等因素决定的。假设阵长D=45m,取声速c=1500m/s,则在%26;#177;60%26;#176;扇面内,艏艉阵元之间信号到达的最大延时为:

Dsin60%26;#176;≈26(ms) (3)

若系统的采样速率为1MSPS,系统解算数据至少需要30ms长的样本,则在数据存储过程中至少要存储的数据量(从信号到达时刻算起)为:

(26ms+30ms)%26;#215;3%26;#215;1MSPS=168Kword (4)

2.3.3 数据解算运算量

数据存储完毕后,数字信号处理器开始进行参数的解算。解算内容主要包括:粗测时延、频率估计、相位估计、目标跟踪关联等。数字信号处理器在解算过程中不再响应外部的中断,此时是系统工作的盲区。根据声纳使用要求,这个盲区越小越好,这意味着主处理器的运算速度越大越好。据粗略估计,若要求盲区为100毫秒,则160MHz的处理器是能够完成任务的。

2.3 软件对硬件的要求

按照侦察模块功能要求,系统软件的工作主要由三个进程构成,如图3所示。系统平时工作在实时检测进程;一旦检测到声纳脉冲,系统就进入数据存储进程,将由模/数转换器输入的数据存入存储器;完成数据存储之后进行数据解算进程,解算之后的结果输出给显控台,然后重新进入检测进程。上述过程将一直循环往复。

2.3.1 实时检测计算量

在实时检测进程中,外部六路阵元输入信号由模/数转换器进行同步并行采样。根据系统要求,每路采样频率为1MHz。数字信号处理器在进行实时检测时要对数据进行降采样处理,使采样频率降为100kHz。数字信号处理器对其中的四路信号(左右舷的艏艉通道)进行实时自适应线谱增强(ALE)运算,以检测声纳脉冲。根据算法分析,计算单路ALE约需要300个指令周期,四通道共需1200个指令周期,若采样频率为100kHz,则数字信号处理器的运算能力应大于120MIPS。

2.3.2 数据存储器

当检测到信号时,数字信号处理器开始将六路数据中的三路(左舷或右舷的艏、舯、艉阵元)存入数据存储器中。存储单元的大小是由解算所需的最大数据量、系统的采样速率、三路信号间的最大延时等因素决定的。假设阵长D=45m,取声速c=1500m/s,则在%26;#177;60%26;#176;扇面内,艏艉阵元之间信号到达的最大延时为:

Dsin60%26;#176;≈26(ms) (3)

若系统的采样速率为1MSPS,系统解算数据至少需要30ms长的样本,则在数据存储过程中至少要存储的数据量(从信号到达时刻算起)为:

(26ms+30ms)%26;#215;3%26;#215;1MSPS=168Kword (4)

2.3.3 数据解算运算量

数据存储完毕后,数字信号处理器开始进行参数的解算。解算内容主要包括:粗测时延、频率估计、相位估计、目标跟踪关联等。数字信号处理器在解算过程中不再响应外部的中断,此时是系统工作的盲区。根据声纳使用要求,这个盲区越小越好,这意味着主处理器的运算速度越大越好。据粗略估计,若要求盲区为100毫秒,则160MHz的处理器是能够完成任务的。

2.4 输入信号动态范围

根据环境噪声谱级的分析,系统背景噪声的动态范围不超过42d B,再考虑到信噪比要大于13dB,系统输入的动态范围应大于55dB,则ADC的精度应该不低于10比特。

3 硬件设计方案

本系统硬件电路采用模块化的设计方案,如图4所示。按照功能大致可以分为四个大的模块:模/数转换模块、逻辑控制模块、数字信号处理器模块、数据存储模块。下面就各个模块的功能及实现方法进行详细介绍。

3.1 模/数转换模块

模/数转换模块的功能是完成信号从模拟形式到数字形式的转换。如图4所示,模/数转换器通过逻辑控制芯片与数字信号处理器相连接。模/数转换器的转换需要的时钟由逻辑控制芯片对数字信号处理器的时钟输出信号进行分频得到。

由前面的分析可知,模/数转换器的转换速率需要在1MSPS以上,转换精度不能低于10比特。这里选用TI公司的THS1206,其主要特性为:精度为12比特;总的采样速率为6MSPS;可四路同步采样。

3.2 逻辑控制模块

逻辑控制模块的功能包括模/数转换器的设置;模/数转换器数据的输入接口;9比特声速数据的输入接口;1比特的控制线输入接口;1比特的故障自检信号接口;静态RAM与主处理器的接口。在逻辑控制芯片上实现了一块双口数据RAM,用以实现解算数据的存储。本系统中的逻辑控制芯片选用Altera公司的FLEX10K系列器件中的EPF10K10AI144-3,其主要特性如下:逻辑门数为10,000,最高工作速率为125MHz。

3.3 数字信号处理器模块

数字信号处理器是本系统的核心,由它完成各种控制、检测和解算等。数字信号处理器在实时检测过程中实现对信号的检测。当检测到声纳脉冲时,系统转入数据存储进程,这时数字信号处理器负责进行数据存储的控制;当数据存储结束时,系统进行数据的解算,数字信号处理器从片外RAM中读取数据,完成解算,并负责将结果输出。本系统选用TI公司生产的TMS320VC5416-160芯片,其主要特性如下:指令周期峰值运算速度达160MIPS;128K%26;#215;16的片内RAM;16bit定点DSP;8M程序/64K数据存储空间。

3.4 数据存储模块

数据存储模块由静态RAM构成,完成数据的存储。根据数据存储容量,选用Cypress公司生产的CY7C1041BV33-Z15芯片,其最快存储速度为15ns。

另外,其它部分还包括:逻辑控制芯片初始化所需的EEPROM;存放数字信号处理器工作程序的EEPROM;电源管理模块,用以实现电源的管理;一片EPROM,其中存有阵长、水听器基线与舰艇艏艉线之间的夹角和误差修正信息。

图4

4 系统的工作流程

首先是数字信号处理器引导自己的程序,对其内部进行各种设置、对各种寄存器进行初始化及内部自检,同时逻辑控制芯片引导程序进行初始化。初始化以后进行板级自检,由TMS320VC5416完成。自检的内容包括:片外的静态RAM(CY7C1041)、片外的EPROM(2716)、模/数转换器(THS1206)等是否工作正常。完成自检后,将自检的结果通过逻辑控制芯片输出。板级自检之后的工作是读入声速参数及从EPROM(2716)中读进所需的参数。上述工作完成之后,系统就进入如图3所示的工作进程中。

5 实验结果

在实验室里,用电信号目标模拟器测试声纳脉冲侦察模块的性能,输出结果显示在显控台。表1和表2分别给出了方位和距离测量实验的结果。实验结果的测量条件为:6级海况,信噪比为20dB,声速为1500m/s,目标距离为15km,起始方位为30%26;#176;,每秒递增0.2%26;#176;,脉宽为200ms,脉冲重复周期为4s。显控台上频率的显示只精确到0.1kHz,而实际测频误差小于1%,所以对4kHz、8kHz、12kHz的信号进行频率测量时,显示的测量值分别为4.0kHz、8.0kHz、12.0kHz,误差为0%。

表1 方位测量实验结果(均方误差)

频率

右舷

左舷

4.0(kHz)

0.40%26;#176;

0.26%26;#176;

8.0(kHz)

0.28%26;#176;

0.25%26;#176;

12.0(kHz)

0.27%26;#176;

0.27%26;#176;

表2 距离测量实验结果(均方误差)

频率

右舷

左舷

4.0(kHz)

3.88%

3.03%

8.0(kHz)

5.02%

2.21%

12.0(kHz)

3.5%

4.6%

脉冲侦察模块是以TMS320VC5416为核心数据处理单元,以FLEX10K10A作为逻辑控制单元的硬件处理系统,具有可靠性高、结构简单灵活、适应性强、运算能力强的特点。该声纳脉冲侦察设计方案经过实验室的各项性能指标测试,达到了某型声纳技术条件规定的各项需要,工作稳定、性能优良。

2.4 输入信号动态范围

根据环境噪声谱级的分析,系统背景噪声的动态范围不超过42d B,再考虑到信噪比要大于13dB,系统输入的动态范围应大于55dB,则ADC的精度应该不低于10比特。

3 硬件设计方案

本系统硬件电路采用模块化的设计方案,如图4所示。按照功能大致可以分为四个大的模块:模/数转换模块、逻辑控制模块、数字信号处理器模块、数据存储模块。下面就各个模块的功能及实现方法进行详细介绍。

3.1 模/数转换模块

模/数转换模块的功能是完成信号从模拟形式到数字形式的转换。如图4所示,模/数转换器通过逻辑控制芯片与数字信号处理器相连接。模/数转换器的转换需要的时钟由逻辑控制芯片对数字信号处理器的时钟输出信号进行分频得到。

由前面的分析可知,模/数转换器的转换速率需要在1MSPS以上,转换精度不能低于10比特。这里选用TI公司的THS1206,其主要特性为:精度为12比特;总的采样速率为6MSPS;可四路同步采样。

3.2 逻辑控制模块

逻辑控制模块的功能包括模/数转换器的设置;模/数转换器数据的输入接口;9比特声速数据的输入接口;1比特的控制线输入接口;1比特的故障自检信号接口;静态RAM与主处理器的接口。在逻辑控制芯片上实现了一块双口数据RAM,用以实现解算数据的存储。本系统中的逻辑控制芯片选用Altera公司的FLEX10K系列器件中的EPF10K10AI144-3,其主要特性如下:逻辑门数为10,000,最高工作速率为125MHz。

3.3 数字信号处理器模块

数字信号处理器是本系统的核心,由它完成各种控制、检测和解算等。数字信号处理器在实时检测过程中实现对信号的检测。当检测到声纳脉冲时,系统转入数据存储进程,这时数字信号处理器负责进行数据存储的控制;当数据存储结束时,系统进行数据的解算,数字信号处理器从片外RAM中读取数据,完成解算,并负责将结果输出。本系统选用TI公司生产的TMS320VC5416-160芯片,其主要特性如下:指令周期峰值运算速度达160MIPS;128K%26;#215;16的片内RAM;16bit定点DSP;8M程序/64K数据存储空间。

3.4 数据存储模块

数据存储模块由静态RAM构成,完成数据的存储。根据数据存储容量,选用Cypress公司生产的CY7C1041BV33-Z15芯片,其最快存储速度为15ns。

另外,其它部分还包括:逻辑控制芯片初始化所需的EEPROM;存放数字信号处理器工作程序的EEPROM;电源管理模块,用以实现电源的管理;一片EPROM,其中存有阵长、水听器基线与舰艇艏艉线之间的夹角和误差修正信息。

图4

4 系统的工作流程

首先是数字信号处理器引导自己的程序,对其内部进行各种设置、对各种寄存器进行初始化及内部自检,同时逻辑控制芯片引导程序进行初始化。初始化以后进行板级自检,由TMS320VC5416完成。自检的内容包括:片外的静态RAM(CY7C1041)、片外的EPROM(2716)、模/数转换器(THS1206)等是否工作正常。完成自检后,将自检的结果通过逻辑控制芯片输出。板级自检之后的工作是读入声速参数及从EPROM(2716)中读进所需的参数。上述工作完成之后,系统就进入如图3所示的工作进程中。

5 实验结果

在实验室里,用电信号目标模拟器测试声纳脉冲侦察模块的性能,输出结果显示在显控台。表1和表2分别给出了方位和距离测量实验的结果。实验结果的测量条件为:6级海况,信噪比为20dB,声速为1500m/s,目标距离为15km,起始方位为30%26;#176;,每秒递增0.2%26;#176;,脉宽为200ms,脉冲重复周期为4s。显控台上频率的显示只精确到0.1kHz,而实际测频误差小于1%,所以对4kHz、8kHz、12kHz的信号进行频率测量时,显示的测量值分别为4.0kHz、8.0kHz、12.0kHz,误差为0%。

表1 方位测量实验结果(均方误差)

频率

右舷

左舷

4.0(kHz)

0.40%26;#176;

0.26%26;#176;

8.0(kHz)

0.28%26;#176;

0.25%26;#176;

12.0(kHz)

0.27%26;#176;

0.27%26;#176;

表2 距离测量实验结果(均方误差)

频率

右舷

左舷

4.0(kHz)

3.88%

3.03%

8.0(kHz)

5.02%

2.21%

12.0(kHz)

3.5%

4.6%

脉冲侦察模块是以TMS320VC5416为核心数据处理单元,以FLEX10K10A作为逻辑控制单元的硬件处理系统,具有可靠性高、结构简单灵活、适应性强、运算能力强的特点。该声纳脉冲侦察设计方案经过实验室的各项性能指标测试,达到了某型声纳技术条件规定的各项需要,工作稳定、性能优良。

上一篇:基于FPGA的TCP粘合设计与实现

下一篇:Xilinx Foundation F3.1的结构及设计流程

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 UPC393GR-9LG-A

UPC393GR-9LG-A

京公网安备 11010802033920号

京公网安备 11010802033920号