在采用微处理器和数字设计的范例中,可以将一些设计从硬连接器件转移到易于移植和易于更新的软件领域,这样就可以在一个“软”环境中处理复杂问题。在整个设计过程中,“软”环境一直都很灵活且容易改变。

如今,由于可编程器件(如FPGA)容量大、性能高、成本相对较低的特性,这种平衡又在发生变化,以前硬件设计元素(如处理器及其外围器件和逻辑块)也可以转移到软领域(图1)。因此,在整个开发周期内,灵活性可能更大,更改关键设计也更加方便,比如可以更改软件与硬件实现之间的功能分区,甚至更改处理器的选择。

与大量使用分立的现有处理器开发嵌入式系统相比,目前开发基于FPGA的处理器应用程序的做法仍很少。尽管FPGA已确实广泛应用于与嵌入式系统处理器密切相关的外围逻辑中,但除了可编程设计之外,处理器及其重要外围器件仍保持着导线连接。

|

| 图1:随着用户买得起的高性能可编程器件的问世,设计工程师可将相当部分的硬件设计从硬连线平台转移到“软”环境中,从而节省设计时间、简化电路板设计并降低制造成本。 |

部分原因来自于成本。FPGA的体积大、性能高,尽管能提供一个处理器的应用平台,但与性能相当的分立MCU相比,它也更加昂贵。因此,采用FPGA方案所产生的额外费用限制了FPGA方案的应用范围。不过最近,赛灵思Spartan-3系列等器件消除了价格上的限制,当这些器件与合适的基于FPGA的处理器内核相结合时,成本与收益的平衡将被打破。

即使价格不再是限制FPGA作为主流嵌入式系统平台的唯一障碍,但仍存在另一个更难处理的问题,即我们需要改变对可编程逻辑器件的总体看法。我们不能仅仅把它们看成集成逻辑块的有效方法,而是需要扩大视野范围,重新评估在器件(如FPGA)可重新配置的情况下我们对整个设计过程的看法。

对“界面友好”开发模型的需求

如果在更大范围内审度与嵌入式设计相关的FPGA现象,线索也许就在于微处理器本身的历史。微处理器最初用于计算器,后来用于个人电脑。当器件价格只占一小部分产品成本时,随着技术的进步,用户界面友好的开发模型开始得到广泛应用(如高级编程语言C语言的应用)。

由于软件具有很好的灵活性和强大功能,所以它们可以创建一种新的设计模式,该模式可以自由创建和修改大部分系统功能而无需重新设计硬件。采用C语言编写嵌入式应用程序,意味着众多设计工程师可以获得其强大功能和灵活性,这促使基于处理器的嵌入式设计成为电子产品的主流设计。

FPGA可以大大增加系统中“软”器件的数量,从而具有类似于引发设计革命的潜力。正如前文所述,大型可编程器件现在的价格使之足以与离散处理器系统竞争。为推动设计工程师采用FPGA器件作为嵌入式应用平台,需要一种用户界面友好的开发方法。该方法既容易被大多数工程师理解,又能方便地将处理器、外围硬件和软件轻松集成在可编程平台中。除此之外,一种在板极设计过程中集成FPGA设计的方法,可以让用户轻松应对在新的“软”设计模型中发生的变化。

|

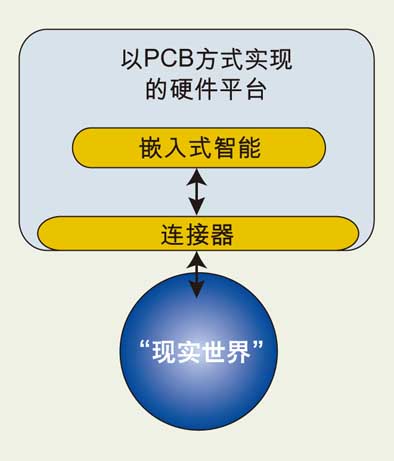

| 图2:嵌入式产品智能包括软件以及包含在FPGA中的软连接系统器件,PCB仅成为器件智能连接外部世界的一个平台。 |

但当我们把FPGA看作系统平台时,在HDL领域获得必需的系统器件(例如处理器与外围器件),并在寄存器转换级实现它们的过程十分复杂。对那些目前还不是FPGA专家的大多数工程师来说,这是一个令人生畏的过程。

但是,工程师在板级上开发同样复杂的设计系统不会遇到这些困难,因为在板级上,系统的复杂性表现在用来创建设计的现有器件上,而工程师只是简单地使用这些器件,并不需要了解其内在复杂性。

因此,挖掘FPGA作为主流嵌入式系统平台的潜能,关键就在于提供当前板级设计与基于FPGA的系统设计之间的无缝转换。

未来的设计工具与嵌入式智能

设计解决方案供应商Altium公司提供的电子产品开发系统Altium Designer,近年来引领着设计工具的发展趋势。Altium Designer为FPGA提供图形输入环境,其中包含高级FPGA器件库。这些器件包括一系列处理器内核和外围器件,它们为大量目标FPGA器件提供预综合。由于器件是现成的,所以创建系统硬件几乎成了“拖放”操作。

这个系统包含自行设计、免费的32位处理器TSK3000,该处理器可被用于大量FPGA器件及其它系列产品中。其它能支持的运行平台包括赛灵思MicroBlaze内核和内嵌于Virtex II Pro器件中的硬PowerPC处理器。

Altium Designer广泛使用免费的开放式Wishbone处理器互连总线。为便于处理器和外围器件的互连,它还提供多个可配置总线连接器件。基于Wishbone的封装内核可用于MicroBlaze和PowerPC等处理器,并且可以重新定位处理器之间的设计而无需重新设计该系统。一个通用的编译引擎和集成工具链在软件层支持这个过程。

这种方案的优势是嵌入式开发人员可以为他们的应用软件选择最合适的运行平台。他们可以采用TSK3000开始设计,如果以后需要更高性能,则可以将设计移植到PowerPC,或者移植到MicroBlaze解决方案。

Altium Designer系统最基本的优势在于,任何硬件开发商都可以利用现有技术,将系统复杂度由板级设计转移到“软”的可编程逻辑领域。这使得大量的设计工程师可从硬连接系统器件中解脱出来,并能发挥在快速变化的硬件和软件环境中进行设计所带来的优势。

设计流程朝“软件”方向的转变始于低成本微处理器的供应。由于FPGA技术的进步,这种转变正走向一个新的阶段。如今,电子产品的大部分智能主要取决于嵌入式软件。通过FPGA,嵌入式智能将跨越可编程平台中的软件和软连接器件(图2),这种可能性将刺激FPGA的广泛使用,并为未来电子产品的开发奠定基础。

上一篇:复杂器件内部的实时可视性的实现方法

下一篇:ARM CPU的软件基础

推荐阅读最新更新时间:2024-05-13 18:11

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号