SoC(片上系统)的概念已日益普及,而随着FPGA技术的迅速发展,可编程系统芯片(SoPC)作为一种特殊的嵌入式微处理器系统,融合了SoC和FPGA各自的优点,并具备软硬件在系统可编程、可裁减、可扩充、可升级的功能,已逐渐成为一个新兴的技术方向。SoPC的核心是在FPGA上实现的嵌入式微处理器核,目前主要有Xilinx公司的32位软核MicroBlaze、32位PowerPC系列处理器硬核PowerPC 405,以及Altera公司的Nios系列微处理器软核等。

本文介绍的系统是一个以PowerPC 405为微处理器,基于VME总线的以太网接口设备,它通过以太网和VME总线接口,实现VME系统与外部局域网的实时数据交换。

硬件开发

开发采用Xilinx公司的EDK7.1(嵌入式开发套件)和ISE7.1工具软件。EDK工具包中集成了硬件平台生成器(Platgen)、软件平台生成器(Libgen)、仿真模型生成器(Simgen)、软件编译器(Mb-gcc/ppc-gcc)和软件调试工具(Mb-gdb/ppc-gdb)等,通过提供的集成开发环境XPS,用户可以调用上述所有工具,来完成嵌入式系统开发的整个流程。

首先在XPS界面环境下生成硬件系统框架并添加所需的IP核,也可以用文本编辑器直接编写硬件描述文件 (.MHS文件),再调用Platgen将其生成嵌入式处理系统的网表文件(.NGC文件);然后通过系统生成或手工编辑的软件描述文件(.MSS文件)来设置系统软件配置,并调用Libgen生成驱动层和库。虽然EDK的IP库中有一些很有用的功能模块和外设接口的IP核,如DCM(数字时钟管理器)、处理器复位、PLB/OPB总线接口、外部存储控制器(EMC)、UART、GPIO、中断控制器、定时器等,充分利用这些资源就可以构建一个较为完善的嵌入式微处理器系统,但是对于许多有特殊专用电路的嵌入式计算机系统的应用还是不够的。如何将用户专用电路设计到EDK系统中,一般有两种方法,第一种是将EDK工程作为一个子系统在XPS中用Export to PorjNav生成ISE工程,然后在ISE中将专用电路和处理器子系统(system.vhd)合成为顶层HDL文件(system_stub.vhd)后,在ISE中完成综合布线,最后在XPS中用Import from PorjNav得到硬件的.bit文件,便可以回到XPS中完成和应用软件的合成、下载和调试了。第二种方法是将专用电路设计成为用户自定义的IP Core,然后直接在系统中调用来实现。自定义的IP Core用HDL设计并要满足EDK的规范,如有专门目录结构和处理器外设定义文件(.MPD)、外设分析定义文件(.PAO)等。如果自定义的IP Core要具有软件驱动,那设计还要完全符合相应的PLB或OPB总线接口规范。完成了硬件和驱动的设计后,就可以在XPS工程中添加应用软件项目并编写应用软件,然后调用处理器对应的编译器编译并和硬件综合后生成的.bit文件合成后下载到目标板便可以进行调试了。

本系统硬件组成框图如图1所示。本设计选用Virtex-II Pro系列FPGA芯片XC2VP40,将系统的程序存储器和数据存储器都放在片内用Block RAM来实现,在系统中添加DCM模块,将外部参考时钟4倍频提供给PowerPC 405作处理器时钟,并分频后再送给OPB总线作总线时钟,降低慢速外设的总线速度,使系统搭配更合理。

图1 系统硬件组成框图

PowerPC 405是此嵌入式系统的核心,它通过PLB总线实现和程序存储器和数据存储器的快速通道,并通过PLB-OPB桥实现了片上的OPB总线,然后通过OPB总线进行各种外设的扩展,OPB外设包括一个RS232串口,一个OPB_EMC用于扩展以太网控制器芯片,一个GPIO作以太网控制器输出的中断请求,一个中断控制器OPB_INTC将GPIO输入的外部中断通知PowerPC 405并可以设置优先级,还有一个用户自定义的IP Core用于实现和VME总线的接口电路。

PowerPC 405 是专门为嵌入式应用而设计的高性能32位PowerPC系列处理器芯核,对于Virtex-II Pro系列FPGA,其实现型号为PowerPC 405D5。

PLB是处理器本机总线,它为指令和数据一侧提供独立的32位地址和64位数据总线。PLB总线架构支持多主从设备,每一个PLB主控机通过独立的地址总线、读数据总线和写数据总线与PLB连接,有一个中央判决机构来授权对PLB的访问以允许主控机通过竞争来获得总线的所有权。OPB是片上外设总线,提供分离的32位地址总线和32位数据总线,一般用来访问低速和低性能的系统资源。它是一种完全同步总线,但不直接连接到处理器内核,处理器内核通过“PLB to OPB”桥和OPB总线来访问OPB接口外设。

网络控制器采用Cirrus Logic公司的通用单片10/100M以太网控制器CS8900A,该芯片完全遵从与IEEE 802.3以太网标准,支持完全的全双工操作。应用EDK的OPB_EMC IP可以很方便地将CS8900A扩展为系统OPB总线上的一个设备,只要将EMC端口的地址、数据总线以及控制信号分别接到CS8900A的地址、数据总线和控制端口上,并将EMC的时序参数设置成与CS8900A手册上要求的一致就可以了。另外将CS8900A的中断输出INTRQ作为一个GPIO引入系统以实现以太网的中断服务功能。

自定义的IP Core内容如图2所示,它用FPGA内的Block RAM资源实现64KB的双口RAM用来完成和VME总线上其他设备的通信和数据交换。我们用上述的第二种方法来实现将用户专用电路嵌入微处理器系统中,自定义的IP主要包括OPB总线接口和用户电路两部分,我们用EDK提供的OPB总线的IPIF模板修改后,作为自定义IP的总线接口,64KB的双口RAM和VME总线接口是真正的用户电路。

图1 系统硬件组成框图

PowerPC 405是此嵌入式系统的核心,它通过PLB总线实现和程序存储器和数据存储器的快速通道,并通过PLB-OPB桥实现了片上的OPB总线,然后通过OPB总线进行各种外设的扩展,OPB外设包括一个RS232串口,一个OPB_EMC用于扩展以太网控制器芯片,一个GPIO作以太网控制器输出的中断请求,一个中断控制器OPB_INTC将GPIO输入的外部中断通知PowerPC 405并可以设置优先级,还有一个用户自定义的IP Core用于实现和VME总线的接口电路。

PowerPC 405 是专门为嵌入式应用而设计的高性能32位PowerPC系列处理器芯核,对于Virtex-II Pro系列FPGA,其实现型号为PowerPC 405D5。

PLB是处理器本机总线,它为指令和数据一侧提供独立的32位地址和64位数据总线。PLB总线架构支持多主从设备,每一个PLB主控机通过独立的地址总线、读数据总线和写数据总线与PLB连接,有一个中央判决机构来授权对PLB的访问以允许主控机通过竞争来获得总线的所有权。OPB是片上外设总线,提供分离的32位地址总线和32位数据总线,一般用来访问低速和低性能的系统资源。它是一种完全同步总线,但不直接连接到处理器内核,处理器内核通过“PLB to OPB”桥和OPB总线来访问OPB接口外设。

网络控制器采用Cirrus Logic公司的通用单片10/100M以太网控制器CS8900A,该芯片完全遵从与IEEE 802.3以太网标准,支持完全的全双工操作。应用EDK的OPB_EMC IP可以很方便地将CS8900A扩展为系统OPB总线上的一个设备,只要将EMC端口的地址、数据总线以及控制信号分别接到CS8900A的地址、数据总线和控制端口上,并将EMC的时序参数设置成与CS8900A手册上要求的一致就可以了。另外将CS8900A的中断输出INTRQ作为一个GPIO引入系统以实现以太网的中断服务功能。

自定义的IP Core内容如图2所示,它用FPGA内的Block RAM资源实现64KB的双口RAM用来完成和VME总线上其他设备的通信和数据交换。我们用上述的第二种方法来实现将用户专用电路嵌入微处理器系统中,自定义的IP主要包括OPB总线接口和用户电路两部分,我们用EDK提供的OPB总线的IPIF模板修改后,作为自定义IP的总线接口,64KB的双口RAM和VME总线接口是真正的用户电路。

图2 自定义的IP Core结构

软件开发

嵌入式开发环境EDK(Embedded Development Kit)将软件开发分为两大部分,一是底层系统软件的开发,主要完成BSP(板级支持包)的功能;另一部分则是用户应用软件的开发(包括用户硬件驱动及用户上层应用软件)。由于EDK中带有许多IP核以及相应的驱动软件,因此底层系统软件的开发大部分可以借助EDK集成开发环境来完成的,如操作系统的选择、设备驱动程序的选择、中断/异常处理例程的设置、操作系统参数设置等在内的各种系统级软件参数的设置。而用户应用软件的开发由于有底层驱动的隔离,可移植性好。整个用户软件的开发及调试工作都可以在EDK中完成。

● 底层系统软件开发

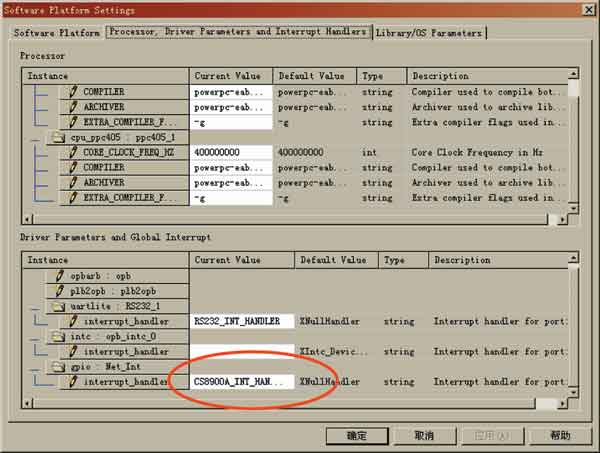

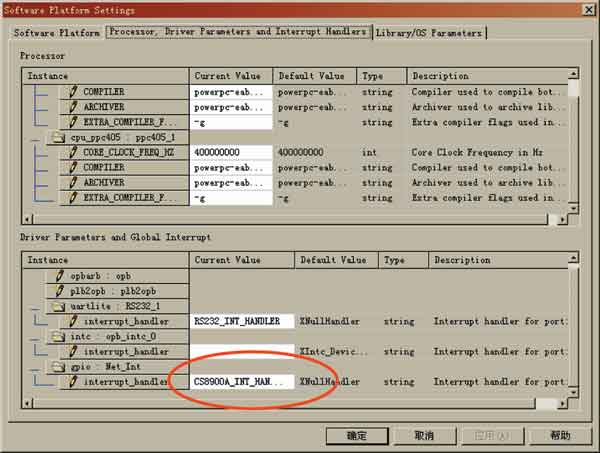

在本设计中,没有使用操作系统,使用所谓的standalone模式,即EDK仅提供硬件初始化及引导代码。此外还需要对GPIO、EMC、RS232、中断控制器等一些外设生成底层驱动,这些都可以通过在EDK集成环境XPS中选择菜单Project->Software Platform Settings的对话框进行设置,如图3所示。其实质是自动修改工程的.MSS文件。例如中断函数的处理例程可在如图4所示的界面中加以设置。也可以手工编辑.MSS文件如下设置:

PARAMETER int_handler = CS8900A_INT_HANDLER, int_port = IP2INTC_Irpt

图2 自定义的IP Core结构

软件开发

嵌入式开发环境EDK(Embedded Development Kit)将软件开发分为两大部分,一是底层系统软件的开发,主要完成BSP(板级支持包)的功能;另一部分则是用户应用软件的开发(包括用户硬件驱动及用户上层应用软件)。由于EDK中带有许多IP核以及相应的驱动软件,因此底层系统软件的开发大部分可以借助EDK集成开发环境来完成的,如操作系统的选择、设备驱动程序的选择、中断/异常处理例程的设置、操作系统参数设置等在内的各种系统级软件参数的设置。而用户应用软件的开发由于有底层驱动的隔离,可移植性好。整个用户软件的开发及调试工作都可以在EDK中完成。

● 底层系统软件开发

在本设计中,没有使用操作系统,使用所谓的standalone模式,即EDK仅提供硬件初始化及引导代码。此外还需要对GPIO、EMC、RS232、中断控制器等一些外设生成底层驱动,这些都可以通过在EDK集成环境XPS中选择菜单Project->Software Platform Settings的对话框进行设置,如图3所示。其实质是自动修改工程的.MSS文件。例如中断函数的处理例程可在如图4所示的界面中加以设置。也可以手工编辑.MSS文件如下设置:

PARAMETER int_handler = CS8900A_INT_HANDLER, int_port = IP2INTC_Irpt

图3 在XPS中设置操作系统和驱动程序

图3 在XPS中设置操作系统和驱动程序

图4 在XPS中设置中断服务例程

设置完成后在XPS中运行Tools->Generate Libraries and BSPs将调用LibGen自动生成驱动库文件,这些CPU和外设驱动库的设置、操作函数实现或定义可在工程项目根目录下的以处理器实例名为名字的目录下的libsrc目录下相应的各模块子目录中找到,参考其实现有助于深刻理解事实上发生的操作。例如中断向量表可在中段向量控制器模块子目录(本例中为intc_v1_00_csrc)下的xintc_g.c文件中找到。

● 用户软件开发

用户软件主要是对网络控制器、GPIO、RS232串口等的操作,其中控制CS8900A的程序是重要部分,它要完成TCP/IP协议。CS8900A所有的控制寄存器和数据寄存器都映射在被称为PacketPage的片上4K地址空间内,这4K空间可映射到主机地址空间中(存储器模式),或通过8个16位I/O口进行存取(I/O模式)。本设计中CS8900A工作于I/O模式,通过EDK的OPB_EMC IP作为OPB总线上的一个设备,并给EMC控制器和所映射的设备分配操作地址空间,在程序中用

Xuint32 XIo_In32(XIo_Address InAddress);

void XIo_Out32(XIo_Address OutAddress, Xuint32 Value);

读写映射的设备,这两个I/O函数同*pDestMem = Value(直接读写存储器操作)的差别在于前者做了读写同步(调用eieio汇编指令)。参考芯片手册编写CS8900A的驱动,实现基本I/O操作CS8900A_SendFrame和CS8900A_RecvFrame。EDK中有需付费的以太网IP CORE并附带有一些TCP/IP协议栈,该协议栈实现了大部分常用功能,但也有一些重要功能并未实现,例如TCP包的超时未达重发,收发操作的中断工作方式。通过修改、增加和完善这些软件包,实现了真正面向用户更高层应用软件的网络编程接口。

● 软件开发中的部分问题

软件开发过程中遇到的几个主要问题归纳如下:

(1)IEEE 802.3网络及网络控制器CS8900A采用的均是Little Endian编码,而XC2VP40内含的处理器PowerPC 405D5采用的是Big Endian编码方式,因此在数据I/O过程中需要做一下转换。

(2)可通过编写链接控制脚本文件控制应用程序的链接过程,从而控制程序映像在存储器中的重定位过程。这在FPGA这种存储器资源有限的环境中有时很有用。

(3)要将EDK提供的默认bootloop程序打包到硬件初始化流中,这样做的目的是提供默认的CPU复位后运行程序,保证CPU处在可预知的状态,而不是因为执行了存储器中的随机代码而处于一种未知的状态。

系统调试方法

由于PowerPC 405处理器核中已包含调试模块,并用JTAG端口引出,只要在系统中添加一个叫做JTAGPPC的IP模块并和PowerPC 405相连便可将其调试端口串入FPGA的JTAG链中,这样只需使用FPGA本身的下载电缆和JTAG接口便可完成系统软件调试而不需要增加额外电路。

EDK提供的软件调试工具主要有XMD和GDB。值得一提的是利用XMD下载可执行程序映像时还会显示各程序段的重定位情况,在发生错误时会报告错误,诸如要求的地址空间大于实际提供的地址空间等错误,而这在EDK集成环境下是看不到的。在存在多种类型存储器资源的情况下,编写链接控制脚本文件控制重定位过程可能能够解决上述某地址空间不够的问题。网络通信部分的调试主要由Sniffer软件辅助完成。

GDB是EDK附带的GNU的主机方图形界面调试工具,它通过和XMD通信完成图形界面调试功能,此时XMD则扮演了一个主机方调试代理的角色,所有的调试通信是由XMD同目标机通信完成的。

结语

SoPC使得硬件设计能真正实现象搭积木一样方便迅速,而利用EDK开发工具就可以实现一个基于FPGA的嵌入式系统的软硬件一体化的开发,的确大大提高了嵌入式系统的开发效率,但是目前它还有许多不够完善的方面。

首先是系统设计对设计工具软件的依赖性很大,而这些软件还有许多有待修正完善的地方,设计师无法避免将在使用熟悉软件方面花许多时间。其次,IP Core的不断丰富和完善是SoPC的基础,昂贵的付费IP核不利于此技术的推广,尤其在国内,而要设计验证用户自己的IP Core对设计者的要求较高。如今一个完善的嵌入式系统都有实时操作系统在运行,SoPC要成为主流也需要更丰富的RTOS的支持。

图4 在XPS中设置中断服务例程

设置完成后在XPS中运行Tools->Generate Libraries and BSPs将调用LibGen自动生成驱动库文件,这些CPU和外设驱动库的设置、操作函数实现或定义可在工程项目根目录下的以处理器实例名为名字的目录下的libsrc目录下相应的各模块子目录中找到,参考其实现有助于深刻理解事实上发生的操作。例如中断向量表可在中段向量控制器模块子目录(本例中为intc_v1_00_csrc)下的xintc_g.c文件中找到。

● 用户软件开发

用户软件主要是对网络控制器、GPIO、RS232串口等的操作,其中控制CS8900A的程序是重要部分,它要完成TCP/IP协议。CS8900A所有的控制寄存器和数据寄存器都映射在被称为PacketPage的片上4K地址空间内,这4K空间可映射到主机地址空间中(存储器模式),或通过8个16位I/O口进行存取(I/O模式)。本设计中CS8900A工作于I/O模式,通过EDK的OPB_EMC IP作为OPB总线上的一个设备,并给EMC控制器和所映射的设备分配操作地址空间,在程序中用

Xuint32 XIo_In32(XIo_Address InAddress);

void XIo_Out32(XIo_Address OutAddress, Xuint32 Value);

读写映射的设备,这两个I/O函数同*pDestMem = Value(直接读写存储器操作)的差别在于前者做了读写同步(调用eieio汇编指令)。参考芯片手册编写CS8900A的驱动,实现基本I/O操作CS8900A_SendFrame和CS8900A_RecvFrame。EDK中有需付费的以太网IP CORE并附带有一些TCP/IP协议栈,该协议栈实现了大部分常用功能,但也有一些重要功能并未实现,例如TCP包的超时未达重发,收发操作的中断工作方式。通过修改、增加和完善这些软件包,实现了真正面向用户更高层应用软件的网络编程接口。

● 软件开发中的部分问题

软件开发过程中遇到的几个主要问题归纳如下:

(1)IEEE 802.3网络及网络控制器CS8900A采用的均是Little Endian编码,而XC2VP40内含的处理器PowerPC 405D5采用的是Big Endian编码方式,因此在数据I/O过程中需要做一下转换。

(2)可通过编写链接控制脚本文件控制应用程序的链接过程,从而控制程序映像在存储器中的重定位过程。这在FPGA这种存储器资源有限的环境中有时很有用。

(3)要将EDK提供的默认bootloop程序打包到硬件初始化流中,这样做的目的是提供默认的CPU复位后运行程序,保证CPU处在可预知的状态,而不是因为执行了存储器中的随机代码而处于一种未知的状态。

系统调试方法

由于PowerPC 405处理器核中已包含调试模块,并用JTAG端口引出,只要在系统中添加一个叫做JTAGPPC的IP模块并和PowerPC 405相连便可将其调试端口串入FPGA的JTAG链中,这样只需使用FPGA本身的下载电缆和JTAG接口便可完成系统软件调试而不需要增加额外电路。

EDK提供的软件调试工具主要有XMD和GDB。值得一提的是利用XMD下载可执行程序映像时还会显示各程序段的重定位情况,在发生错误时会报告错误,诸如要求的地址空间大于实际提供的地址空间等错误,而这在EDK集成环境下是看不到的。在存在多种类型存储器资源的情况下,编写链接控制脚本文件控制重定位过程可能能够解决上述某地址空间不够的问题。网络通信部分的调试主要由Sniffer软件辅助完成。

GDB是EDK附带的GNU的主机方图形界面调试工具,它通过和XMD通信完成图形界面调试功能,此时XMD则扮演了一个主机方调试代理的角色,所有的调试通信是由XMD同目标机通信完成的。

结语

SoPC使得硬件设计能真正实现象搭积木一样方便迅速,而利用EDK开发工具就可以实现一个基于FPGA的嵌入式系统的软硬件一体化的开发,的确大大提高了嵌入式系统的开发效率,但是目前它还有许多不够完善的方面。

首先是系统设计对设计工具软件的依赖性很大,而这些软件还有许多有待修正完善的地方,设计师无法避免将在使用熟悉软件方面花许多时间。其次,IP Core的不断丰富和完善是SoPC的基础,昂贵的付费IP核不利于此技术的推广,尤其在国内,而要设计验证用户自己的IP Core对设计者的要求较高。如今一个完善的嵌入式系统都有实时操作系统在运行,SoPC要成为主流也需要更丰富的RTOS的支持。

引用地址:基于嵌入式SoPC的以太网接口设备

图1 系统硬件组成框图

PowerPC 405是此嵌入式系统的核心,它通过PLB总线实现和程序存储器和数据存储器的快速通道,并通过PLB-OPB桥实现了片上的OPB总线,然后通过OPB总线进行各种外设的扩展,OPB外设包括一个RS232串口,一个OPB_EMC用于扩展以太网控制器芯片,一个GPIO作以太网控制器输出的中断请求,一个中断控制器OPB_INTC将GPIO输入的外部中断通知PowerPC 405并可以设置优先级,还有一个用户自定义的IP Core用于实现和VME总线的接口电路。

PowerPC 405 是专门为嵌入式应用而设计的高性能32位PowerPC系列处理器芯核,对于Virtex-II Pro系列FPGA,其实现型号为PowerPC 405D5。

PLB是处理器本机总线,它为指令和数据一侧提供独立的32位地址和64位数据总线。PLB总线架构支持多主从设备,每一个PLB主控机通过独立的地址总线、读数据总线和写数据总线与PLB连接,有一个中央判决机构来授权对PLB的访问以允许主控机通过竞争来获得总线的所有权。OPB是片上外设总线,提供分离的32位地址总线和32位数据总线,一般用来访问低速和低性能的系统资源。它是一种完全同步总线,但不直接连接到处理器内核,处理器内核通过“PLB to OPB”桥和OPB总线来访问OPB接口外设。

网络控制器采用Cirrus Logic公司的通用单片10/100M以太网控制器CS8900A,该芯片完全遵从与IEEE 802.3以太网标准,支持完全的全双工操作。应用EDK的OPB_EMC IP可以很方便地将CS8900A扩展为系统OPB总线上的一个设备,只要将EMC端口的地址、数据总线以及控制信号分别接到CS8900A的地址、数据总线和控制端口上,并将EMC的时序参数设置成与CS8900A手册上要求的一致就可以了。另外将CS8900A的中断输出INTRQ作为一个GPIO引入系统以实现以太网的中断服务功能。

自定义的IP Core内容如图2所示,它用FPGA内的Block RAM资源实现64KB的双口RAM用来完成和VME总线上其他设备的通信和数据交换。我们用上述的第二种方法来实现将用户专用电路嵌入微处理器系统中,自定义的IP主要包括OPB总线接口和用户电路两部分,我们用EDK提供的OPB总线的IPIF模板修改后,作为自定义IP的总线接口,64KB的双口RAM和VME总线接口是真正的用户电路。

图1 系统硬件组成框图

PowerPC 405是此嵌入式系统的核心,它通过PLB总线实现和程序存储器和数据存储器的快速通道,并通过PLB-OPB桥实现了片上的OPB总线,然后通过OPB总线进行各种外设的扩展,OPB外设包括一个RS232串口,一个OPB_EMC用于扩展以太网控制器芯片,一个GPIO作以太网控制器输出的中断请求,一个中断控制器OPB_INTC将GPIO输入的外部中断通知PowerPC 405并可以设置优先级,还有一个用户自定义的IP Core用于实现和VME总线的接口电路。

PowerPC 405 是专门为嵌入式应用而设计的高性能32位PowerPC系列处理器芯核,对于Virtex-II Pro系列FPGA,其实现型号为PowerPC 405D5。

PLB是处理器本机总线,它为指令和数据一侧提供独立的32位地址和64位数据总线。PLB总线架构支持多主从设备,每一个PLB主控机通过独立的地址总线、读数据总线和写数据总线与PLB连接,有一个中央判决机构来授权对PLB的访问以允许主控机通过竞争来获得总线的所有权。OPB是片上外设总线,提供分离的32位地址总线和32位数据总线,一般用来访问低速和低性能的系统资源。它是一种完全同步总线,但不直接连接到处理器内核,处理器内核通过“PLB to OPB”桥和OPB总线来访问OPB接口外设。

网络控制器采用Cirrus Logic公司的通用单片10/100M以太网控制器CS8900A,该芯片完全遵从与IEEE 802.3以太网标准,支持完全的全双工操作。应用EDK的OPB_EMC IP可以很方便地将CS8900A扩展为系统OPB总线上的一个设备,只要将EMC端口的地址、数据总线以及控制信号分别接到CS8900A的地址、数据总线和控制端口上,并将EMC的时序参数设置成与CS8900A手册上要求的一致就可以了。另外将CS8900A的中断输出INTRQ作为一个GPIO引入系统以实现以太网的中断服务功能。

自定义的IP Core内容如图2所示,它用FPGA内的Block RAM资源实现64KB的双口RAM用来完成和VME总线上其他设备的通信和数据交换。我们用上述的第二种方法来实现将用户专用电路嵌入微处理器系统中,自定义的IP主要包括OPB总线接口和用户电路两部分,我们用EDK提供的OPB总线的IPIF模板修改后,作为自定义IP的总线接口,64KB的双口RAM和VME总线接口是真正的用户电路。

图2 自定义的IP Core结构

软件开发

嵌入式开发环境EDK(Embedded Development Kit)将软件开发分为两大部分,一是底层系统软件的开发,主要完成BSP(板级支持包)的功能;另一部分则是用户应用软件的开发(包括用户硬件驱动及用户上层应用软件)。由于EDK中带有许多IP核以及相应的驱动软件,因此底层系统软件的开发大部分可以借助EDK集成开发环境来完成的,如操作系统的选择、设备驱动程序的选择、中断/异常处理例程的设置、操作系统参数设置等在内的各种系统级软件参数的设置。而用户应用软件的开发由于有底层驱动的隔离,可移植性好。整个用户软件的开发及调试工作都可以在EDK中完成。

● 底层系统软件开发

在本设计中,没有使用操作系统,使用所谓的standalone模式,即EDK仅提供硬件初始化及引导代码。此外还需要对GPIO、EMC、RS232、中断控制器等一些外设生成底层驱动,这些都可以通过在EDK集成环境XPS中选择菜单Project->Software Platform Settings的对话框进行设置,如图3所示。其实质是自动修改工程的.MSS文件。例如中断函数的处理例程可在如图4所示的界面中加以设置。也可以手工编辑.MSS文件如下设置:

PARAMETER int_handler = CS8900A_INT_HANDLER, int_port = IP2INTC_Irpt

图2 自定义的IP Core结构

软件开发

嵌入式开发环境EDK(Embedded Development Kit)将软件开发分为两大部分,一是底层系统软件的开发,主要完成BSP(板级支持包)的功能;另一部分则是用户应用软件的开发(包括用户硬件驱动及用户上层应用软件)。由于EDK中带有许多IP核以及相应的驱动软件,因此底层系统软件的开发大部分可以借助EDK集成开发环境来完成的,如操作系统的选择、设备驱动程序的选择、中断/异常处理例程的设置、操作系统参数设置等在内的各种系统级软件参数的设置。而用户应用软件的开发由于有底层驱动的隔离,可移植性好。整个用户软件的开发及调试工作都可以在EDK中完成。

● 底层系统软件开发

在本设计中,没有使用操作系统,使用所谓的standalone模式,即EDK仅提供硬件初始化及引导代码。此外还需要对GPIO、EMC、RS232、中断控制器等一些外设生成底层驱动,这些都可以通过在EDK集成环境XPS中选择菜单Project->Software Platform Settings的对话框进行设置,如图3所示。其实质是自动修改工程的.MSS文件。例如中断函数的处理例程可在如图4所示的界面中加以设置。也可以手工编辑.MSS文件如下设置:

PARAMETER int_handler = CS8900A_INT_HANDLER, int_port = IP2INTC_Irpt

图3 在XPS中设置操作系统和驱动程序

图3 在XPS中设置操作系统和驱动程序

图4 在XPS中设置中断服务例程

设置完成后在XPS中运行Tools->Generate Libraries and BSPs将调用LibGen自动生成驱动库文件,这些CPU和外设驱动库的设置、操作函数实现或定义可在工程项目根目录下的以处理器实例名为名字的目录下的libsrc目录下相应的各模块子目录中找到,参考其实现有助于深刻理解事实上发生的操作。例如中断向量表可在中段向量控制器模块子目录(本例中为intc_v1_00_csrc)下的xintc_g.c文件中找到。

● 用户软件开发

用户软件主要是对网络控制器、GPIO、RS232串口等的操作,其中控制CS8900A的程序是重要部分,它要完成TCP/IP协议。CS8900A所有的控制寄存器和数据寄存器都映射在被称为PacketPage的片上4K地址空间内,这4K空间可映射到主机地址空间中(存储器模式),或通过8个16位I/O口进行存取(I/O模式)。本设计中CS8900A工作于I/O模式,通过EDK的OPB_EMC IP作为OPB总线上的一个设备,并给EMC控制器和所映射的设备分配操作地址空间,在程序中用

Xuint32 XIo_In32(XIo_Address InAddress);

void XIo_Out32(XIo_Address OutAddress, Xuint32 Value);

读写映射的设备,这两个I/O函数同*pDestMem = Value(直接读写存储器操作)的差别在于前者做了读写同步(调用eieio汇编指令)。参考芯片手册编写CS8900A的驱动,实现基本I/O操作CS8900A_SendFrame和CS8900A_RecvFrame。EDK中有需付费的以太网IP CORE并附带有一些TCP/IP协议栈,该协议栈实现了大部分常用功能,但也有一些重要功能并未实现,例如TCP包的超时未达重发,收发操作的中断工作方式。通过修改、增加和完善这些软件包,实现了真正面向用户更高层应用软件的网络编程接口。

● 软件开发中的部分问题

软件开发过程中遇到的几个主要问题归纳如下:

(1)IEEE 802.3网络及网络控制器CS8900A采用的均是Little Endian编码,而XC2VP40内含的处理器PowerPC 405D5采用的是Big Endian编码方式,因此在数据I/O过程中需要做一下转换。

(2)可通过编写链接控制脚本文件控制应用程序的链接过程,从而控制程序映像在存储器中的重定位过程。这在FPGA这种存储器资源有限的环境中有时很有用。

(3)要将EDK提供的默认bootloop程序打包到硬件初始化流中,这样做的目的是提供默认的CPU复位后运行程序,保证CPU处在可预知的状态,而不是因为执行了存储器中的随机代码而处于一种未知的状态。

系统调试方法

由于PowerPC 405处理器核中已包含调试模块,并用JTAG端口引出,只要在系统中添加一个叫做JTAGPPC的IP模块并和PowerPC 405相连便可将其调试端口串入FPGA的JTAG链中,这样只需使用FPGA本身的下载电缆和JTAG接口便可完成系统软件调试而不需要增加额外电路。

EDK提供的软件调试工具主要有XMD和GDB。值得一提的是利用XMD下载可执行程序映像时还会显示各程序段的重定位情况,在发生错误时会报告错误,诸如要求的地址空间大于实际提供的地址空间等错误,而这在EDK集成环境下是看不到的。在存在多种类型存储器资源的情况下,编写链接控制脚本文件控制重定位过程可能能够解决上述某地址空间不够的问题。网络通信部分的调试主要由Sniffer软件辅助完成。

GDB是EDK附带的GNU的主机方图形界面调试工具,它通过和XMD通信完成图形界面调试功能,此时XMD则扮演了一个主机方调试代理的角色,所有的调试通信是由XMD同目标机通信完成的。

结语

SoPC使得硬件设计能真正实现象搭积木一样方便迅速,而利用EDK开发工具就可以实现一个基于FPGA的嵌入式系统的软硬件一体化的开发,的确大大提高了嵌入式系统的开发效率,但是目前它还有许多不够完善的方面。

首先是系统设计对设计工具软件的依赖性很大,而这些软件还有许多有待修正完善的地方,设计师无法避免将在使用熟悉软件方面花许多时间。其次,IP Core的不断丰富和完善是SoPC的基础,昂贵的付费IP核不利于此技术的推广,尤其在国内,而要设计验证用户自己的IP Core对设计者的要求较高。如今一个完善的嵌入式系统都有实时操作系统在运行,SoPC要成为主流也需要更丰富的RTOS的支持。

图4 在XPS中设置中断服务例程

设置完成后在XPS中运行Tools->Generate Libraries and BSPs将调用LibGen自动生成驱动库文件,这些CPU和外设驱动库的设置、操作函数实现或定义可在工程项目根目录下的以处理器实例名为名字的目录下的libsrc目录下相应的各模块子目录中找到,参考其实现有助于深刻理解事实上发生的操作。例如中断向量表可在中段向量控制器模块子目录(本例中为intc_v1_00_csrc)下的xintc_g.c文件中找到。

● 用户软件开发

用户软件主要是对网络控制器、GPIO、RS232串口等的操作,其中控制CS8900A的程序是重要部分,它要完成TCP/IP协议。CS8900A所有的控制寄存器和数据寄存器都映射在被称为PacketPage的片上4K地址空间内,这4K空间可映射到主机地址空间中(存储器模式),或通过8个16位I/O口进行存取(I/O模式)。本设计中CS8900A工作于I/O模式,通过EDK的OPB_EMC IP作为OPB总线上的一个设备,并给EMC控制器和所映射的设备分配操作地址空间,在程序中用

Xuint32 XIo_In32(XIo_Address InAddress);

void XIo_Out32(XIo_Address OutAddress, Xuint32 Value);

读写映射的设备,这两个I/O函数同*pDestMem = Value(直接读写存储器操作)的差别在于前者做了读写同步(调用eieio汇编指令)。参考芯片手册编写CS8900A的驱动,实现基本I/O操作CS8900A_SendFrame和CS8900A_RecvFrame。EDK中有需付费的以太网IP CORE并附带有一些TCP/IP协议栈,该协议栈实现了大部分常用功能,但也有一些重要功能并未实现,例如TCP包的超时未达重发,收发操作的中断工作方式。通过修改、增加和完善这些软件包,实现了真正面向用户更高层应用软件的网络编程接口。

● 软件开发中的部分问题

软件开发过程中遇到的几个主要问题归纳如下:

(1)IEEE 802.3网络及网络控制器CS8900A采用的均是Little Endian编码,而XC2VP40内含的处理器PowerPC 405D5采用的是Big Endian编码方式,因此在数据I/O过程中需要做一下转换。

(2)可通过编写链接控制脚本文件控制应用程序的链接过程,从而控制程序映像在存储器中的重定位过程。这在FPGA这种存储器资源有限的环境中有时很有用。

(3)要将EDK提供的默认bootloop程序打包到硬件初始化流中,这样做的目的是提供默认的CPU复位后运行程序,保证CPU处在可预知的状态,而不是因为执行了存储器中的随机代码而处于一种未知的状态。

系统调试方法

由于PowerPC 405处理器核中已包含调试模块,并用JTAG端口引出,只要在系统中添加一个叫做JTAGPPC的IP模块并和PowerPC 405相连便可将其调试端口串入FPGA的JTAG链中,这样只需使用FPGA本身的下载电缆和JTAG接口便可完成系统软件调试而不需要增加额外电路。

EDK提供的软件调试工具主要有XMD和GDB。值得一提的是利用XMD下载可执行程序映像时还会显示各程序段的重定位情况,在发生错误时会报告错误,诸如要求的地址空间大于实际提供的地址空间等错误,而这在EDK集成环境下是看不到的。在存在多种类型存储器资源的情况下,编写链接控制脚本文件控制重定位过程可能能够解决上述某地址空间不够的问题。网络通信部分的调试主要由Sniffer软件辅助完成。

GDB是EDK附带的GNU的主机方图形界面调试工具,它通过和XMD通信完成图形界面调试功能,此时XMD则扮演了一个主机方调试代理的角色,所有的调试通信是由XMD同目标机通信完成的。

结语

SoPC使得硬件设计能真正实现象搭积木一样方便迅速,而利用EDK开发工具就可以实现一个基于FPGA的嵌入式系统的软硬件一体化的开发,的确大大提高了嵌入式系统的开发效率,但是目前它还有许多不够完善的方面。

首先是系统设计对设计工具软件的依赖性很大,而这些软件还有许多有待修正完善的地方,设计师无法避免将在使用熟悉软件方面花许多时间。其次,IP Core的不断丰富和完善是SoPC的基础,昂贵的付费IP核不利于此技术的推广,尤其在国内,而要设计验证用户自己的IP Core对设计者的要求较高。如今一个完善的嵌入式系统都有实时操作系统在运行,SoPC要成为主流也需要更丰富的RTOS的支持。

上一篇:嵌入式Linux系统下Microwindows的应用

下一篇:基于TRIMEDIA平台的数字监控DVR的设计实现

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新应用文章

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

- 是德科技电子书 《X-Apps藏宝图: 能够加速测试的信号分析仪必备测量App》下载有好礼!

- 一大波MCU开发板正在靠近,速来——瑞萨电子设计大赛(2015)

- 感谢有你,愿一路同行!——eeworld感恩节送书活动

- 有奖直播【如何在几分钟之内完成高效可靠的USB PD电源设计——PI Expert™分步教程】(9:30开始入场)

- 免费下载 | 注册施耐德电气,下载《施耐德电气参考指南》白皮书

- 安世半导体&世平集团 高效能&小型化, Nexperia MOSFET的5G解决方案 观看、下载 闯关赢好礼!

- 免费下载——Maxim 面向工业应用的参考设计

- 关注EE官方微信,大年初一抢新年红包

- 【有奖知识问答】vishay电感,感动电子生活!

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 ALD2701BDAMXXXX

ALD2701BDAMXXXX

京公网安备 11010802033920号

京公网安备 11010802033920号