循环码是最重要的一类线性分组纠错码,而BCH码又是目前发现的性能很好且应用广泛的循环码,它具有严格的代数理论,对它的理论研究也非常透彻。BCH码的实现途径有软件和硬件两种。软件实现方法灵活性强且较易实现,但硬件实现方法的工作速度快,在高数据速率和长帧应用场合时具有优势。FPGA(现场可编程门阵列)为DSP算法的硬件实现提供了很好的平台,但如果单独使用一片FPGA实现BCH编解码,对成本、功耗和交互速度都不利。最新的SoC(片上系统)设计方法可以很好地解决这个问题。

本文基于Altera公司的Nios软核+可编程资源的SoC平台设计了BCH编解码IP核,这样,在Nios系统中可以将BCH码作为一种片内资源进行调用,在工程设计上具有积极的意义。

1 BCH码

BCH码于1960年前后发明,可以纠检多个错误。通常的二进制BCH码元是取自加罗瓦域GF(2m)。对于参数m和可纠错码元数目t,BCH码的码长为n=2m-1,对于m≥3,t<2m-1的BCH码,监督码元数目n-k=mt;dmin≥2t+1。同时,BCH码元多项式的根为GF(2m)中的元素α,α3,…,α2t+1。例如一个m=6,t=3的BCH码,其参数为:n=63,n-k=18,dmin=7。这就构成了可以纠正3个错误的(63,45)BCH码。

BCH码基于加罗瓦域,BCH编解码的运算也是域内的闭合运算。加罗瓦有限域产生于一个本原多项式,GF(2m)有限域内有2m个元素。以GF(23)域为例,它的本原多项式p(x)假定为p(x)=x3+x+1,基本元素α定义为p(x)=0的根,GF(23)中的元素可以计算如下:

BCH码的编码取决于其生成多项式,令φ2i-1(x)是加罗瓦域元素α2i-1的最小多项式,则可以纠正t个错误的BCH码的生成多项式为:

有了生成多项式,BCH编码与普通的循环码编码相同,使用除法电路可以实现。

一个复杂度较低的BCH译码算法对于BCH码的应用有着重要的意义。BCH译码可以分为伴随式计算和Berlekamp迭代译码两部分。设接收码元多项式为r(x),由于生成多项式的性质,如果传输过程中信道没有引入错误,α,α2,α3,…,α2t应是r(x)的根。因此,伴随式计算即将加罗瓦域中的元素代入接收码元多项式,如果所有伴随式结果都为0,则说明没有错误,否则就有错误。如果只使用BCH码进行检错,则译码过程就结束了。

伴随式计算结束后,如果有错,首先需要计算错误位置多项式δ(x),译码的核心主要集中在这一步上。Berlekamp迭代算法不仅求解了错误位置多项式的关键方程,而且运算速度快,可以说它解决了BCH码译码的工程实用问题。其次,使用钱搜索找出δ(x)的根,即错误位置。最后,由于是二进制编码,只需把相应位置的码元取反就完成了整个译码过程。

2 BCH编解码IP核的设计

2.1 整体设计及CPU接口

在NiosⅡ系统中,平台免费提供了各种常用接口IP核以及对这些外设的驱动程序包,例如UART接口、Flash接口等。作为一个自行设计的IP核,需要挂接在NiosⅡ系统的Avalon总线上。这个过程使用Sopc Builder工具中的Interface t0 user logic模块可以方便地进行设计。NiosⅡ处理器和BCH IP核之间通过Avalon总线使用寄存器映射方式进行交互。图1是整个IP核的实现方框图。

其中与NiosⅡ的接口分为控制接口和数据接口两部分。控制接口包括复位、编解码控制、存储器状态报告和编解码状态报告等。数据接口为FPGA内部的RAM,分为发送和接收两部分,它在NiosⅡ中映射成存储空间。在NiosⅡ和BCH码IP核之间设置简单的数据协议,控制寄存器的起始控制位设置后,写入数据缓存的第1个字节为编解码输入数据的长度字节。BCH编解码模块从数据缓存中读入数据进行相应处理。其中,加罗瓦域的运算主要通过对域元素的查表得到。

2.2 BCH编码

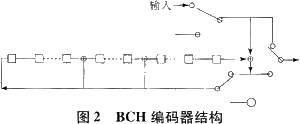

BCH码属于系统码,其编码与一般循环码的编码形式基本相同,即为信息码元多项式与生成多项式之间的除法电路实现。除法电路采用带反馈的移位寄存器完成。信息码元发送完后,寄存器内存储的就是监督码元,再接着发送即可。其中反馈抽头连接为生成多项式控制。其基本结构见图2。

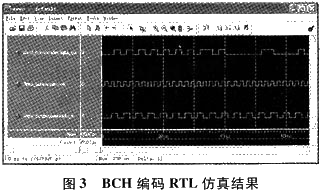

信息码元首先从数据缓存中被读出,然后通过并/串变换进入编码器后,一方面直接输出,同时送入除法电路,当信息码元输入结束后,开关进行相应的变换,存在寄存器中的监督码元输出。图3为(31,16)BCH编码的RTL(寄存器传输级)仿真结果。

2.3 BCH译码

前面已经介绍了BCH迭代译码的基本步骤。译码过程中的运算都为有限域运算,在运算过程中经常计算加罗瓦域的元素是不明智的,查表实现是通用的方法。例如GF(23)中,可以设计表1所示的表格来实现域元素的查找,同时,运算中还经常需要通过元素值反查元素类型,因此需要设计两张表格来正向和反向查找。图1中的GF域查表RAM模块就完成了这个功能。通过以上查表方法可以轻松实现有限域的加、减和乘运算。

首先进行伴随式计算,在设计中利用片内较高的工作频率和FPGA的并发实现优势,同时完成所有伴随式的计算。图4为伴随式计算的RTL仿真结果,当传输引入错误后,伴随式相或的结果Data_Out输出高电平,表示需要进行纠错。

然后进行迭代译码,迭代过程可以通过表2表示。其中μ为算法迭代的次数,第1次为了表示方便,可以认为初始值是0。δμ(x)就是错误位置多项式。dμ是一种差值,用于运算。ιμ是第μ次运算时δμ(x)的多项式阶数,2μ-ιμ是运算中应用的变量。

算法流程步骤如下:

a) 按如上μ为0和-1/2时初始化各个变量。

b) 如果dμ=0,此时,则往下进行。

c) 如果dμ≠0,则寻找以前运算的某一行ρ,其具有2μ-ιμ最大(正值),且dρ≠0。

此时,![]()

如果μ=t-1,则算法结束。

d)ιμ+1=deg(δμ+1(x)),即δμ+1(x)的多项式阶数。

e) dμ+1 =s2μ+3+δ1μ+1s2μ+2+δ2μ+1s2μ+1+…+δLμ+1s2μ+3-L,其中,L为ιμ+1,δu(x)的第i阶系数。

f) 增加μ,从步骤b开始。

得到错误多项式后,通过钱搜索和取反即可完成整个译码工作。

3 结束语

SoC技术以其低成本、低功耗和小体积已经成为电子设计领域的一个重要发展方向。BCH码是一种经典的分组纠错码,在通信系统中应用较为广泛。通过这两者的结合,本文设计的BCH码IP核嵌入NiosSoC中,使得BCH编解码在单片系统中可以自由调用,对SoC中的应用软件而言,调用接口简单,IP核屏蔽了所有算法细节。同时,由于采用硬件实现,具有高速、稳定的特点。

上一篇:利用FPGA实现UART的设计

下一篇:基于FPGA的数字交换系统的设计与实现

推荐阅读最新更新时间:2024-05-13 18:37

新能源电车马达驱动EMC对策电路

新能源电车马达驱动EMC对策电路 ICCV2023论文汇总:First Person (Egocentric) Vision 第一人称视觉(自我中心视觉)

ICCV2023论文汇总:First Person (Egocentric) Vision 第一人称视觉(自我中心视觉) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号