摘要:PCI9052是PLX公司推出的一种PCI总线从属接口芯片(不具有DMA功能)。它提供了方便的本地总线与PCI总线的接口,避免用户直接面对复杂的PCI总线协议。GP2010是通用电器公司Plessey半导体机构为全球定位系统(GPS)接收机设计的第二代射频高频端器件。它将GPS射频信号下变频到4.309MHz的中频(IF)后进行5.714MHz的2bit(A/D)量化。文中主要介绍如何利用PCI9052和GP2010实现GPS信号的量化存储。

关键词:PCI总线 GPS DMA

引言

全球定位系统GPS(Global Position System),可以给用户提供实时的定位、速度和时间信息。现在的GPS接收机大多采用硬件电路进行码相关运算,结构复杂,更新升级比较困难;而基于软件无线电的GPS接收机受电路限制较少,更新换代只需调整相应软件,十分灵活。该数据采集卡就是基于以上考虑设计的。

1 PCI9052的特点与功能

PCI9052(以下简称9052)提供高性能的从目标PCI接口板卡与PCI总线的连接,支持宽范围速率的本地总线,最高可达132

MB/s的传输速率。对9052编程可实现复用/非复用的8位、16位、32位的本地总线接口。9052还有内部FIFO可以加速本地总线的操作,此外它还有以下功能:

①支持PCI r2.1版本,可以方便地将ISA卡转换为PCI卡;

②支持从目标传输模式,可以对存储器空间进行突发读/写,对I/O空间单次访问;

③2个本地中断总线配置;

④可编程的本地总线配置;

⑤串行E2PROM配置;

⑥4个本地片选引脚,5个本地空间;

⑦多种本地读/写操作模式,方便地实现PCI与本地的接口。

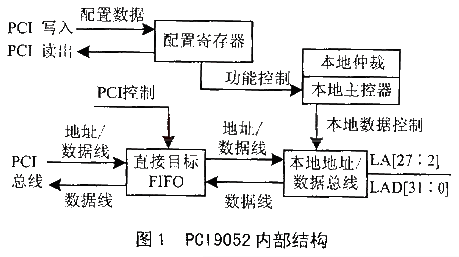

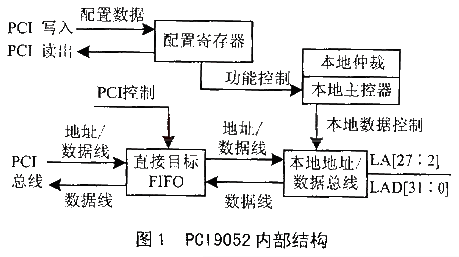

图1给出了9052内部结构。

2 GP2010射频前端器件

GP2010(以下简称2010)是为GPS接收机设计的射频前端器件,它接收GPS(L1)调制信号。L1是50位/Hz的信息码速率经过1.023MHz的伪随机码扩频后以BPSK方式调制在1575.42MHz的载波上形成的扩频信号。信号电平在进入天线之前大约只有-130dB,带宽为2.046MHz,所以L1基本上被噪声所掩盖。2010经过内部锁相环频率综合器产生1.4GHz、140MHz、与31.11MHz的三级时钟分别与射频输入的L1信号进行混频,其中还经过3级滤波抑制带外干扰,最后将其变换到4.309MHz的中频,然后进行5.714MHz的采样实现A/D变换(2位量化,符号位SIGN和数据位MAG)。根据奈奎斯特定律对带通信号要以高于两倍的信号带宽进行采样才可无失真的恢复,用5.714MHz的速率采样也要考虑到信号传播过程中由于相对运动而产生的多普勒效应使信号带宽变宽的缘故。量化数据在每个时钟的上升沿输出。图2给出2010的内部结构图。

图2 GP2010内部结构图

3 数据采集卡系统结构

GPS信号数据采集卡实现基本的一路GPS卫星信号的采集工作。由于2010为2位、5.714MHz的采样速率,我们在FPGA中首先将2位数据进行串并变换,使其每满32位后进行一次传输存储,这样存储速率就变为357.12kHz。缓存选用4片18k%26;#215;16位的FIFO,这样就可以省略地址产生逻辑。在程序设计中,采样数据首先存入FIFO(A),待满后会产生相应的中断,中断服务程序将读取其中的数据。在读过程中,采样数据会继续写入FIFO(B),如此反复可将数据采入计算机内存。选用缓存时,建议在可行的情况下,容量越大越好。因为PCI总线上,除了设计的采集卡在不断地申请占用总线外,还会有其余的设备占用,如果缓存不够大将会丢失采样数据。FPGA的主要功能是实现数据串行变换、控制采样过程和与FIFO的接口逻辑。图3是该数据采集卡的系统框图。

4 9052使用中应该注意的问题

9052内部的配置寄存器是通过外部串行E2PROM上电加载的。9052会自动根据该E2PROM的状态来决定其内部寄存器的值。如果E2PROM不存在(此时E2PROM和9052连接的数据引脚应加上拉电阻)或其内部无有效值,9052会将其内部寄存器配置为缺省值。值得一提的是,如果E2PROM内部没有烧写为有效值时,应保证其开始48位为全“1”;否则,系统上电时可能会产生错误。

9052有5个本地空间,用户可根据实际需要进行相应的配置。当将本地空间配置成I/O时,对该空间的读/写操作只能单次进行。利用PLXMon来开发驱动程序(调用其提供的API函数)进行I/O读/写,速度会十分慢(一般不会超过500kHz);而如配置成存储器空间,用户会有多种接入模式,可大大提高接入速度。

MB/s的传输速率。对9052编程可实现复用/非复用的8位、16位、32位的本地总线接口。9052还有内部FIFO可以加速本地总线的操作,此外它还有以下功能:

①支持PCI r2.1版本,可以方便地将ISA卡转换为PCI卡;

②支持从目标传输模式,可以对存储器空间进行突发读/写,对I/O空间单次访问;

③2个本地中断总线配置;

④可编程的本地总线配置;

⑤串行E2PROM配置;

⑥4个本地片选引脚,5个本地空间;

⑦多种本地读/写操作模式,方便地实现PCI与本地的接口。

图1给出了9052内部结构。

2 GP2010射频前端器件

GP2010(以下简称2010)是为GPS接收机设计的射频前端器件,它接收GPS(L1)调制信号。L1是50位/Hz的信息码速率经过1.023MHz的伪随机码扩频后以BPSK方式调制在1575.42MHz的载波上形成的扩频信号。信号电平在进入天线之前大约只有-130dB,带宽为2.046MHz,所以L1基本上被噪声所掩盖。2010经过内部锁相环频率综合器产生1.4GHz、140MHz、与31.11MHz的三级时钟分别与射频输入的L1信号进行混频,其中还经过3级滤波抑制带外干扰,最后将其变换到4.309MHz的中频,然后进行5.714MHz的采样实现A/D变换(2位量化,符号位SIGN和数据位MAG)。根据奈奎斯特定律对带通信号要以高于两倍的信号带宽进行采样才可无失真的恢复,用5.714MHz的速率采样也要考虑到信号传播过程中由于相对运动而产生的多普勒效应使信号带宽变宽的缘故。量化数据在每个时钟的上升沿输出。图2给出2010的内部结构图。

图2 GP2010内部结构图

3 数据采集卡系统结构

GPS信号数据采集卡实现基本的一路GPS卫星信号的采集工作。由于2010为2位、5.714MHz的采样速率,我们在FPGA中首先将2位数据进行串并变换,使其每满32位后进行一次传输存储,这样存储速率就变为357.12kHz。缓存选用4片18k%26;#215;16位的FIFO,这样就可以省略地址产生逻辑。在程序设计中,采样数据首先存入FIFO(A),待满后会产生相应的中断,中断服务程序将读取其中的数据。在读过程中,采样数据会继续写入FIFO(B),如此反复可将数据采入计算机内存。选用缓存时,建议在可行的情况下,容量越大越好。因为PCI总线上,除了设计的采集卡在不断地申请占用总线外,还会有其余的设备占用,如果缓存不够大将会丢失采样数据。FPGA的主要功能是实现数据串行变换、控制采样过程和与FIFO的接口逻辑。图3是该数据采集卡的系统框图。

4 9052使用中应该注意的问题

9052内部的配置寄存器是通过外部串行E2PROM上电加载的。9052会自动根据该E2PROM的状态来决定其内部寄存器的值。如果E2PROM不存在(此时E2PROM和9052连接的数据引脚应加上拉电阻)或其内部无有效值,9052会将其内部寄存器配置为缺省值。值得一提的是,如果E2PROM内部没有烧写为有效值时,应保证其开始48位为全“1”;否则,系统上电时可能会产生错误。

9052有5个本地空间,用户可根据实际需要进行相应的配置。当将本地空间配置成I/O时,对该空间的读/写操作只能单次进行。利用PLXMon来开发驱动程序(调用其提供的API函数)进行I/O读/写,速度会十分慢(一般不会超过500kHz);而如配置成存储器空间,用户会有多种接入模式,可大大提高接入速度。

突发模式是为提高本地总线操作速度而设计的。在该模式期间,9052只提供一次传输开始和终止信号。开始信号有效后,地址将以本地时钟的频率(最高可达40MHz)递增,可以利用Bterm#引脚是否有效来终止突发操作。由于FIFO只需要一个口地址,在设计中为了利用其快速的存储器访问(突发访问)特性,我们还是为其分配了36KB的地址空间,以保证在该范围内FIFO的片选始终有效。图4是一次突发读时序。其中LCLK是本地时钟,ADS有效表示一次传输的开始,BLAST有效表示本次传输的终止。

在此须澄清一个概念:Pentium系列计算机(指CPU),不支持突发读操作,只可能产生单次读操作。用户若想在PCI总线上实现突发操作(FRAME信号有效,多余一个PCI时钟周期),应使用支持DMA传输的芯片,如PLX9054。但9052会将PCI总线上的多次单次读操作转化为本地空间上的突发操作。

5 PLXMon及PLX器件驱动程序的开发

PLXMon是PLX公司专为其产品开发的测试软件。在用户的板卡插入PCI槽,并安装了PLXMon提供的驱动程序后,启动该软件就可以观察和修改芯片内部寄存器的值,并可以对存储器空间进行测试。

Windows下的驱动程序包括硬件物理设备的驱动程序和文件系统等非物理设备的虚拟设备驱动程序,我们所编写的是硬件物理设备的驱动程序。Windows类操作系统(Windows 95、Windows 98、WindowsNT、Windows 2000)为了保证其安全性、稳定性和可移植性,对应用程序访问硬件资源加以限制,用户需要对系统硬件及操作系统软件有详细的了解才可开发出高效的驱动程序,因此开发周期较长。利用第三方提供的开发软件,可以大大缩短开发时间,但效率不一定高,尤其对实时性要求严格的程序显得有些无力。

①Device Developer Kit(DDK)。该软件中包括了有关设备驱动开发的文档、编译需要的头文件和库文件、调试工具和程序范例;但是由于DDK主要是使用汇编语言进行描述,开发起来比较困难。

②VtoolsD。该软件包是基于C/C++的,支持BorlandC++和VisualC++,使用和维护比较方便。

③WinDriver。允许用户使用Visual C++、Borland或者其它Win32编程工具软件在用户模式(UserMode)上编写设备驱动程序。

④PLXMon。PLX公司专为其芯片提供的驱动程序开发包和测试软件,同样可以在用户模式上编写。支持Visual C++环境。

图4 突发读时序

在开发程序时,我们发现PLXMon和WinDriver不兼容,而且除非有正式版本的WinDriver;否则试用期过后,利用它开发的驱动程序将无法使用。所以建立使用PLXMon,只需包括相应的头文件,用户便可以方便地调用其提供的API函数,对板卡上的资源进行访问。以下的程序片段是在调试电路板时编写的基本查询中断是否有效来读取缓存的。所调用的函数均为PLXMon提供的API函数。其中:PlxPciBaseAddressesGet()是得到板卡上存储空间的物理地址,而*(Data+i)=*(U32*)(va.Va3)是将该空间的值装入计算机内存。

图5是驱动程序流程图。

程序段如下:

Example:

rc_w=PlxPciBaseAddressesGet(hDevice,%26;amp;va);

while(TRUE){

Int_Flag=*(U32*)(va.Va0+0x4c);

if(Int_Flag[0]%26;amp;4) {

突发模式是为提高本地总线操作速度而设计的。在该模式期间,9052只提供一次传输开始和终止信号。开始信号有效后,地址将以本地时钟的频率(最高可达40MHz)递增,可以利用Bterm#引脚是否有效来终止突发操作。由于FIFO只需要一个口地址,在设计中为了利用其快速的存储器访问(突发访问)特性,我们还是为其分配了36KB的地址空间,以保证在该范围内FIFO的片选始终有效。图4是一次突发读时序。其中LCLK是本地时钟,ADS有效表示一次传输的开始,BLAST有效表示本次传输的终止。

在此须澄清一个概念:Pentium系列计算机(指CPU),不支持突发读操作,只可能产生单次读操作。用户若想在PCI总线上实现突发操作(FRAME信号有效,多余一个PCI时钟周期),应使用支持DMA传输的芯片,如PLX9054。但9052会将PCI总线上的多次单次读操作转化为本地空间上的突发操作。

5 PLXMon及PLX器件驱动程序的开发

PLXMon是PLX公司专为其产品开发的测试软件。在用户的板卡插入PCI槽,并安装了PLXMon提供的驱动程序后,启动该软件就可以观察和修改芯片内部寄存器的值,并可以对存储器空间进行测试。

Windows下的驱动程序包括硬件物理设备的驱动程序和文件系统等非物理设备的虚拟设备驱动程序,我们所编写的是硬件物理设备的驱动程序。Windows类操作系统(Windows 95、Windows 98、WindowsNT、Windows 2000)为了保证其安全性、稳定性和可移植性,对应用程序访问硬件资源加以限制,用户需要对系统硬件及操作系统软件有详细的了解才可开发出高效的驱动程序,因此开发周期较长。利用第三方提供的开发软件,可以大大缩短开发时间,但效率不一定高,尤其对实时性要求严格的程序显得有些无力。

①Device Developer Kit(DDK)。该软件中包括了有关设备驱动开发的文档、编译需要的头文件和库文件、调试工具和程序范例;但是由于DDK主要是使用汇编语言进行描述,开发起来比较困难。

②VtoolsD。该软件包是基于C/C++的,支持BorlandC++和VisualC++,使用和维护比较方便。

③WinDriver。允许用户使用Visual C++、Borland或者其它Win32编程工具软件在用户模式(UserMode)上编写设备驱动程序。

④PLXMon。PLX公司专为其芯片提供的驱动程序开发包和测试软件,同样可以在用户模式上编写。支持Visual C++环境。

图4 突发读时序

在开发程序时,我们发现PLXMon和WinDriver不兼容,而且除非有正式版本的WinDriver;否则试用期过后,利用它开发的驱动程序将无法使用。所以建立使用PLXMon,只需包括相应的头文件,用户便可以方便地调用其提供的API函数,对板卡上的资源进行访问。以下的程序片段是在调试电路板时编写的基本查询中断是否有效来读取缓存的。所调用的函数均为PLXMon提供的API函数。其中:PlxPciBaseAddressesGet()是得到板卡上存储空间的物理地址,而*(Data+i)=*(U32*)(va.Va3)是将该空间的值装入计算机内存。

图5是驱动程序流程图。

程序段如下:

Example:

rc_w=PlxPciBaseAddressesGet(hDevice,%26;amp;va);

while(TRUE){

Int_Flag=*(U32*)(va.Va0+0x4c);

if(Int_Flag[0]%26;amp;4) {

for(i=0;i

for(i=0;i

引用地址:采用PCI9052及GP2010实现GPS信号采集

MB/s的传输速率。对9052编程可实现复用/非复用的8位、16位、32位的本地总线接口。9052还有内部FIFO可以加速本地总线的操作,此外它还有以下功能:

①支持PCI r2.1版本,可以方便地将ISA卡转换为PCI卡;

②支持从目标传输模式,可以对存储器空间进行突发读/写,对I/O空间单次访问;

③2个本地中断总线配置;

④可编程的本地总线配置;

⑤串行E2PROM配置;

⑥4个本地片选引脚,5个本地空间;

⑦多种本地读/写操作模式,方便地实现PCI与本地的接口。

图1给出了9052内部结构。

2 GP2010射频前端器件

GP2010(以下简称2010)是为GPS接收机设计的射频前端器件,它接收GPS(L1)调制信号。L1是50位/Hz的信息码速率经过1.023MHz的伪随机码扩频后以BPSK方式调制在1575.42MHz的载波上形成的扩频信号。信号电平在进入天线之前大约只有-130dB,带宽为2.046MHz,所以L1基本上被噪声所掩盖。2010经过内部锁相环频率综合器产生1.4GHz、140MHz、与31.11MHz的三级时钟分别与射频输入的L1信号进行混频,其中还经过3级滤波抑制带外干扰,最后将其变换到4.309MHz的中频,然后进行5.714MHz的采样实现A/D变换(2位量化,符号位SIGN和数据位MAG)。根据奈奎斯特定律对带通信号要以高于两倍的信号带宽进行采样才可无失真的恢复,用5.714MHz的速率采样也要考虑到信号传播过程中由于相对运动而产生的多普勒效应使信号带宽变宽的缘故。量化数据在每个时钟的上升沿输出。图2给出2010的内部结构图。

图2 GP2010内部结构图

3 数据采集卡系统结构

GPS信号数据采集卡实现基本的一路GPS卫星信号的采集工作。由于2010为2位、5.714MHz的采样速率,我们在FPGA中首先将2位数据进行串并变换,使其每满32位后进行一次传输存储,这样存储速率就变为357.12kHz。缓存选用4片18k%26;#215;16位的FIFO,这样就可以省略地址产生逻辑。在程序设计中,采样数据首先存入FIFO(A),待满后会产生相应的中断,中断服务程序将读取其中的数据。在读过程中,采样数据会继续写入FIFO(B),如此反复可将数据采入计算机内存。选用缓存时,建议在可行的情况下,容量越大越好。因为PCI总线上,除了设计的采集卡在不断地申请占用总线外,还会有其余的设备占用,如果缓存不够大将会丢失采样数据。FPGA的主要功能是实现数据串行变换、控制采样过程和与FIFO的接口逻辑。图3是该数据采集卡的系统框图。

4 9052使用中应该注意的问题

9052内部的配置寄存器是通过外部串行E2PROM上电加载的。9052会自动根据该E2PROM的状态来决定其内部寄存器的值。如果E2PROM不存在(此时E2PROM和9052连接的数据引脚应加上拉电阻)或其内部无有效值,9052会将其内部寄存器配置为缺省值。值得一提的是,如果E2PROM内部没有烧写为有效值时,应保证其开始48位为全“1”;否则,系统上电时可能会产生错误。

9052有5个本地空间,用户可根据实际需要进行相应的配置。当将本地空间配置成I/O时,对该空间的读/写操作只能单次进行。利用PLXMon来开发驱动程序(调用其提供的API函数)进行I/O读/写,速度会十分慢(一般不会超过500kHz);而如配置成存储器空间,用户会有多种接入模式,可大大提高接入速度。

MB/s的传输速率。对9052编程可实现复用/非复用的8位、16位、32位的本地总线接口。9052还有内部FIFO可以加速本地总线的操作,此外它还有以下功能:

①支持PCI r2.1版本,可以方便地将ISA卡转换为PCI卡;

②支持从目标传输模式,可以对存储器空间进行突发读/写,对I/O空间单次访问;

③2个本地中断总线配置;

④可编程的本地总线配置;

⑤串行E2PROM配置;

⑥4个本地片选引脚,5个本地空间;

⑦多种本地读/写操作模式,方便地实现PCI与本地的接口。

图1给出了9052内部结构。

2 GP2010射频前端器件

GP2010(以下简称2010)是为GPS接收机设计的射频前端器件,它接收GPS(L1)调制信号。L1是50位/Hz的信息码速率经过1.023MHz的伪随机码扩频后以BPSK方式调制在1575.42MHz的载波上形成的扩频信号。信号电平在进入天线之前大约只有-130dB,带宽为2.046MHz,所以L1基本上被噪声所掩盖。2010经过内部锁相环频率综合器产生1.4GHz、140MHz、与31.11MHz的三级时钟分别与射频输入的L1信号进行混频,其中还经过3级滤波抑制带外干扰,最后将其变换到4.309MHz的中频,然后进行5.714MHz的采样实现A/D变换(2位量化,符号位SIGN和数据位MAG)。根据奈奎斯特定律对带通信号要以高于两倍的信号带宽进行采样才可无失真的恢复,用5.714MHz的速率采样也要考虑到信号传播过程中由于相对运动而产生的多普勒效应使信号带宽变宽的缘故。量化数据在每个时钟的上升沿输出。图2给出2010的内部结构图。

图2 GP2010内部结构图

3 数据采集卡系统结构

GPS信号数据采集卡实现基本的一路GPS卫星信号的采集工作。由于2010为2位、5.714MHz的采样速率,我们在FPGA中首先将2位数据进行串并变换,使其每满32位后进行一次传输存储,这样存储速率就变为357.12kHz。缓存选用4片18k%26;#215;16位的FIFO,这样就可以省略地址产生逻辑。在程序设计中,采样数据首先存入FIFO(A),待满后会产生相应的中断,中断服务程序将读取其中的数据。在读过程中,采样数据会继续写入FIFO(B),如此反复可将数据采入计算机内存。选用缓存时,建议在可行的情况下,容量越大越好。因为PCI总线上,除了设计的采集卡在不断地申请占用总线外,还会有其余的设备占用,如果缓存不够大将会丢失采样数据。FPGA的主要功能是实现数据串行变换、控制采样过程和与FIFO的接口逻辑。图3是该数据采集卡的系统框图。

4 9052使用中应该注意的问题

9052内部的配置寄存器是通过外部串行E2PROM上电加载的。9052会自动根据该E2PROM的状态来决定其内部寄存器的值。如果E2PROM不存在(此时E2PROM和9052连接的数据引脚应加上拉电阻)或其内部无有效值,9052会将其内部寄存器配置为缺省值。值得一提的是,如果E2PROM内部没有烧写为有效值时,应保证其开始48位为全“1”;否则,系统上电时可能会产生错误。

9052有5个本地空间,用户可根据实际需要进行相应的配置。当将本地空间配置成I/O时,对该空间的读/写操作只能单次进行。利用PLXMon来开发驱动程序(调用其提供的API函数)进行I/O读/写,速度会十分慢(一般不会超过500kHz);而如配置成存储器空间,用户会有多种接入模式,可大大提高接入速度。

突发模式是为提高本地总线操作速度而设计的。在该模式期间,9052只提供一次传输开始和终止信号。开始信号有效后,地址将以本地时钟的频率(最高可达40MHz)递增,可以利用Bterm#引脚是否有效来终止突发操作。由于FIFO只需要一个口地址,在设计中为了利用其快速的存储器访问(突发访问)特性,我们还是为其分配了36KB的地址空间,以保证在该范围内FIFO的片选始终有效。图4是一次突发读时序。其中LCLK是本地时钟,ADS有效表示一次传输的开始,BLAST有效表示本次传输的终止。

在此须澄清一个概念:Pentium系列计算机(指CPU),不支持突发读操作,只可能产生单次读操作。用户若想在PCI总线上实现突发操作(FRAME信号有效,多余一个PCI时钟周期),应使用支持DMA传输的芯片,如PLX9054。但9052会将PCI总线上的多次单次读操作转化为本地空间上的突发操作。

5 PLXMon及PLX器件驱动程序的开发

PLXMon是PLX公司专为其产品开发的测试软件。在用户的板卡插入PCI槽,并安装了PLXMon提供的驱动程序后,启动该软件就可以观察和修改芯片内部寄存器的值,并可以对存储器空间进行测试。

Windows下的驱动程序包括硬件物理设备的驱动程序和文件系统等非物理设备的虚拟设备驱动程序,我们所编写的是硬件物理设备的驱动程序。Windows类操作系统(Windows 95、Windows 98、WindowsNT、Windows 2000)为了保证其安全性、稳定性和可移植性,对应用程序访问硬件资源加以限制,用户需要对系统硬件及操作系统软件有详细的了解才可开发出高效的驱动程序,因此开发周期较长。利用第三方提供的开发软件,可以大大缩短开发时间,但效率不一定高,尤其对实时性要求严格的程序显得有些无力。

①Device Developer Kit(DDK)。该软件中包括了有关设备驱动开发的文档、编译需要的头文件和库文件、调试工具和程序范例;但是由于DDK主要是使用汇编语言进行描述,开发起来比较困难。

②VtoolsD。该软件包是基于C/C++的,支持BorlandC++和VisualC++,使用和维护比较方便。

③WinDriver。允许用户使用Visual C++、Borland或者其它Win32编程工具软件在用户模式(UserMode)上编写设备驱动程序。

④PLXMon。PLX公司专为其芯片提供的驱动程序开发包和测试软件,同样可以在用户模式上编写。支持Visual C++环境。

图4 突发读时序

在开发程序时,我们发现PLXMon和WinDriver不兼容,而且除非有正式版本的WinDriver;否则试用期过后,利用它开发的驱动程序将无法使用。所以建立使用PLXMon,只需包括相应的头文件,用户便可以方便地调用其提供的API函数,对板卡上的资源进行访问。以下的程序片段是在调试电路板时编写的基本查询中断是否有效来读取缓存的。所调用的函数均为PLXMon提供的API函数。其中:PlxPciBaseAddressesGet()是得到板卡上存储空间的物理地址,而*(Data+i)=*(U32*)(va.Va3)是将该空间的值装入计算机内存。

图5是驱动程序流程图。

程序段如下:

Example:

rc_w=PlxPciBaseAddressesGet(hDevice,%26;amp;va);

while(TRUE){

Int_Flag=*(U32*)(va.Va0+0x4c);

if(Int_Flag[0]%26;amp;4) {

突发模式是为提高本地总线操作速度而设计的。在该模式期间,9052只提供一次传输开始和终止信号。开始信号有效后,地址将以本地时钟的频率(最高可达40MHz)递增,可以利用Bterm#引脚是否有效来终止突发操作。由于FIFO只需要一个口地址,在设计中为了利用其快速的存储器访问(突发访问)特性,我们还是为其分配了36KB的地址空间,以保证在该范围内FIFO的片选始终有效。图4是一次突发读时序。其中LCLK是本地时钟,ADS有效表示一次传输的开始,BLAST有效表示本次传输的终止。

在此须澄清一个概念:Pentium系列计算机(指CPU),不支持突发读操作,只可能产生单次读操作。用户若想在PCI总线上实现突发操作(FRAME信号有效,多余一个PCI时钟周期),应使用支持DMA传输的芯片,如PLX9054。但9052会将PCI总线上的多次单次读操作转化为本地空间上的突发操作。

5 PLXMon及PLX器件驱动程序的开发

PLXMon是PLX公司专为其产品开发的测试软件。在用户的板卡插入PCI槽,并安装了PLXMon提供的驱动程序后,启动该软件就可以观察和修改芯片内部寄存器的值,并可以对存储器空间进行测试。

Windows下的驱动程序包括硬件物理设备的驱动程序和文件系统等非物理设备的虚拟设备驱动程序,我们所编写的是硬件物理设备的驱动程序。Windows类操作系统(Windows 95、Windows 98、WindowsNT、Windows 2000)为了保证其安全性、稳定性和可移植性,对应用程序访问硬件资源加以限制,用户需要对系统硬件及操作系统软件有详细的了解才可开发出高效的驱动程序,因此开发周期较长。利用第三方提供的开发软件,可以大大缩短开发时间,但效率不一定高,尤其对实时性要求严格的程序显得有些无力。

①Device Developer Kit(DDK)。该软件中包括了有关设备驱动开发的文档、编译需要的头文件和库文件、调试工具和程序范例;但是由于DDK主要是使用汇编语言进行描述,开发起来比较困难。

②VtoolsD。该软件包是基于C/C++的,支持BorlandC++和VisualC++,使用和维护比较方便。

③WinDriver。允许用户使用Visual C++、Borland或者其它Win32编程工具软件在用户模式(UserMode)上编写设备驱动程序。

④PLXMon。PLX公司专为其芯片提供的驱动程序开发包和测试软件,同样可以在用户模式上编写。支持Visual C++环境。

图4 突发读时序

在开发程序时,我们发现PLXMon和WinDriver不兼容,而且除非有正式版本的WinDriver;否则试用期过后,利用它开发的驱动程序将无法使用。所以建立使用PLXMon,只需包括相应的头文件,用户便可以方便地调用其提供的API函数,对板卡上的资源进行访问。以下的程序片段是在调试电路板时编写的基本查询中断是否有效来读取缓存的。所调用的函数均为PLXMon提供的API函数。其中:PlxPciBaseAddressesGet()是得到板卡上存储空间的物理地址,而*(Data+i)=*(U32*)(va.Va3)是将该空间的值装入计算机内存。

图5是驱动程序流程图。

程序段如下:

Example:

rc_w=PlxPciBaseAddressesGet(hDevice,%26;amp;va);

while(TRUE){

Int_Flag=*(U32*)(va.Va0+0x4c);

if(Int_Flag[0]%26;amp;4) {

for(i=0;i

for(i=0;i

嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练 TC52N4848ECTRT

TC52N4848ECTRT

京公网安备 11010802033920号

京公网安备 11010802033920号