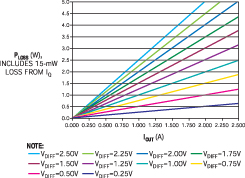

图1,线性稳压器压差VIN-VOUT(VDIFF)范围内,功率损失与IOUT关系。 功率损耗有两个后果:发热和低效率。使用线性稳压器的关键在于是否可以发散和耐受产生的热量,以及避免由此所致电池寿命的缩减。另一个关键问题是,是否能通过提高 LDO 稳压器的性能来维持它的候选资格。图1 显示了在某个VIN-VOUT 差(VDIFF)范围内,功率损耗与IOUT的关系。图 2 显示了几种常见封装的功率耗散能力。如图 2 所示,业界标准封装技术可以在不加散热片情况下提供超过 2W 的功耗。可将此数值与上面计算的 PLOSS 相比较。图 3 按图 2 所示顺序和相对大小列出了各种封装形式。

图1,线性稳压器压差VIN-VOUT(VDIFF)范围内,功率损失与IOUT关系。 功率损耗有两个后果:发热和低效率。使用线性稳压器的关键在于是否可以发散和耐受产生的热量,以及避免由此所致电池寿命的缩减。另一个关键问题是,是否能通过提高 LDO 稳压器的性能来维持它的候选资格。图1 显示了在某个VIN-VOUT 差(VDIFF)范围内,功率损耗与IOUT的关系。图 2 显示了几种常见封装的功率耗散能力。如图 2 所示,业界标准封装技术可以在不加散热片情况下提供超过 2W 的功耗。可将此数值与上面计算的 PLOSS 相比较。图 3 按图 2 所示顺序和相对大小列出了各种封装形式。  图2,在无散热片情况下,工业标准封装技术可以提供高于 2.0W 的功率耗散。

图2,在无散热片情况下,工业标准封装技术可以提供高于 2.0W 的功率耗散。  图3,按图2 顺序列出的封装以及相对尺寸。 已知负载电流和压差VIN-VOUT确定功率损耗,那么如何提高 LDO 稳压器的性能,使之适应标准封装的限制?尽管负载决定了输出电流和电压,但仍可以减小输入电压和 VDIFF。如果能降低这个电压差,就可以减小功耗和封装的约束,也就可以有更多可供选择的 LDO 稳压器方案。

图3,按图2 顺序列出的封装以及相对尺寸。 已知负载电流和压差VIN-VOUT确定功率损耗,那么如何提高 LDO 稳压器的性能,使之适应标准封装的限制?尽管负载决定了输出电流和电压,但仍可以减小输入电压和 VDIFF。如果能降低这个电压差,就可以减小功耗和封装的约束,也就可以有更多可供选择的 LDO 稳压器方案。  图4,FET 正在代替双极晶极管用于传输晶体管,因为 FET 的低导通电阻可以提供比双极晶体管固定饱和电压更低的压降。 新型 LDO 稳压器满足了这一要求,它具有比以往产品更低的电压降(VDIFF),以及降低最小输入电压和输出电压等级的方法。需要用场效应管(FET)代替双极晶体管来担当传输晶体管角色,因为 FET 的导通电阻电压降低于双极晶体管的固定饱和电压(图 4)。但很遗憾,大多数的 LDO 稳压器仍然要求最低输入电压要高于控制电路的工作电压。市场上也出现了一些改进后的 LDO 稳压器:它们有一个 VIN 和一个 VBIAS 输入,即将主电流通路与 IC 的偏置通路分隔开。换句话说,该器件的控制电路运行在较高的标准电压下(5V),有极小的电流(3mA),而通向输出端的大电流通路则来自一个独立的低电压输入(VIN)。这种设置降低了压差VIN-VOUT以及功率损耗。美国国家半导体的 LP3883 就是使用 VBIAS 端的一个电路实例,它在 3A 输出电流时压降为 210 mV。可以从一个 1.5V 电源(另一个核心电压)为 1.2V 负载(3.6W)提供 3A 电流,而功率损失仅为 900 mW。再加上控制电路消耗的 3mA 电流(控制电路电压为 5V),总的功率损耗只有 915 mW,因此可以采用很多封装形式。使用这些新型 LDO 稳压器,最佳策略就成了找到并利用电路板上的最低电压。标准封装的线性稳压器一般都比开关稳压器更便宜、更小,使用也更方便。 可以用以下公式确定应用的功耗对散热方式的要求:θJA=(TJ-TA)/PLOSS,其中θJA 为封装的热阻;TJ为 IC 的最大结温(一般为 125%26;#176;C),TA 为紧贴 IC的环境温度(系统的内部环境)。在本例中,TA为 30℃(大致的室内温度),TJ 为 125℃。计算出方案所需θJA后,将其与LDO 数据表中的封装进行比较,选定一种封装形式。数据表中封装的θJA必须等于或小于计算出的θJA值,否则结温可能会超出设定的最大值。 现在,我们已经计算了某个线性稳压方案的功率损失,并且确定了用于散热的封装形式。下面要考虑一下功耗和效率对电池寿命的影响。电池寿命一般用毫安小时(mAh)来表示。可以粗略地认为一节 100 mAh 的电池可以提供 10 个小时的 10 mA 电流,或提供一个小时的 100 mA 电流。(当然许多因素可以影响或降低这一数值。) 如果 IC 核心需要 100 mA 电流,则无论输入电压或输出电压如何,线性稳压器都必须通过它的传输晶体管供给 100 mA电流。但是,开关稳压器可以通过控制传输晶体管的导通时间(占空比)来减少对输入端平均输入电流的需求。在大多数情况下,开关稳压器效率都高于 LDO,因为它的输入电流是可以减小的,所以对那些需要高效率并对热量敏感的应用来说,开关稳压器方案更具吸引力。 关于线性稳压器有一个最后要注意的问题:如果核心电压是 1.2V,应确定它是否能承受更高的电压。市面上大多数的线性稳压器都使用标准的带隙基准源,它的最低输出电压极限是大约 1.25V。如果核心可以承受稍高的电压,可以选择的器件范围就宽多了,通常成本会更低。 现在,已经清楚了线性稳压方案的参数,如效率、功耗、压降以及封装。第三步查看一下开关稳压器。前面提到过的新型 LDO 稳压器电压降已经大幅减小,某些情况下已接近了开关稳压器的效率,拓宽了它们的应用范围。然而,开关稳压器总体上效率仍然更高,也有许多种类可供选择。

图4,FET 正在代替双极晶极管用于传输晶体管,因为 FET 的低导通电阻可以提供比双极晶体管固定饱和电压更低的压降。 新型 LDO 稳压器满足了这一要求,它具有比以往产品更低的电压降(VDIFF),以及降低最小输入电压和输出电压等级的方法。需要用场效应管(FET)代替双极晶体管来担当传输晶体管角色,因为 FET 的导通电阻电压降低于双极晶体管的固定饱和电压(图 4)。但很遗憾,大多数的 LDO 稳压器仍然要求最低输入电压要高于控制电路的工作电压。市场上也出现了一些改进后的 LDO 稳压器:它们有一个 VIN 和一个 VBIAS 输入,即将主电流通路与 IC 的偏置通路分隔开。换句话说,该器件的控制电路运行在较高的标准电压下(5V),有极小的电流(3mA),而通向输出端的大电流通路则来自一个独立的低电压输入(VIN)。这种设置降低了压差VIN-VOUT以及功率损耗。美国国家半导体的 LP3883 就是使用 VBIAS 端的一个电路实例,它在 3A 输出电流时压降为 210 mV。可以从一个 1.5V 电源(另一个核心电压)为 1.2V 负载(3.6W)提供 3A 电流,而功率损失仅为 900 mW。再加上控制电路消耗的 3mA 电流(控制电路电压为 5V),总的功率损耗只有 915 mW,因此可以采用很多封装形式。使用这些新型 LDO 稳压器,最佳策略就成了找到并利用电路板上的最低电压。标准封装的线性稳压器一般都比开关稳压器更便宜、更小,使用也更方便。 可以用以下公式确定应用的功耗对散热方式的要求:θJA=(TJ-TA)/PLOSS,其中θJA 为封装的热阻;TJ为 IC 的最大结温(一般为 125%26;#176;C),TA 为紧贴 IC的环境温度(系统的内部环境)。在本例中,TA为 30℃(大致的室内温度),TJ 为 125℃。计算出方案所需θJA后,将其与LDO 数据表中的封装进行比较,选定一种封装形式。数据表中封装的θJA必须等于或小于计算出的θJA值,否则结温可能会超出设定的最大值。 现在,我们已经计算了某个线性稳压方案的功率损失,并且确定了用于散热的封装形式。下面要考虑一下功耗和效率对电池寿命的影响。电池寿命一般用毫安小时(mAh)来表示。可以粗略地认为一节 100 mAh 的电池可以提供 10 个小时的 10 mA 电流,或提供一个小时的 100 mA 电流。(当然许多因素可以影响或降低这一数值。) 如果 IC 核心需要 100 mA 电流,则无论输入电压或输出电压如何,线性稳压器都必须通过它的传输晶体管供给 100 mA电流。但是,开关稳压器可以通过控制传输晶体管的导通时间(占空比)来减少对输入端平均输入电流的需求。在大多数情况下,开关稳压器效率都高于 LDO,因为它的输入电流是可以减小的,所以对那些需要高效率并对热量敏感的应用来说,开关稳压器方案更具吸引力。 关于线性稳压器有一个最后要注意的问题:如果核心电压是 1.2V,应确定它是否能承受更高的电压。市面上大多数的线性稳压器都使用标准的带隙基准源,它的最低输出电压极限是大约 1.25V。如果核心可以承受稍高的电压,可以选择的器件范围就宽多了,通常成本会更低。 现在,已经清楚了线性稳压方案的参数,如效率、功耗、压降以及封装。第三步查看一下开关稳压器。前面提到过的新型 LDO 稳压器电压降已经大幅减小,某些情况下已接近了开关稳压器的效率,拓宽了它们的应用范围。然而,开关稳压器总体上效率仍然更高,也有许多种类可供选择。  图5,计算出的效率曲线,1.2V 输出电压,50 mA 至 5A 电流范围,分别对应于一个同步开关稳压器、一个异步开关稳压器和一个线性稳压器时。 先来比较一下开关稳压器的与线性稳压器的效率。图 5 显示了计算出的效率曲线,它们分别是一个同步开关稳压器、一个异步开关稳压器和一个线性稳压器,条件均为 1.2V 输出电压,输出电流范围为 50 mA 至 5A。当输入电压从 3.3V 降至 2.5V 和 1.5V 时,异步开关稳压器和线性稳压器的效率均有较大提高。对线性稳压器,效率大致为 VOUT/VIN,所以当输入电压降为 1.5V 时,效率大约提高 35% 至 80%,接近开关稳压器的效率。异步开关稳压器的效率增加约 10%,因为当输入电压下降时,占空比增加,传输晶体管导通的时间多于二极管,这就需要更高的固定电压降(本例为 0.5V)。应记住这些效率只是理论值。在实际应用中,由于开关稳压器有传输晶体管和电感的压降,从 1.5V 可能得不到 1.2V 电压,此时 LDO 稳压器就更具吸引力了。 现在,注意一下低输出电压条件下开关稳压器的效率,以及两种主要开关稳压器(同步和异步)之间的比较评定。开关稳压器效率较高是因为它们降低了对电源电流的需求。对线性稳压器,传输晶体管总是导通的,多余的能量(VDIFF%26;#215;IOUT)都以热能形式散发出去。但是,开关稳压器可以把这个多余的能量储存在输出端的电感和电容中。负载可以从这里汲取能量,直至下一个开关周期刷新它们。由于开关稳压器是储存能量而不是浪费掉它们,因此降低了平均输入电流,提高了效率。

图5,计算出的效率曲线,1.2V 输出电压,50 mA 至 5A 电流范围,分别对应于一个同步开关稳压器、一个异步开关稳压器和一个线性稳压器时。 先来比较一下开关稳压器的与线性稳压器的效率。图 5 显示了计算出的效率曲线,它们分别是一个同步开关稳压器、一个异步开关稳压器和一个线性稳压器,条件均为 1.2V 输出电压,输出电流范围为 50 mA 至 5A。当输入电压从 3.3V 降至 2.5V 和 1.5V 时,异步开关稳压器和线性稳压器的效率均有较大提高。对线性稳压器,效率大致为 VOUT/VIN,所以当输入电压降为 1.5V 时,效率大约提高 35% 至 80%,接近开关稳压器的效率。异步开关稳压器的效率增加约 10%,因为当输入电压下降时,占空比增加,传输晶体管导通的时间多于二极管,这就需要更高的固定电压降(本例为 0.5V)。应记住这些效率只是理论值。在实际应用中,由于开关稳压器有传输晶体管和电感的压降,从 1.5V 可能得不到 1.2V 电压,此时 LDO 稳压器就更具吸引力了。 现在,注意一下低输出电压条件下开关稳压器的效率,以及两种主要开关稳压器(同步和异步)之间的比较评定。开关稳压器效率较高是因为它们降低了对电源电流的需求。对线性稳压器,传输晶体管总是导通的,多余的能量(VDIFF%26;#215;IOUT)都以热能形式散发出去。但是,开关稳压器可以把这个多余的能量储存在输出端的电感和电容中。负载可以从这里汲取能量,直至下一个开关周期刷新它们。由于开关稳压器是储存能量而不是浪费掉它们,因此降低了平均输入电流,提高了效率。  图6,异步稳压器使用一个三极管和一个二极管完成能量传送周期。同步稳压器则使用两个三极管。 异步稳压器使用一个三极管和一个二极管来完成能量传输过程(图 6)。在周期的第一部分,三极管将能量从源头送给负载和 LC 滤波器。当三极管截止时,正向偏置的二极管使 LC 中储存的能量流向负载,完成周期的剩余部分。由于二极管导通需要较高的正偏电压,所以最好是尽量使传输晶体管导通时间加长,以提高效率。但不幸的是,低输出电压经常会产生短的占空周期。 同步稳压器用另一个三极管替代了异步稳压器中的二极管。这支三极管的电压降低于二极管,于是效率高于异步开关稳压器。但轻载时则是一个例外,因为此时低导通电阻对系统效率提升作用不大,但仍要开关同步 FET 管。图 5 显示了这一效应。当 IOUT 接近 0A 时,同步 FET 的开关损耗明显降低了效率。 一般而言,在需要低占空因数、大输出电流或低输出电压的情况下(如为处理器核心供电的情况),同步稳压器的效率仍然高于异步稳压器。 许多开关稳压器有在轻载时提高同步稳压效率的功能。有些可以跳过脉冲或降低开关频率,使开关动作不那么频繁。另一种方法是关掉同步 FET 驱动,使用一个异步二极管与同步 FET 并联组成通路。这种方法在轻载工作时取异步运行效率,而在正常工作状态用同步运行效率。当然,每增加一个特性都会增加复杂性、成本或电路体积。因此,必须将这些可选方案与需求和约束进行比较来作出决定。 哪个是设计中最重要的因素?效率、成本还是体积?糟糕的是,对开关稳压器来说,这三大因素的计算要比线性稳压器复杂得多。比较好的着手解决的方法是采用一般的效率曲线图(如图 5 所示)来确定哪种方案最适合对效率的要求。搞清楚成本和体积的限制是很关键的。高的开关频率使得电路可以采用更小的电感和电容,从而能够降低整体体积和方案成本。但开关频率的升高可能会降低设计的总体效率。 由于可选方案众多,因此应该从多个线性和开关稳压电源供应商那里获得帮助。有了需求清单,就可以对一系列可行方案进行快速鉴别,还可以对没有公开发表的新器件进行研究。一旦可选范围缩小后,就可以计算各方案的效率、成本和体积,并且再次利用供应商的支持与工具,比较各种可能方案的特性。还应记住,尽管新型开关稳压器可能包括亚带隙基准源,但大多数仍然继续沿用标准的带隙基准源,因此多数开关稳压器的最小输出电压仍被限制为 1.25V。 这里要特别提一下开关电容变换器。开关电容变换器可以提供比线性稳压器更高的效率,无需使用电感。但是,它们的电流限制约为 300 mA。开关电容设计在电池供电的应用中很有吸引力,此时电感尺寸和 EMI 问题都是重要的限制因素。但是,采用新型开关技术与电感技术的开关稳压器已经在许多应用中获得了相当的关注,而这些应用以前都是用开关电容变换器。 为低电压微处理器核心供电有多种可选方案。在三个步骤的选择过程中,第一步是建立一个需求与约束的完整清单;第二步是考虑新型 LDO 稳压器和标准的封装技术,分析是否可能采用线性稳压器方案;第三步是仔细审查开关稳压器,以及对同步、异步和线性方案的效率作出比较评定。有了需求表和收集到的信息,再寻求供应商的帮助来缩小可选范围,并计算各个方案的效率、成本和体积。

图6,异步稳压器使用一个三极管和一个二极管完成能量传送周期。同步稳压器则使用两个三极管。 异步稳压器使用一个三极管和一个二极管来完成能量传输过程(图 6)。在周期的第一部分,三极管将能量从源头送给负载和 LC 滤波器。当三极管截止时,正向偏置的二极管使 LC 中储存的能量流向负载,完成周期的剩余部分。由于二极管导通需要较高的正偏电压,所以最好是尽量使传输晶体管导通时间加长,以提高效率。但不幸的是,低输出电压经常会产生短的占空周期。 同步稳压器用另一个三极管替代了异步稳压器中的二极管。这支三极管的电压降低于二极管,于是效率高于异步开关稳压器。但轻载时则是一个例外,因为此时低导通电阻对系统效率提升作用不大,但仍要开关同步 FET 管。图 5 显示了这一效应。当 IOUT 接近 0A 时,同步 FET 的开关损耗明显降低了效率。 一般而言,在需要低占空因数、大输出电流或低输出电压的情况下(如为处理器核心供电的情况),同步稳压器的效率仍然高于异步稳压器。 许多开关稳压器有在轻载时提高同步稳压效率的功能。有些可以跳过脉冲或降低开关频率,使开关动作不那么频繁。另一种方法是关掉同步 FET 驱动,使用一个异步二极管与同步 FET 并联组成通路。这种方法在轻载工作时取异步运行效率,而在正常工作状态用同步运行效率。当然,每增加一个特性都会增加复杂性、成本或电路体积。因此,必须将这些可选方案与需求和约束进行比较来作出决定。 哪个是设计中最重要的因素?效率、成本还是体积?糟糕的是,对开关稳压器来说,这三大因素的计算要比线性稳压器复杂得多。比较好的着手解决的方法是采用一般的效率曲线图(如图 5 所示)来确定哪种方案最适合对效率的要求。搞清楚成本和体积的限制是很关键的。高的开关频率使得电路可以采用更小的电感和电容,从而能够降低整体体积和方案成本。但开关频率的升高可能会降低设计的总体效率。 由于可选方案众多,因此应该从多个线性和开关稳压电源供应商那里获得帮助。有了需求清单,就可以对一系列可行方案进行快速鉴别,还可以对没有公开发表的新器件进行研究。一旦可选范围缩小后,就可以计算各方案的效率、成本和体积,并且再次利用供应商的支持与工具,比较各种可能方案的特性。还应记住,尽管新型开关稳压器可能包括亚带隙基准源,但大多数仍然继续沿用标准的带隙基准源,因此多数开关稳压器的最小输出电压仍被限制为 1.25V。 这里要特别提一下开关电容变换器。开关电容变换器可以提供比线性稳压器更高的效率,无需使用电感。但是,它们的电流限制约为 300 mA。开关电容设计在电池供电的应用中很有吸引力,此时电感尺寸和 EMI 问题都是重要的限制因素。但是,采用新型开关技术与电感技术的开关稳压器已经在许多应用中获得了相当的关注,而这些应用以前都是用开关电容变换器。 为低电压微处理器核心供电有多种可选方案。在三个步骤的选择过程中,第一步是建立一个需求与约束的完整清单;第二步是考虑新型 LDO 稳压器和标准的封装技术,分析是否可能采用线性稳压器方案;第三步是仔细审查开关稳压器,以及对同步、异步和线性方案的效率作出比较评定。有了需求表和收集到的信息,再寻求供应商的帮助来缩小可选范围,并计算各个方案的效率、成本和体积。

上一篇:具有低功耗待机和PFC功能的开关电源控制器

下一篇:抽油机节能电控装置综述(1)

Vishay线上图书馆

- 选型-汽车级表面贴装和通孔超快整流器

- 你知道吗?DC-LINK电容在高湿条件下具有高度稳定性

- microBUCK和microBRICK直流/直流稳压器解决方案

- SOP-4小型封装光伏MOSFET驱动器VOMDA1271

- 使用薄膜、大功率、背接触式电阻的优势

- SQJQ140E车规级N沟道40V MOSFET

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- Vicor高性能电源模块助力低空航空电子设备和 EVTOL的发展

- Bourns 推出两款厚膜电阻系列,具备高功率耗散能力, 采用紧凑型 TO-220 和 DPAK 封装设计

- Bourns 全新高脉冲制动电阻系列问世,展现卓越能量消散能力

- Nexperia推出新款120 V/4 A半桥栅极驱动器,进一步提高工业和汽车应用的鲁棒性和效率

- 英飞凌推出高效率、高功率密度的新一代氮化镓功率分立器件

- Vishay 新款150 V MOSFET具备业界领先的功率损耗性能

- 强茂SGT MOSFET第一代系列:创新槽沟技术 车规级60 V N通道 突破车用电子的高效表现

- 面向车载应用的 DC/DC 电源

嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练 LM101H/883

LM101H/883

京公网安备 11010802033920号

京公网安备 11010802033920号