摘 要:针对目前电磁跟踪系统跟踪速度慢,计算参数精度低的现况,文中介绍了一种采用DSP系统来完 成对感应天线接收到的模拟信号采集处理的方案。该方案实现了单通道128 kHz的采样率和12位的数据精度,解 决了系统中信号的时序配合问题,很准确地得到了系统的接收矩阵,提高了系统的定位精度,并将数据刷新率提高 到125 Hz。

六自由度电磁跟踪系统根据电磁感应的原理来计算出目标的六个自由度参数,从而唯一确定目标的位 置和姿态。怎样由接收到的模拟信号计算得到目标的位置和姿态参数是影响整个系统性能的关键所在。在 一些早期的产品中对感应天线接收信号的处理主要采用模拟电路和单片机来完成,由于模拟电路精度低,受 器件性能影响大,单片机的指令执行速度慢,使整个系统无法准确实时地确定目标的位置。本文提出的DSP 数据采集系统利用了DSP快速的指令执行周期和强大的数字信号处理功能和CPLD灵活的时序和逻辑控 制功能,快速准确地完成了对每一路接收信号的采集和计算,得到了准确的数字接收矩阵,为进一步计算目 标的六个自由度参数打下良好基础。本文主要介绍了DSP数据采集系统的硬件设计方案和软件设计流程。

1 电磁跟踪系统的工作原理

六自由度电磁跟踪系统的发射和接收天线均为三维正交环形天线。发射电路向发射天线的xyz轴按时

式中x为发射矩阵,为一单位对角阵,G为系统总增益,H、M为包含了接收天线相对于发射天线的位置和接收天线姿态角度的坐标变换矩阵。因此接收矩阵是影响目标参数精度的关键。

2 DSP系统的硬件设计

由六自由度电磁跟踪系统的原理,为了得到系统接收矩阵Y,DSP系统要同时采集四路模拟信号:T,Rx ,R y,Rz ,而每一路的信号都是时分复用的。因此要求系统能准确区分每一路每个时间段的数据,然后计算出每一段数据的幅度,将其发送到计算机。DSP数据采集系统的硬件结构如图3所示。

四路模拟信号由两片A/D同时进行采样,采样得到的数字比特流通过FIFO缓存后有序地传送到DSP芯片,DSP快速地对采集来的数字信号进行计算,最后将计算结果通过异步串行接口传送到计算机。各器件之间的时序配合由CPLD来控制。

2.1 DSP外围电路及通信接口的设计

本系统所采用的TMS320VC5416是TI公司推出的一款低功耗高性能16位定点DSP,具有160 MIPS 的指令执行速度,片内集成有128 K×16 bit的RAM 和16 K×16 bit的ROM。它的外围电路主要包括时 钟,电源,复位以及外程序存储器。本系统采用外部时钟,电源和复位采用TI公司的专用芯片TPS73HD301。

由于TM320VC5416无片内FLASH,因此系统采用M29w8O0DT作为程序存储器,系统上电后,DSP内部 引导程序把M29W800DT 中的工作程序加载到片内SRAM ,提高程序执行效率。 系统通信电路包括并行通信和串行通信两部分。

由于TMS320VC5416片内没有UART端口,要实现 和计算机的串行数据通信,系统采用了ST16C550,通过IO访问ST16C550来实现与主机的串行通信。 系统中FI ASH,F1FO,ST16C550通过CPI D分别映射到DSP的数据空间和IO空间,DSP与他们的 通信主要通过16位的外部并行数据总线。因此用到的DSP的外部接口主要有16位地址总线,16位数据总线和一组用于访问片外存储器与I/0端口的控制信号。

2.2 A/D与DSP的接口设计

AD7862是AD公司推出的高速、低功耗、双极性12位的A/D转换芯片,其中包含了两个独立的快速 ADC模块(允许同时采样和转换两路信号),4路模拟输入信号,2.5 V的内部电压基准以及12位的高速并 行接口,最高采样率达250 kHz。

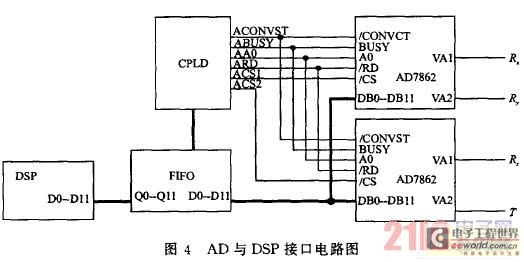

系统要求对4路频率为16 kHz 的模拟信号进行同时采样,采样时不 能有相位差。AD7862虽然有4路模 拟输入通道,然而内部只有两个 ADC,即每片A/D只能同时采样两 路模拟信号,因此系统中采用了两 片AD7862来完成对模拟信号的采 样[3]。A/D与DSP接口如图4所 示。

从这部分电路可以看到,DSP 不直接与数/模转换模块接口,而是利用CPLD屏蔽A/D转换的初始化以及读写操作过程,并将两个A/D 转换单元通过FIFO缓存后映射到DSP的10空间。这样DSP可以在未知ADC控制方式的情况下,通过定 时访问外设的方式来获得4个通道的模数转换后的数据。这种方法大大提高了DSP的工作效率,而且当系 统要求增加ADC的数目时,不需要改变电路,极大的提高了系统的可扩展性。

电路中两片A/D除了片选控制信号以外其 他的数据总线以及控制总线全部是分别连在一起 的。将片选控制与其他控制分开的原因在于:A/ D芯片的初始化以及转换过程需要同时完成,但 是数据的输出需要分别完成,否则会出现总线冲 突。ADC时序控制框图如图5所示。

AD7862最高采样率可到250 kHz,然而根据 正弦信号抽样的基本原则,抽样率应为原信号的 整数倍,又考虑到对抽样后的数据做DFT运算时 希望数据点数N 最好为2的整次幂,因此设计系 统实际采样率为128 kHz。

3 系统的软件设计

TMS32O5416的软件设计主要包括初始化程 序,主程序,外部中断程序,定时器中断程序和串 行口中断程序。初始化程序完成DSP及外围芯片 的初始化,主程序将采集到的数据滤波后进行 FFT运算提取幅度值。串行口中断程序完成接收 矩阵的发送。系统软件的工作流程如图6所示,当模拟信号进来并开始采样时,即发射部分的时序控制逻辑为OO时,产生INT1,DSP开启定时器中断并设置定 时器的值为2 ms。定时器中断后,DSP从FIFO 中读取前2 ms时间段内采集到的所有数据,

上一篇:基于物联网的公共安全监测系统

下一篇:基于DSP的模拟电路诊断系统的实验可行性验证

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 LM6161W/883

LM6161W/883

京公网安备 11010802033920号

京公网安备 11010802033920号