摘要:提出了一款适合在低电压、大容量SRAM中应用的高速低功耗电流型灵敏放大器。该电路在交叉耦合反相器之间添加了一对隔离管,有效消除了大量位线寄生电容所带来的负面影响,从而极大提高了灵敏放大器的速度。同时,通过对时序控制电路的优化,有效降低了放大器的功耗。采用SMIC 0.13 μm数字工艺在HSpice下进行仿真,结果表明:在室温,1.2 V工作电压下,灵敏放大器的放大延迟仅为0.344ns,功耗为102 μW。相比文献中提出的电流型灵敏放大器,速度分别提高了9.47%和31.2%,功耗则降低了64.8%与63%。

关键词:电流型灵敏放大器;交叉耦合反相器;隔离管;时序控制电路

0 引言

静态随机访问存储器(SRAM)最初作为CPU与内存之间的缓存。近年来已广泛应用于高性能通信网络、便携式设备以及SOC系统中,呈现出向高速器件与低功耗性能方向发展的趋势。因此,设计高速低功耗的SRAM已成为现在SRAM技术的主流方向。灵敏放大器是SRAM的重要组成部分,它将位线上的微小信号差迅速放大到全摆幅模式,从而有效减小数据的读出延迟,同时由于不需要对位线电容完全充放电,因此也在某种程度上降低了功耗。所以,对高性能灵敏放大器进行设计是得到高速低功耗SRAM的一个有效途径。根据对位线上要进行处理的信号类型的不同,灵敏放大器可分为电压型灵敏放大器和电流型灵敏放大器。由于电流型灵敏放大器直接检测位线上的电流变化,不需要转化为电压信号,因此在速度上更具有优势,可满足高速的要求。针对不同的应用层面,目前出现了多种电流型灵敏放大器的设计结构:有源负载PBT结构,其优点是输出不受电源电压及偏置电压的影响;基于电流镜结构的电流灵敏放大器,可以应用在低压非易失存储器中;为了消除位线噪声电流,而提出的采用位线漏电流补偿技术的电流型灵敏放大器;单端伪差分电流灵敏放大器,旨在改善SRAM读出操作时的稳定性及延迟;为降低功耗而提出的由两级放大(全局和局部放大)构成的全电流模式灵敏放大器以及APD灵敏放大器。

本文在分析目前广泛应用的电流型灵敏放大器的基础上,提出了一种改进型的结构,以提高灵敏放大器的速度为主要目标,兼顾考虑功耗,以实现速度和功耗之间合理的折衷。

1 传统的电流型灵敏放大器

传统的电流型灵敏放大器是由4个晶体管构成的交叉耦合反相器单元,位线信号从漏极输入,经正反馈放大,再由漏极输出,电路如图1所示。灵敏放大器有2个工作阶段:预充电和信号放大阶段。预充电时,2个上拉P管将位线电压拉至VDD,同时平衡管(M3)开启,使位线电压近似相等;当灵敏放大器使能信号有效时,便进入放大阶段,检测到位线上电流的变化差值并放大输出。

![]()

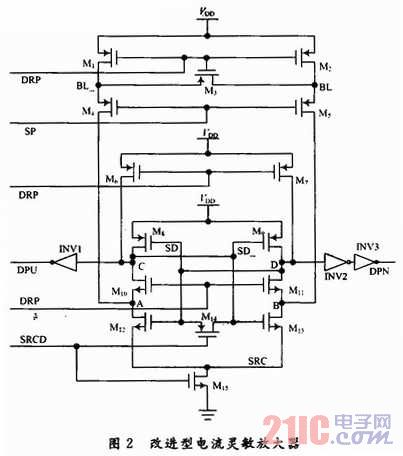

2 改进的电流型灵敏放大器

上述分析的灵敏放大器的输入和输出共用同一个端口,容易相互产生串扰,造成输出结果错误,并且当该端口作为输出端时,由于位线寄生电容较大,会浪费部分时间在对该电容进行充放电上,由灵敏放大器的延迟公式即式(1)可以看出,当位线电容Cbit增大时,延迟Td也将变大,不利于高速灵敏放大器的设计。所以可在原有电路结构的基础上添加一对隔离管,并对外围电路做一改进,具体结构如图2所示。

当灵敏放大器进行放大时,隔离管(M10和M11)开启,信号输入和输出端被隔断,输出时可以不必考虑端口的寄生电容,因此有效提高了灵敏放大器的速度;并且当灵敏放大器处于预充状态时,隔离管关闭,这样反相器的P管和N管就被隔离开,之间没有通路,也就没有漏电流,从而降低了电路的功耗。

另外电流型灵敏放大器的输入为电流信号,故不需要在位线上建立较大的电压差,即可快速放大差值信号。因此,从动态功耗即式(2)及式(1)可以看出,小的电压摆幅△Vs可使电流型灵敏放大器的功耗与延迟同时减小。

![]()

此外,对灵敏放大器的时序控制也非常重要。若时序设置不当,有可能会造成灵敏放大器的读出错误,相反若设计得当,不仅可以减小数据的读出延迟,还可以有效地降低灵敏放大器的功耗。因此,需要对这部分做一特别考虑。

2.1 灵敏放大器的工作过程

在预充电阶段,DRP为“0”,此时M1,M2,M3,M6,M7管导通,M10,M11管关断,位线BL和BL被上拉至电源电压VDD,平衡管M3使两边的位线电压处于近似相等的状态。同时交叉耦合反相器的输出端C,D也被上拉至VDD,使得在预充电时DPU为“0”,DPN为“1”。M4和M5管为电流传输管,由信号SP控制,在预充电时,SP为低电平,M4、M5导通,电流通过这2个管传输到A、B端,等待放大信号的到来。M10,M11关闭,将放大通路阻断,此时灵敏放大器使能信号SRCD为低,M14导通,使C,D两端电压相互平衡,M15则关闭,从而切断了电源到地之间的通路,使得灵敏放大器在预充电时没有漏电流,进而降低了电路的功耗。这一阶段是准备阶段,即灵敏放大器为下一个放大操作做准备的过程。在放大模式下,首先DRP跳变为“1”,结束预充电过程,同时M10、M11管导通。随后SRCD变为高电平,M16管导通,M14关闭,放大通路由此形成。之后SP变为高电平,将电流传输管关闭,此时A,B端之间的微小电流信号差通过正反馈被迅速放大成全摆幅的逻辑信号。当被放大的输出信号稳定后,灵敏放大器将重新进入到预充电状态。在整个灵敏放大器电路中,M8、M9、M12和M13管构成的交叉耦合反相器是核心,其管子尺寸直接影响放大器的速度。因此,还需适当调整这4个管的尺寸从而最大化的提高灵敏放大器的速度。表1为核心管子的尺寸。

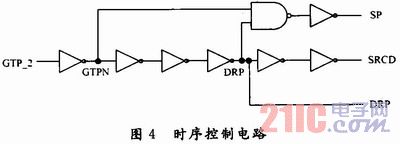

2.2 时序控制电路

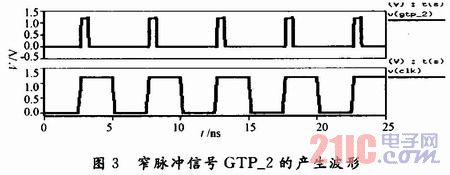

该灵敏放大器的时序控制信号包括:预充电控制信号DRP、电流传输信号SP、灵敏放大器使能信号SRCD。在外部看,整个灵敏放大器的时序基于一个GTP_2信号,该信号是由外部时钟CLK产生的同步脉冲,即通过反馈把周期的时钟信号变成一个周期的窄脉冲信号GTP_2,从图3的波形中可以明显看出。用该脉冲代替CLK控制SRAM的读写操作,可以尽可能地减少晶体管的开启时间,从而有效降低了电路的功耗。

由于预充是为放大做准备的阶段,因此预充电控制信号DRP要先于其它所有信号,以便在其它信号到来之前先对电路进行充电。在DRP跳变为高电平之前,电流传输信号SP以及使能SRCD都为低电平,SP为低保证位线高电平已传输至A、B端,而SRCD为低则将平衡管M14开启。当电路进入到放大状态时,DRP变为高电平,为了保证位线电压被充分传输至A、B两端,SP应在DRP跳变后再变为高电平。而在进行信号放大之前,应使SRCD为高,关闭平衡管同时开启尾电流源,并且关断M14一定是在打开隔离管M10和M11之后进行的,因为若立即关断平衡管,放大器两边轻微的失配就会触发正反馈进行工作,从而导致读出结果的错误。因此,信号SRCD可由DRP经过反相器链延迟后形成,同时SRCD应先于SP变高,并且SP的高电平只需持续到下一次预充准备时,即DRP变为低电平时,所以SP可由DRP和GTP_2的反信号相与产生。图4即为控制该灵敏放大器工作的时序电路,由该电路产生的波形如图5所示。

3 仿真结果

本设计采用SMIC 0.13μm数字工艺在HSpice下进行仿真,在位线BL和BL_上各加1个1 pF的电容来模拟大容量SRAM电路中的位线电容,并添加一个六管的存储单元,输出端各加1个50 pF的负载电容,字线WP用窄脉冲控制,仿真时工作电压设为1.2 V,温度为室温。

图6为改进后的电流型灵敏放大器的实际仿真波形。从图中可以看出,在图4时序电路的控制下,灵敏放大器的实际工作过程完全符合上述分析。如图6(a),在预充电时由于位线被上拉至VDD,所以输出DPN为高电平,而DPU为低电平;放大时,由于存储单元存储的信息为“0”,所以BL一侧对寄生电容放电后电流略微减小进而与BL_侧形成电流差值,之后由正反馈迅速放大,在输出DPN端得到全摆幅的逻辑电平“0”,存储数据被正确读出。图6(b)为存储单元存储信息为“1”时的输出波形,分析同上,最后是在DPU端得到全摆幅的逻辑电平“1”。

改进型电流灵敏放大器的版图如图7所示,面积为82.39μm2。版图设计时特别考虑了器件的匹配性以及布局布线的合理性,尽可能减小寄生效应对电路性能的影响。对该灵敏放大器进行后仿真,结果显示其放大延迟为0.344 ns,平均功耗为102μW。由此可见,本文设计的改进型的电流灵敏放大器可以实现高速低功耗的要求。

在工艺条件及工作电压相近的前提下,将本文的灵敏放大器与文献中提到的几种灵敏放大器在速度和功耗上进行比较,见表2。结果表明,本文提出的改进型电流灵敏放大器无论在速度,还是在功耗上都较其它灵敏放大器更具有优势。速度为0.344 ns,与文献提出的电流型灵敏放大器相比提高了9.47%,比文献所示的放大器则提高了31.2%;功耗则较两者分别降低了64.8%和63%。

4 结语

本文提出了一款改进的电流型灵敏放大器,其优势在于读取速度快,功耗低,并且适合在低压下工作。与文献提出的电流灵敏放大器相比,速度分别提高了9.47%和31.2%,而功耗则降低了64.8%和63%。由于电流型灵敏放大器输入阻抗小,并且本文在原有的基础上加了一对隔离管,使得输出不受负载电容的影响,同时优化了四个核心管的尺寸,进而有效提高了灵敏放大器的速度;此外,对放大器的时序控制电路也做了细致合理的设置,在完成放大的基础上尽量减少管子的开启时间,从而减小静态电流,达到了降低功耗的目的。因此,该灵敏放大器完全满足高速低功耗的需求,更适合低电压,大容量SRAM的应用。

上一篇:基于CORDIC改进算法的DDS设计

下一篇:美国两所大学与英特尔试制成功人工心脏无线供电系统

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TLP7820(LF4,E

TLP7820(LF4,E

京公网安备 11010802033920号

京公网安备 11010802033920号