VHDL是美国国防部提出的一种经过标准化认证的硬件描述语言,使用VHDL语言进行硬件设计有如下特点:将一项工程设计(或称设计实体)分成外部(或称可视部分,即端口)和内部(或称不可视部分),即设计实体的内部功能和算法完成部分。

本文介绍应用美国ALTERA公司的MAX+PLUSⅡ平台,使用VHDL硬件描述语言实现的十六路彩灯控制系统。

十六路彩灯控制系统的实现

在电路中以1代表灯亮,以0代表灯灭,由0、1按不同的规律组合代表不同的灯光图案,同时使其选择不同的频率,从而实现多种图案多种频率的花样功能显示。在该电路中只需简单的修改程序就可以灵活地调整彩灯图案和变化方式。下面就以一个十六路彩灯控制系统的实现为例进行简单说明。

功能描述

此十六路彩灯控制系统设定有四种花样变化,这四种花样可以进行自动切换,且每种花样可以选择不同的频率,四种花样分别为:

(1)彩灯从右到左,然后从左到右逐次产闪烁。

(2)彩灯从右到左点亮,然后从左到右逐次依次熄灭,全亮全灭。

(3)彩灯两边同时亮2个逐次向中间移动再散开。

(4)彩灯两边同时亮4个,4亮4灭。

设计原理

用VHDL进行设计,首先应该理解,VHDL语言是一种全方位硬件描述语言,包括系统行为级,寄存器传输级和逻辑门级多个设计层次。应充分利用VHDL“自顶向下”的设计优点以及层次化的设计概念,层次概念对于设计复杂的数字系统是非常有用的,它使得我们可以从简单的单元入手,逐渐构成庞大而复杂的系统。

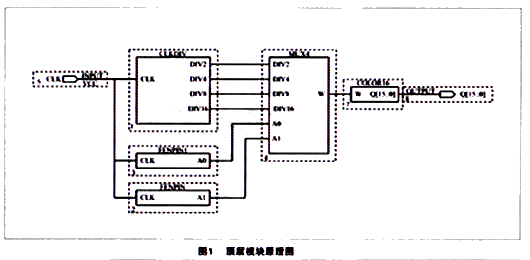

首先应进行系统模块的划分,规定每一模块的功能以及各个模块之问的接口。最终设计方案为:以一个十六路彩灯花样控制器、一个四频率输出分频器,一个四选一控制器和一个时间选择器总共四部分来完成设计。四选一控制器从分频器选择不同频率的时钟信号输送到彩灯花样控制器,从而达到控制彩灯闪烁速度的快慢,时间选择器控制每种速度维持的时间长短。

整个十六路彩灯控制系统设计的模块图如图1所示。

|

|---|

子模块及其功能

本次设计分为四个子模块,即十六路彩灯花样控制器、四频率输出分频器,四选一控制器和时问选择器,其子模块及其功能如下:

(1)四频率输出分频器:在本次设计中,我们只设计了四种花样,我们要求这四种花样以不同的频率显示,而只有一个输入的时钟信号,所以我们对所输入的时钟信号进行2分频、4分频、8分频、16分频,得到四种频率信号,CLKDIV模块就是来完成此功能。

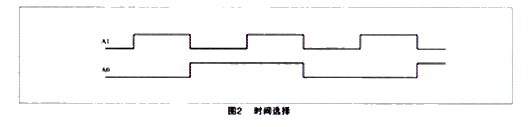

(2)时间选择器:时间选择器实际上是两个分频器,其中一个频率是另一个频率的两倍。本来这两个分频器可以在上述的四频率输出器中实现的,但为了方便地为四选一控制器提供不同的时间选择条件,就将这两个分频器独立开来。这两个输出的的时钟信号组合起来就可以为四选一控制器提供00、01、10、11四个时间选择条件,如图2所示。

(3)四选一控制器:四选一控制器功能是从分频器中选择不同频率的时钟信号送给彩灯控制器,实现彩灯闪烁的频率变化。

(4)彩灯控制器:彩灯控制电路是整个设计的核心,它负责整个设计的输出效果即各种彩灯图案的样式变化。该程序充分地说明了用VHDL设计电路的“弹”性,即可通过改变程序中输出变量Q的位数来改变彩灯的数目。其中,P1进程对灯闪的速度进行控制,有两种方式可改变灯闪的速度:一是改变外部时钟的赋值,二是改变信号U的位数。P2进程能进行彩灯的图案控制,改变s的位数即可改变要控制图案的数目,改变输出变量O的组合即可变幻彩灯图案。彩灯控制器的实现程序如下:

|

|---|

Librarv ieee;

|

|---|

|

|---|

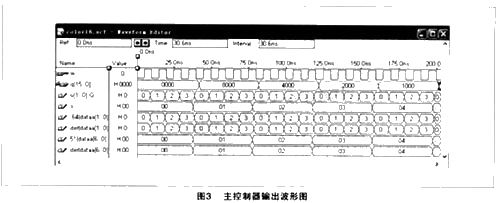

其仿真波形如图3所示,模块符号如图4所示。

|

|---|

|

仿真结果

最后,当各个模块均完成上述操作之后,即可利用MAXPLLUS2的原理图输入,调用各个元器件(底层文件),以原理图的形式形成最后的十六路彩灯显示系统(顶层文件),并且进行仿真。仿真通过,即可下载到指定的CPLD芯片里面,并进行实际连线,进行最后的硬件测试。当然,可以将各个模块所生成的元件符号存放在元件库中,以被其他人或其他的设计所重复调用,以简化后面的设计。

与其它硬件设计方法相比,用VHDL进行工程设计的优点是多方面的:VHDL具有很强的行为描述能力,支持大规模设计的分解和已有设计的再利用,可读性好,易于修改和发现错误,可以使用仿真器对VHDL源代码进行仿真,允许设计者不依赖于器件,容易发现设计中出现的问题,以便及时处理。能实现设计与工艺无关,可移植性好,上市时间快,成本低,ASI(:移植等优点。应用FPGA可以实现复杂电路的控制,本文只是应用其简单的控制设计的一个具体实现过程。

上一篇:PLC控制系统的电磁干扰来源和抗干扰设计

下一篇:基于C8051F040的CAN总线智能节点设计

推荐阅读最新更新时间:2024-03-30 21:23

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著)

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著) 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号