PCI总线是现今最为流行的控制总线之一,它广泛地应用在计算机中,目前嵌入式设备中的很多解决方案都包含了PCI总线。在多主设备的PCI系统应用中,必须为各个主设备提供仲裁授权信号。为了使PCI设备能够更方便地应用在嵌入式系统中,本文介绍一种基于飞思卡尔MPC5200B的低成本PCI总线仲裁器逻辑扩展的设计方法,此方法可以在已有的PCI仲裁器的基础上,实现扩展PCI总线上主设备的个数,从而满足多PCI设备的设计要求,提高系统的扩展性要求,在体积、功能、成本等诸多方面都有很好的应用前景。

MPC5200B

飞思卡尔公司的MPC5200B是基于PowerPC架构下的一款性能卓越的微处理器。它具有760MIPS、带浮点运算单元(FPU)、低功耗等特点。该处理器采用高性能的e300内核,集成了高性能存储控制器、中断控制器、 DMA控制器、PCI控制器、以太网控制器以及USB、CAN 2.0A/B、I2C等丰富的接口。其结构框图如图1所示。

图1 MPC5200B 框图

MPC5200B能够快速提供数据吞吐和处理。集成的 BestComm DMA控制器可降低主e300核心传送I/O密集数据的负荷。集成的双倍数据速率(DDR)内存控制器的有效内存总线速度达到266MHz,能够实现高速数据访问。 BestComm DMA 控制器和DDR内存支持的高速PCI 接口能够实现高速数据输入和输出。

MPC5200B内部集成了一个PCI总线仲裁器,但其仲裁只支持两个外部PCI主设备(包含MPC5200B的PCI模块)。为了增加PCI主设备,我们必须对PCI仲裁器进行扩展。

PCI总线仲裁

PCI总线是一种共享式的总线,可以连接多个主设备,但由于数据传输的独享性,每一时刻只能由一个主设备占用总线。因此,为了有效地利用PCI总线带宽,总线上必须设置一个仲裁器。

每个具有主设备功能的PCI设备必须提供两个与仲裁有关的信号:REQ#(请求总线信号)和GNT#(总线授权信号)。由需要发起PCI传输事务的设备发出 REQ#信号,由PCI总线仲裁器裁决后给出GNT#信号。接到GNT#信号的PCI设备将在下一次总线空闲后开始操作。

PCI总线仲裁的裁决过程可以在PCI传输期间完成,并不占用PCI总线的带宽,这被称为隐式仲裁:即需要发起PCI操作的设备可以随时发出请求REO#,PCI仲裁器立即批准该请求并给出GNT#。但实际的传输过程一定要等到当前传输完毕、线空闲后才可以开始。[page]

具体设计及仿真

以MPC5200B外扩两个主PCI设备为例,依据PCI仲裁原理及MPC5200B PCI控制器接口,逻辑扩展方式如图2所示。其中逻辑单元(Logic Unit)就是本文详细阐述的部分。

图2 MPC5200B PCI仲裁逻辑扩展示意图

MPC5200B含有一个片上PCI总线仲裁器,现在需要对外扩展其仲裁功能,以满足多主PCI设备的需求。

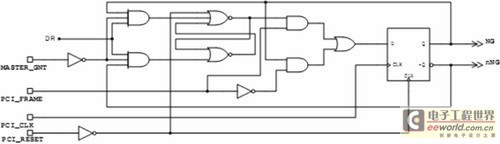

对于外扩PCI主设备而言,有两对REQ#和GNT#信号需要和MPC5200B片上PCI仲裁器进行通讯;对于MPC5200B而言,逻辑单元就是它一对一的主PCI设备,通讯信号为相关的PCI总线控制信号。逻辑单元电路如图3所示。

图3 MPC5200B PCI仲裁逻辑扩展电路

图3b MPC5200B PCI仲裁逻辑扩展电路(续)

PCI总线复位信号对逻辑电路复位后,如果仅有一个总线请求,则相对应的总线授权信号MASTER_GNT通过由此总线请求控制的MUX进行输出,实现总线“请求-授权”过程。

如果两PCI外设同时产生总线请求信号REQ0#和REQ1#,则DR(Dual Require)信号配合PCI_PRAME和PCI_CLK,锁住NG(Next Grant)信号的更新,直到当前帧传输完毕。

由图4可以看出,仿真环境模拟了一个设备申请和两个设备同时申请的情况,并分别给出了总线授权信号(GNT),验证了仲裁器扩展逻辑的正确性。

图4 MPC5200B PCI仲裁逻辑扩展电路仿真

结语

PCI总线协议抽象性很强,且时序逻辑复杂。本文采用简单的逻辑设计实现了对于PCI仲裁器扩展,已经在CPLD中实现,成功应用于MPC5200B的PCI仲裁器逻辑扩展。

参考文献:

1. MPC5200B User’s manual. Rev.1

2. PCI Local Bus Specification. Rev 2.2

上一篇:应用CY8C21534设计通用操作面板

下一篇:基于嵌入式Linux系统设备驱动程序的开发

推荐阅读最新更新时间:2024-03-16 12:58

设计资源 培训 开发板 精华推荐

- 微软领先科技巨头,成为英伟达Hopper芯片最大买家

- 芯启源(上海)将持续发力,“做深做精”EDA及IP产品

- 本田严厉警告日产:若与鸿海合作,那么本田与日产的合作将终止

- Microchip推出新款交钥匙电容式触摸控制器产品 MTCH2120

- Matter对AIoT的意义:连接AIoT设备开发人员指南

- 我国科学家建立生成式模型为医学AI训练提供技术支持

- Diodes 推出符合车用标准的电流分流监测器,通过高精度电压感测快速检测系统故障

- Power Integrations面向800V汽车应用推出新型宽爬电距离开关IC

- 打破台积电垄断!联电夺下高通先进封装订单

- Ampere 年度展望:2025年重塑IT格局的四大关键趋势

- 寻宝大冒险,搜索有好礼!

- 免费申请| Microchip WBZ451 Curiosity

- MPS有奖活动|梦想设计闪亮登场,便携式多功能电工台诞生啦!

- 学AM335X课程,赢超值BB-Black团购资格,更有DIY大奖赛预热中!

- 有奖活动|登陆泰克高精度电源测试知识星球,揭开噪声的迷雾,发现真实的信号!

- 深入东芝参考设计库:夯实您的设计库,让您的设计更出彩

- 直播已结束【使用 TI 低成本 MSPM0 MCU 快速开发 – 生态详解系列之二】(9:45开始入场)

- 了解PI高性能AC-DC产品,答题赢好礼

- 助力EEWorld 19成长计划,赢取精美好礼!

- 是德科技有奖问答活动之一,A4WP无线充电测试的示波器方案,答题闯关赢好礼!

机器人学 (蔡自兴)

机器人学 (蔡自兴) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号