随着硬件技术的大力发展和加工丁艺技术的不断提升,芯片技术日益成熟,软件无线电技术得到广泛应用和迅猛发展。无线电系统在整体体系结构上发生了重大变化,正沿着综合化、模块化、通用化和智能化的方向快速推进。无线电系统将模块化、标准化的硬件构成基本平台,通过软件加载技术来实现尽可能多的功能,为多种信号的功能综合和互联互通提供了技术保障。随着模块应用灵活性要求的不断增加,软件维护及升级需求的日益迫切,给软件加载技术提出了更高要求。本文提出了一种基于CPLD的多处理器远程加载管理设计应用方案,系统实现了从远端下发命令字和更新数据即可完成模块的程序更新升级和重新加载,实现软件维护和模块功能切换,满足日益复杂的系统使用要求。

1 数字处理模块

数字处理模块主要完成基带信号调制解调、RS编解码算法实现、收发通道实时控制、导航算法实现、信息层的协议实现以及大量的数据融合算法实现等。硬件设计采用了FPGA+DSP的设计构架,以1颗Altera公司的Stratix系列FPGA和4颗TI公司的DSP作为设计核心完成以上功能实现,框图如图1所示。系统要求数字处理模块要适应系统通用化和智能化的设计要求,具备远程自动更新升级、加载等功能,为系统功能多样化、维护简易化打下基础。根据系统要求和模块设计实际,结合CPLD芯片稳定性高、设计灵活的自身特点,确定采用CPLD作为整个数字处理模块的功能管理芯片,实现对整个处理模块的电源管理、状态检测、上电复位管理、各DSP及FPGA的程序加载管理、远程更新等功能处理。

当系统需要对本模块的软件进行升级或者模块功能重构时,系统将更新命令字和更新内容通过SEDERS总线下发至DSP4,再送入CPLD进行解码、识别分类,根据指令要求启动CPLD对FLASH中的相应空间进行擦除、更新操作。当操作完成后,CPLD强行启动DSP或FPCA,重新加载FLASH中的程序,完成系统软件升级或者模块功能重构任务。

[page]

[page]

2 远程更新硬件实现

远程更新和加载就是系统具有从远端通过下发指令或参数对处理模块中存储的应用程序进行修改升级的功能,模块内部控制单元启动加载模块,完成模块功能重构。反映到硬件功能就是主控芯片要具备擦除、读写模块内存储芯片的功能,可以控制模块内的各处理器及可编程器件重新加载运行新程序。数字处理模块采用4颗DSP芯片和1颗FPGA来完成系统的数据处理任务,因此在系统升级时需要对4个处理器或部分处理器及FPCA的程序进行更新并重新加载。所以主控芯片要具备擦除、读写各DSP和FPCA芯片挂接的FLASH芯片,并能对其完成程序加载。

硬件设计时FLASH芯片采用了集中式设计,多个DSP芯片和FPGA分段共享同一片大容量FLASH。共享存储器有利于提高模块可靠性、模块小型化设计、有利于主控模块对其操作控制,有效降低功能实现复杂度,也有利于扩充模块功能。一般FPGA设计多采用挂接与之匹配的FLASH芯片,这些专用存储芯片不但具备专用接口与FPGA匹配,而且内部嵌入了FPCA信息,硬件设计时只需要将FPCA设计成主动加载模式即可。系统上电后FPGA将自动识别存储器并完成程序加载,整个过程不需要外部干预。但对于通用存储芯片来说FPGA是无法实现自动加载的。而且这种远程控制也是要通过外部干预来实现的,所以FPGA只能设计为被动模式,通过主控模块完成加载过程。而ALTERA公司专门研发了一款MAXⅡ系列的CPLD来实现StratixⅢ系列FPGA的加载管理CPLD硬件框图如图2所示。

2.1 通用接口存储器(CFI Flashl更新

系统将更新数据从上位机下发至处理模块。经过CPLD解码、识别系统更新要求。CPLD将启动擦写模块,对CFI_Flash的相应空间段进行数据擦除操作,同时将更新数据写入存储器中,实现系统程序升级更新。其流程框图如图3所示。

2.2 程序重构

当CPLD按照系统要求将CFI Flash中程序更新完毕后,就会自动唤醒加载模块,对已更新的处理器或FPGA的程序进行重新加载。DSP的加载相对简单,将DSP设计成主机口加载模式,设计框图如图4所示。由CPLD强行复位相应DSP使其进入加载状态,然后从CFI_Flash中分别读出各DSP的目标数据,按照主机口加载时序写入DSP的内部静态存储区,加载完毕再对DSP初始化控制寄存器进行设置,完成加载过程并唤醒各DSP重新运行新程序。完成模块处理器的功能重构工作。

[page]

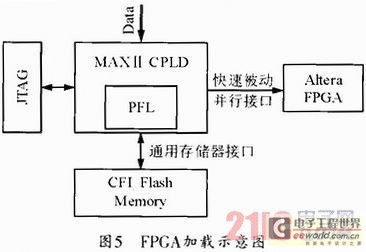

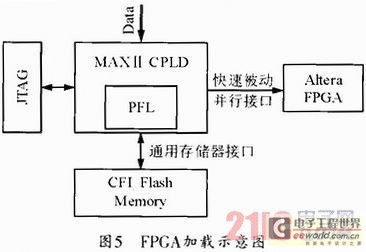

对Stratix系列的FPGA而言,加载过程相对复杂,实现起来比较困难,因为FPGA在加载过程中不仅要满足时序控制,而且加载的数据内部还含有一定的器件信息,需要满足消息格式和CRC校验才能顺利完成加载。而器件信息和CRC校验方程用户是无法得到的,因此只能采用Alte ra公司设计的MAXⅡ系列CPLD来完成加载过程。这款CPLD内部自带一个并行加载模块(PARALLEL FLASHLOADER),此模块对FPCA有专用加载接口,内部嵌入了FPGA的加载控制时序及器件信息,象一道桥梁将FPCA和通用存储器无缝连接,但硬件设计时FPGA必须设置为被动加载方式,如图5所示。系统需要对FPGA程序重构时,只需通过逻辑启动CPLD的PFL模块,PFL模块从通用存储器中读取配置数据,并且将配置数据进行格式转换打包、CRC校验后按照FPGA的加载时序写入FPGA内部,然后上拉配置完成标志位来启动新程序运行,实现FPGA的功能重构。

利用MAXⅡ系列CPLD不仅可以实现单个FPGA程序的加载,也可以根据实际应用需求通过硬件扩展以及在CPLD中增加泽码控制逻辑实现多个FPCA的加载。满足系统复杂的使用要求。

3 结束语

本设计采用MAXⅡ系列CPLD作为数字处理模块的主控芯片,来实现整个模块工作状态检测、时序管理以及多个DSP芯片和FPGA芯片的程序更新升级和加载,充分利用MAXⅡ系列CLPD芯片的硬件资源、合理调用内嵌加载逻辑模块,有效规避FPGA芯片与通用Flash芯片接口不匹配带来的设计缺陷,简化了FPGA芯片程序加载复杂度。不仅可以远程控制更新重构,还可实现动态重构,这都给处理器芯片以及FPGA芯片的加载方式和应用提出了更高的要求。

本模块已经随某通信终端完成了试飞鉴定测试,模块各项指标优异、远程更新、重构功能稳定可靠,均达到了设计要求。实现了系统模块通用化,波形功能多样化,使用维护智能化的设计要求。

引用地址:

基于CPLD的多DSP及FPGA远程加载设计

推荐阅读最新更新时间:2024-03-16 13:03

基于CPLD和接触式图像传感器的图像采集系统

接触式图像传感器CIS(Contact Image Sensor)是继CCD之后于20世纪90年代研究和开发的一种新型光电耦合器件 。它将光电传感阵列、LED光源阵列、柱状透镜阵列、移位寄存器和模拟开关等集成在一个条状方形盒内,其工作原理与CCD较为相似,但与CCD相比,CIS具有体积小、价格低、结构简单、安装方便等优点,目前在传真机、扫描仪及条码解码器等领域可完全取代CCD图像传感器。

本文介绍一种基于复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)使用接触式图像传感器实现的图像采集系统。

1 系统概述

图像采集模块的框图如图1所示,CIS图像传感器在CPL

[应用]

世强代理国内唯一批量供货的32位工业控制DSP供应商进芯电子

近期,进芯电子与全球先进电子元件分销商世强签订分销协议,后者正式代理包括集成电路芯片、电路模块、嵌入式电子系统的硬件和软件等在内的进芯电子全线产品。 据悉,世强作为全球先进的元件分销商,目前已经代理了如SILICON LABS、RENESAS、ROGERS、MELEXIS、EPSON等近百家欧、美、日顶尖半导体企业的产品,特别是2016年1月,上线了线上服务平台——世强元件电商,走上了全面互联网化的道路,进一步为中国数万企业提供技术支持、元件供应等创新服务,获得了业界一致好评。 而,进芯电子是我国专业从事数字信号处理芯片研发的高科技企业,也是国内唯一可批量供货的32位工业控制

[嵌入式]

基于ARM和CPLD的无线内窥系统设计

引 言 目前微米、纳米技术的研究非常活跃,使得微小技术、微型机械电子系统(MEMS)技术得到迅速发展,从而大大促进,医用器材的微型化、微观化,出现了医用光电微传感器(如无线内窥镜)。无线内窥镜以微机电系统为基础,由感知外界信息(力、热、光、生、磁、化等)的微型传感器、控制对象的执行器、信号处理和控制电路、通信接口和电源等部件组成,将信息的获取、处理和执行集成在一起,形成一体化的、具有多种功能的微型系统。 当前,医用无线内窥镜已有产品问世。以色列GI公司早在2001年5月即推出其M2A无线内窥镜产品,并获得美国FDA认证。GI公司生产的胶囊型内窥镜长为26 mm,直径为11mm,重3.5g;采用微功耗CMOS图像传感

[医疗电子]

基于ARM+DSP的嵌入式四轴运动控制器设计

导读:动控制系统已被广泛应用于工业控制领域。近年来,工业控制对运动控制系统的要求越来越高。传统的基于PC及低端微控制器日渐暴露出高成本、高消耗、低可靠等问题,已经不能满足现代制造的要求 。随着嵌入式技术的日益成熟,嵌人式运动控制器已经初露锋芒。 运动控制系统已被广泛应用于工业控制领域。近年来,工业控制对运动控制系统的要求越来越高。传统的基于PC及低端微控制器日渐暴露出高成本、高消耗、低可靠等问题,已经不能满足现代制造的要求 。随着嵌入式技术的日益成熟,嵌人式运动控制器已经初露锋芒。基于ARM技术的微处理器具有体积小、低成本、低功耗的特点,决定其在运动控制领域具有良好的发展前景。 PCL6045BL是一种新型专用DSP运动控

[单片机]

基于DSP6713的IIR格型自适应滤波器

TMS320C6713是TI公司开发的一款新型浮点DSP芯片,它基于超长指令字结构(VLIW),非常适合于做高强度的数学运算,被认为是TI公司运算能力最强的处理器之一。本文使用合众达公司开发的一款基于TMS320C6713芯片的开发板构建了音频信号处理系统,对音频信号的IIR格型自适应滤波处理算法进行硬件验证。 1 硬件系统设计 开发板系统总体方案框图如图1所示。模拟音频信号首先通过高性能前置运算NE5532进行预放,然后进入音频ADC进行A/D转换得到串行输出的数字音频信号,本文使用CIRRUS公司最新专业级音频芯片CS4272,该芯片使用了一个差分模拟结构,采样率高达192 kHz,实际信噪比超过90 dB。接着

[嵌入式]

基于DSP的液晶模块的显示原理

1、硬件电路接口的设计 图1给出了液晶显示模块的硬件电路接口设计框图,该系统采用TI公司的TMS320F206芯片(以下简称F206),其内部带有4KB的FLASH存储器,可以根据系统需要外挂EEPROM作为外部程序存储区。 SEDl335控制器是日本EPSON公司生产的一款液晶显示屏控制器,与同类产品相比,功能最强。主要特点有: 有较强功能的I/O缓冲器; 指令功能丰富; 四位数据并行发送; 图形和文本方式混合显示。 可编程控制器芯片GALl6V8的输入端连接到DSP上,输出为硬件汉字库、液晶控制器、键盘扫描电路提供所需的片选和使能信号。该芯片编程实现容易,可以随时修改其逻辑关系,在

[模拟电子]

TMS320VC5402 DSP与单片机的HPI接口实现

TMS320VC5402(VC5402)两个可编程的多通道缓冲串口(McBSP)能够全双工、快速地与其他同步串口进行数据交换,硬件连接简单,串口的工作模式和传送数据的格式可通过编程实现。DSP和单片机之间的通信一般利用双口RAM,通过串口或DSP的HPI接口实现。 利用双口RAM实现 CY7C026是CYPRESS公司生产的16k×16B高速双口静态RAM,存取速度小于25ns。他具有真正的双端口,可以同时进行数据存取,两个端口具有独立的控制信号线、地址线和数据线,另外通过主?从选择可以方便地扩存储容量和数据宽度。通过芯片的信号量标志器,左、右两端口可以实现芯片资源的共享。 由于DSP的数据是16位,而单片机

[单片机]

IDT 推出业界唯一的预处理交换芯片,增强下一代无线基础设施效能

具备一系列创新预处理功能的 优化互连解决方案使数字信号处理器性能提升 20% IDT TM 公司( Integrated Device Technology, Inc. ;纳斯达克上市代号: IDTI )推出用于数字信号处理器( DSP )集群的、业界唯一现成的预处理交换( PPS )芯片,再次彰显其在为无线基础设施设计提供半导体解决方案方面的领先地位。 IDT 预处理交换芯片( PPS, pre-processing switch )专为无线基带处理应用设计,采用串行 RapidIO ( sRIO )互连,是一种先进的半导体解决方案,集成了一套创新字节级和信息包级处

[新品]

[page]

[page]

YAMAHA_rx-v340_rx-v340rds_htr-5630_htr-5630rds_dsp-ax340维修手册

YAMAHA_rx-v340_rx-v340rds_htr-5630_htr-5630rds_dsp-ax340维修手册 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号