题目分析:本题目的设计意图在于使用FPGA中硬件资源对某些流程固定的软件算法进行加速,即algorithm-hardware codesign,是软硬协同设计中更为具体的一种形式,本题目中的CRC算法只是其中一种实例。这种由硬件电路实现的软件算法通常能够很大程度上的降低计算时间,代价仅是FPGA内部所消耗的一些逻辑、存储资源,但对于如今的FPGA芯片来讲是完全可以接受的。本题目的设立将充分验证MicroZed开发板中Zynq系列芯片的优势,因为它集成了高性能ARM处理器内核、充足外设资源和FPGA逻辑资源,对于软硬件协同设计的嵌入式应用,是很好的选择。

(二)过程说明

1. 软件学习:Vivado+ SDK

要在两周时间内完成挑战题目,需尽快学会题目规定的Vivado + SDK软件开发流程。其中第一个目标就是要搭建起基于ARM CortexA9的嵌入式系统,才能够进行下一步CRC算法的实现和调试。在Vivado 2013.4及以上的版本中都包含支持MicroZed开发板的硬件定义和板级支持包,新建工程时选中就会将开发板的所有信息导入到工程中,十分快捷。

有很多网友或MicroZed、Zynq使用者上传过很详细的图文开发流程,在这里我就不再重复演示了。这些教程包含了从入门级到专家级的MicroZed开发板、Vivado/SDK软件使用教程甚至代码。正是由于这些人乐于分享的精神,才使得国内FPGA设计技术能够快速、深入的发展起来。在这里跟大家推荐一个名字叫“亚当泰勒玩转MicroZed”的连载,中英版都有,但英文版的更全一些。这个入门级的图文教学可以教大家如何从一个新手快速熟悉基于Vivado+SDK的MicroZed开发流程,本题目能够顺利完成离不开这位外国友人的帮助。连载中除了说明开发板的使用、软件设计/调试流程外,还包含部分PS基本外设的使用方法,比如GPIO、中断控制器、三重定时器以及PS与PL进行通信使用的AXI4总线搭建/调试方法等。在这里提一下用Vivado进行设计的一个典型特点:在搭建嵌入式硬件系统时,它采用的是模块图的形式比PlanAhead更直观一些,下图就是本题目最终设计的系统模块图:

其中包含了CortexA9处理器系统、AXI总线互连IP以及PL实现的自定义CRC算法IP。

2. 基于ARM的CRC算法实现(PS端)及性能比较流程

软件CRC算法实现方法有很多种,目前大多使用查表法,具有较低的算法复杂度和运行时间。但是此题目的目的在于比较硬件加速对某种软件算法的性能提升,需要使用与PL端相同的算法实现才更有说服性。所以在ARM中实现的32bit CRC校验采用根据生产多项式按bit异或的方式,需要将输入的32bit整型数据拆分为32个单bit数据进行运算,然后将结果重新组合为32bit整型,如下所示

另外,为确保以太网数据包CRC校验的真实性,在本题目中使用了Wireshark从网络中随意抓取的一个ARP广播包,如下图:

下面向大家说明本题目进行性能比较时采用的流程:

首先,在进行性能比较时,统一时间标准是必要的。由于PS端进行时间计算采用的是TTC三重定时器,将其工作频率设为系统内部ARM_PLL产生的CPU_1X,约为133MHz。同时将其通过FCLK_CLK0信号输出到PL端用作CRC校验模块的工作时钟,能够确保PS端与PL端的计时标准一致性,如下图:

另外,为体现CRC循环冗余校验中的“循环”特点,本人将ARP数据包的完整校验过程分步呈现了出来。使用了开发板上唯一的GPIO按键进行过程控制,每次按键产生一次中断,执行一次中断比较程序。每次中断比较程序进行对比的数据包都会比上一次多一组(32bit),直到完整的ARP数据包完成CRC校验,则继续重复初始的校验过程。

按键中断程序中,首先进行PS端的CRC校验和计时,之后将数据包通过GP总线传送到PL端,PL端接收到完整数据包后进行自动校验和计时,完成后将结果返回PS端,流程如下:Reset Timer—>Start Timer—>Start CRC Calculate Function—>StopTimer—>Get Counter Value—>Output PS Result—>.Packet Transmit—>StartPL CRC FSM—>Read Back Result—> Output PL Result—>Reset Control Reg—>Return.

按键中断比较程序输出内容如下:

Ø每次按键触发后,首先输出提示:

“**********CRC Calculate Begin!**************”

Ø随后输出本次PS与PL进行CRC校验的数据:

“---------Packet is :-----------”

“数据包内容”(32bit为一组)

“---------------------------------”

Ø首先输出PS端CRC校验结果以及计算时间:

“PS_CRC = 0x......; PS_CRC_TIME = ……”

Ø之后输出PL端CRC校验结果以及计算时间:

“PL_CRC = 0x......; PL_CRC_TIME = ……”

连续按下按键,则超级终端返回内容如下:

以上就是本题目的CRC算法比较流程以及PS端的实现方案,接下来介绍PL端的实现方法。

3. 基于FPGA的CRC算法实现(PL端)

题目要求使用GP,HP,ACP总线完成数据帧的传输,如何完成数据帧的传输并界定帧的起始和截止是任务的重点。由于数据帧的长度并不大,也没有高速传输的要求,因此采用了最常用的GP总线。

实现方案:本人选择通过GP总线对自定义外设myip_crc_0中的4个控制/数据寄存器reg0~3进行读写,来完成数据帧的传输以及结果的返回功能。其中reg0为控制寄存器,包含标记帧起始的SOP和帧截止的EOP信号;reg1为数据寄存器,用于接收对端发送的32bit数据帧;reg2和reg3用于存储CRC校验的结果和消耗的时间。在一次帧传输开始后,所有接收的32bit数据会被自动存入FIFO中,当EOP信号有效时开始对FIFO内的全部数据进行连续的CRC校验并进行计时,校验完成后将结果存储到寄存器中并返回给PS端。

设计细节:生成带有AXI从接口的自定义IP核是本题目设计中的一个重点,需要选择好对应参数,并同时生成驱动以备软件使用:

建立好新的IP后需要在AddressEditor中为其分配地址空间

然后进入IP Packager中对其进行各项配置

并且每次修改后记得进入“Reviewand Package”中点击”Re-package IP”进行保存。

IP核生成之后,下一步需要对AXI从接口模块源文件“myip_crc_v1_0_S00_AXI.v”进行部分修改并在其中例化自定义功能模块。该源文件包含AXI Slave接口中每个输入输出信号的含义注释以及AXI协议功能实现部分的代码注释,方便设计人员进行阅读和修改。

在myip_crc_v1_0_S00_AXI.v中除了例化自定义的模块外,对协议本身部分的代码也进行了少许修改,使寄存器reg0~reg3可以同时被PL端进行赋值,并且控制向reg1写入的数据自动写入FIFO中。当接收到EOP信号后,启动CRC运算,连续读取FIFO中的数据包并进行校验,直到FIFO读空后完成本次校验并将结果写入寄存器reg2、reg3中返回。

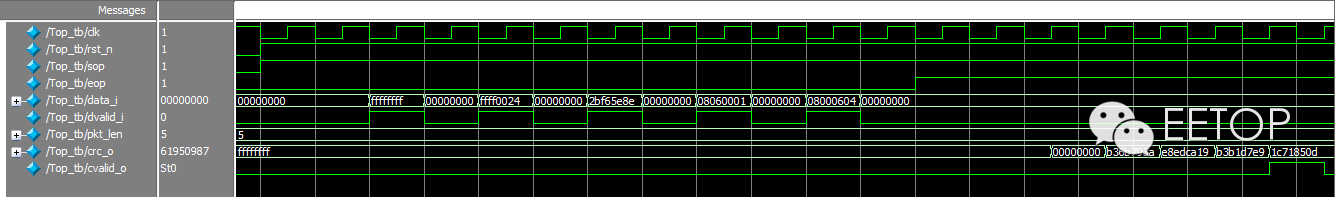

仿真结果:

下图为数据包接收及校验过程仿真,测试的是数据包长度为五的情况

下图为五组连续的校验结果,与超级终端返回的初始五次比较结果吻合

以上便是PL端CRC算法的设计实现方法。

(三)总结

本次为期两周的Zynq极客挑战赛告于段落了,对于楼主来说这次比赛的挑战性还不小。困难主要体现在比赛之前我仅有过MicroBlaze + XPS的SOC经验,没有接触过Zynq器件和Vivado。在短时间内熟悉软硬件、设计流程需要十分专注的学习和尝试,并且寻找合适的学习资源。另外,时间也是一个问题,在挑战期间突发的事情会打乱设计调试的进度,真正用来进行开发的时间也就一个星期左右。优势在于之前是做计算机网络应用方面的,对题目二中CRC算法的FPGA设计实现有一定经验。最终,在规定的时间内完成了题目中的前四个要求,只是还有一些想法未能及时实现,比如使用MAC控制器从网络中实时抓取长度可变、内容较大的数据包进行CRC校验,使本次设计具有更大的应用意义并提高设计难度。

最后,再次感谢EETOP论坛给予本次挑战机会。希望越来越多的FPGA、嵌入式爱好者参与到其中,从中学习、思考、体验,收获更多的知识和技能。同时也祝愿中国的电子设计、制造行业能够迅速发展,不断进步!

上一篇:STM32F4-浮点DSP库的MDK开发环境的设置

下一篇:STM32的CAN总线的标识符过滤器组使用注意事项

推荐阅读最新更新时间:2024-03-16 14:58

设计资源 培训 开发板 精华推荐

- 人工智能机器人“小严”:专注于变频系统业务,24小时全天候在线

- 中国机器人市场进入高速增长期,机器人产业的发展迈入新的层次

- 福伊特一直在协作机器人前沿探索,做到贴近用户的同时为其提供快速且灵活的支持

- 中国老年人口市场巨大,协助老年人生活的机器人应运而生

- FANUC M-410iC机器人:搭载了FANUC最尖端的伺服技术,码垛效率更高

- DARPA为推进制造毫米级到厘米级微型机器人所需的技术制定了一项新计划

- 随着智能机器人的不断发展,以下这些工作岗位在未来20年可能会有风险

- 为了确保铜陵电网迎峰度夏安全供电,智能巡检机器人上线

- 福伊特,抢占先机率先布局中国机器人市场

- 国美在广州和天津投放AGV机器人,用来提高拣货效率

ARM Cortex-M0权威指南(中文)

ARM Cortex-M0权威指南(中文)

京公网安备 11010802033920号

京公网安备 11010802033920号