外层板子原理图

四层板原理图(核心板子)

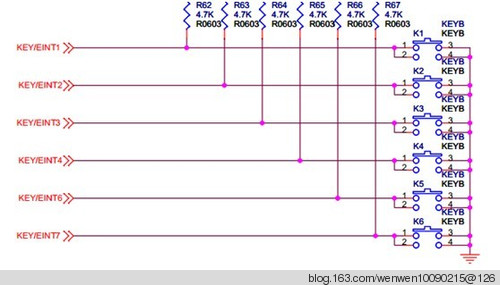

本板子总共使用了留个按键分别是EINT1~EINT7

所以对应的寄存器是GPH1_1~GPH0_7..

首先来查看芯片手册查看关于GPH0寄存器的descriptor

GPH0,1,2,3: 32 in/out pin –CAM IF channel, Key pad, External Wakeup (up-to 32-bit)

大概意思主要想表达GPHO是可被外部唤醒的.

GPH0CON[7] [31:28] 0000 = Input, 0001 = Output, 0010 = WU_INT[7] 0000

GPH0CON[6] [27:24] 0000 = Input, 0001 = Output, 0010 = WU_INT[6] 0000

GPH0CON[5] [23:20] 0000 = Input, 0001 = Output, 0010 = WU_INT[5] 0000

GPH0CON[4] [19:16] 0000 = Input, 0001 = Output, 0010 = WU_INT[4] 0000

GPH0CON[3] [15:12] 0000 = Input, 0001 = Output, 0010 = WU_INT[3] 0000

GPH0CON[2] [11:8] 0000 = Input, 0001 = Output, 0010 = WU_INT[2] 0000

GPH0CON[1] [7:4] 0000 = Input, 0001 = Output, 0010 = WU_INT[1] 0000

PAD CONTROL S5PC100 USER’S MANUAL (REV1.0)

2.2-36

GPH0CON[0] [3:0] 0000 = Input, 0001 = Output, 0010 = WU_INT[0] 0000

那么我们看看可唤醒中断配置寄存器:

5.6.1 Wakeup Interrupt 0_7 Configuration (WU_INT0_7_CON, R/W, Address = 0xE030_0E00)

The value of WU_INTx_y_CON[n] means that 000 = Low level, 001 = High level, 010 = Falling edge triggered,

011 = Rising edge triggered, 100 = Both edge triggered

意思是唤醒中断配置寄存器

000 为低电平有效 001为高电平有效 010为下降沿触发 011为上升沿触发有效 100为两种沿都可以

在看看可唤醒中断掩码寄存器:

Wakeup Interrupt 0_7 Mask (WU_INT0_7_MASK, R/W, Address = 0xE030_0F00)

The value of FLTENx_y[n] means that 0= disable, 1=enable. The value of FLTSELx_y[n]means that 0 = delay

filter, 1 = digital filter

FLTENx_y[n] 0 为使能关闭 1 为使能打开

FLTSELx_y[n] 0为延迟过滤器 1为数字滤波器

Reserved [31:8] Reserved

WU_INT0_7_MASK [n] [n]

Mask for WU_INT[n]

0 = Enabled,1 = Masked (n=0~7)

看完这些寄存器就可以实现按键中断了:

首先了解中断流程:(这里为GPH0)

①:使能引脚的中断方式 --- 也就是上述GPH0CON = GPH0CON & (~(0xf)) | 0x2<<4 <------- >GPH0CON[1]这里暂时用的是key1、根据原理图key1为enter1既为GPH0CON[1]

②:设置中断的触发方式(也就是配置可唤醒中断寄存器)

为WKUP_INT0_7_CON[1]

WKUP_INT0_7_CON = ( WKUP_INT0_7_CON & (~(0x7<<4))) | (0X2<<4);

设置下降沿触发

010

0111<<4

~11100000 = 0001 1111 | 0010 <<4

0001 1111 | 0010 0000

= 0011 1111

所以4-6位该是011 所以就对了上面共八位是0 – 7

③:使能中断屏蔽寄存器(mask)

WKUP_INT0_7_MASK = WKUP_INT0_7_MASK &(~(0x1<<1)) ;

0010 ~ =0 故0为使能关闭中断。

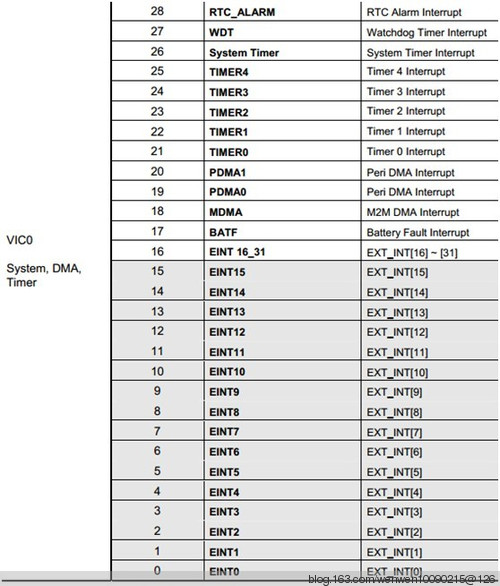

④:使能VIC关于GPH0中断

VIC0INTERRUPT.VIC0INTENABLE |=1<<1; //从下往上数为第2个所以为1

这里为什么使用VIC0呢、是芯片手册给我们提供的。

⑤:注册中断函数并且实现do_irq函数和中断服务函数并且到最后清除中断位

VIC0VECTADDR.VIC0VECTADDR1 = (unsigned int )key1_int;

void key1_int()

{

printf("key1_int\n");

VIC0ADDRESS =0;

VIC1ADDRESS =0;

VIC2ADDRESS =0;

WKUP_INT0_7_PEND = 1<<1;

/*这是关于等待中断WAKEU_PENDING的描述

*/ Wakeup Interrupt 0_7 Pending (WU_INT0_7_PEND, R/W, Address = 0xE030_0F40)

Field Bit Description Reset Value

Reserved [31:8] Reserved 0

WU_INT0_7_PEND [n] [n]

This bit is set if WU_INT [n] is pending.

Writing ‘1’ makes this bit clear. (n=0~7)

0

Note. Even though WU_INT0_7_MASK [n] is masked, this can be pended.

}

void do_irq() /*do_irp函数的实现()*/

{

printf("VIC0ADDRESS = %x\n",VIC0ADDRESS );

( ( void(*)(void) )VIC0ADDRESS)();

}

关于( ( void(*)(void) )VIC0ADDRESS)();

这其实是一个函数指针的强转。

完全可以理解为void (*)();

这样去理解。

通过上述就可以实现一个按键中断。

/*---------------------*/

printf("keven");

上一篇:外设一个一个学_PWM

下一篇:外设一个一个学 for ARM_first

推荐阅读最新更新时间:2024-03-16 15:03

ESP32-C6 系列芯片手册

ESP32-C6 系列芯片手册 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号