一、实验现象

每次按下k0按键2次后,在P0.0输出一个周期是100ms的方波信号。

二、实验目的

掌握内部定时/计数器作计数功能的应用

三、实验任务分析

在前面的3个试验里面,我们都是让T0工作于定时方式,从而产生一段固定的时间。但是T0和T1除了可以用于定时外,还可以用于对外部输入的脉冲进行计数。在这个试验里面,我们学习T0工作于计数方式时的编程方法。

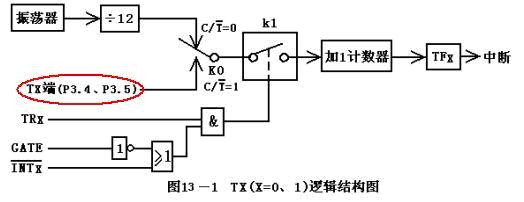

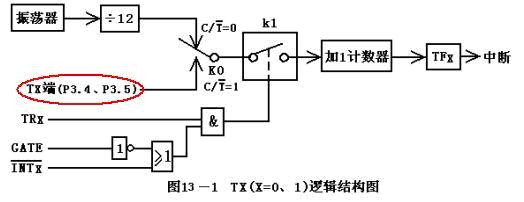

在本试验中,我们用T0对外部按键的动作进行计数。看一下定时/计数器的逻辑图如下图所示:

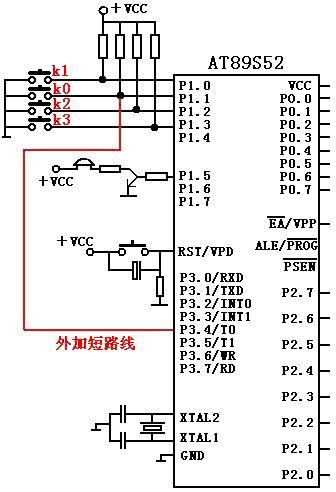

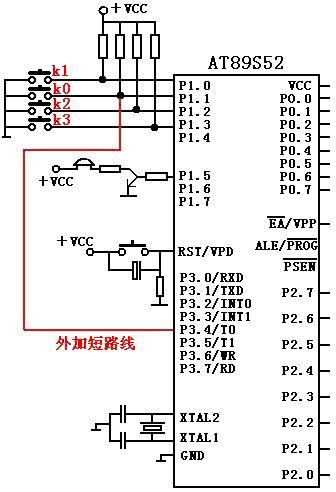

我们发现当C/T=1的时候,定时/计数器T0可对T0(P3.4)端计数,每当T0端产生一个负跳变的时候,计数器执行一次加1的运算。为了让k0按键按下的时候,在p3.4端产生一个负跳变,我们首先要做的是把p1.1和p3.4用导线短路,如下图13-2所示,这样才能满足试验要求。

这个试验的思路如下:让T0在计数2次时,产生溢出中断,在T0的中断服务程序我们启动T1开始计数,然后在T1的溢出中断里面把P0.0取反,这样就可以产生符合我们实验要求的信号

为了让k0按下2次后T0产生溢出中断,我们可以让T0工作于计数方式,并选择可重新置入计数初值的8位计数器模式2;为了产生100ms的方波信号,我们让T1工作于定时方式,选择16位计数器模式。所以tmod的初值应该是:0001 0110,即16h。

四、实验程序

org 0000h

ajmp main

org 000bh ;T0溢出中断入口地址

ajmp time0

org 001bh

ajmp time1 ;T1溢出中断入口地址

org 0020h

main: clr p1.5

setb p0.0

mov sp,#70h ;设置堆栈

mov tmod,#16h ;T0、T1初始化,T0工作在计数方式,T1工作在定时方式

mov tl0,#0feh ;T0置计数初值,计数2次后产生溢出中断

mov th0,#0feh ;计数初值置入常数缓冲区

mov th1,#3ch ;T1置入计数初值,产生50ms定时

mov tl1,#0b0h

setb et0 ;允许T0溢出中断

setb et1 ;允许T1溢出中断

setb tr0 ;启动T0计数

setb ea cpu开中断

ajmp $

time0: setb tr1 ;启动T1计数

reti

time1: mov th1,#3ch ;T1重装计数初值

mov tl1,#0b0h

cpl p0.0 ;P0.0取反

reti

end

五、几点说明

在运行该程序时,有时可能会发现并不是按键按下两次后产生信号,这是因为手动按键的时候可能会发生抖动情况,导致计数器计数的缘故。

引用地址:

单片机学习之十七:计数器的应用

推荐阅读最新更新时间:2024-03-16 15:09

基于8051的微控制器在系统编程

介绍 Dallas Semiconductor基于8051的 微控制器 类产品中,许多型号都支持通过通用RS-232串口实现在 系统编程 。在系统编程意味着 程序 和/或数据存储器能够在不用拆解嵌入式系统来替换存储器的情况下进行修改。这种特性强调易使用性和多功能性,在所有嵌入式设计中增加了许多非常重要的特性: 允许硬件在工厂组装和存放,而在出厂前才进行软件定制, 需要进行软件升级时,消除了在现场拆解 器件 的高昂代价, 允许对位置不可达的应用进行软件升级, 访问专用配置与状态寄存器,以及使用存储器加密的方式把软件加载到安全微控制器。 具有这种特性的器件包括: DS2250, DS2250T

[工业控制]

avr单片机数码管显示时钟

// 数码管 数据P0口,数码管控制P2口 #include avr/io.h #include avr/delay.h #include avr/pgms PAC e.h #include avr/signal.h #include avr/interrupt.h #define code PROGMEM #define uchar unsigned char #define uint unsigned int code const uchar LED _7 = {0x28, 0x7E, 0xA2, 0x62, 0x74, 0x61, 0x21, 0x7A, 0x20, 0x60,0xff};//common of

[单片机]

PIC系列8位单片机的基本组成

PIC系列8位单片机为适应各种不同的用途,有多种型号可供选用。但是,尽管PIC单片机有不同的档次和型号,但其最基本的组成则大同小异。因此,在这里先从型号PIC16F84的单片机入手,讨论其基本组成。PIC16F84是双列直插式(DIP)塑料封装,最大时钟频率可达4MHz。现为MicroChip公司的独家产品,关于其具体技术指标,可查阅该公司的产品手册,或在网址www.Microchip.com上查找。 PIC16F84单片机的引脚排列可参阅本期本版的16F8X系列简介一文。本文的附图是该器件的主要组成部分。PIC16F84虽然体积不大,但仍然是一个完整的计算机,它有一个中央处理器(CPU)、程序存储器(ROM)、数据寄存器

[单片机]

自动驾驶与SOA架构下MCU的变化 兼论国产MCU

自动驾驶与SOA架构下MCU的变化主要是算力要大幅提升,运行频率至少在300MHz以上,片上Flash容量不低于20MB,足以运行轻量虚拟机,还要具备矢量运算能力。汽车SOA架构即服务导向架构或软件定义汽车架构,在硬件领域对应的就是Zonal架构,即中央计算服务器架构,也有称之为域/区架构。 典型Zonal架构 图片来源:互联网 整车厂已在分布式架构软件开发上投入了大量精力财力人力,这是一笔巨大的研发资产,物理上的计算单元只有1-2个,要想复用分布式架构上的软件成果,逻辑上需要虚拟出原本一个功能对应一个ECU的架构。 大多数现代ECU将运行AUTOSAR(AUTomotive Open System ARchite

[汽车电子]

AVR单片机教程——数码管

先解答之前一个思考题:如果不把引脚配置为输出而写高电平,连接LED会怎样? 实验结果是,LED会亮,但相比于输出高电平的情况,亮度很低。这是为什么呢? 通过上一篇教程我们知道,引脚输入输出模式是由寄存器DDRx中DDxn位控制的,可以推断出 pin_mode 函数会改变一个引脚对应的DDxn值,输入为0,输出为1,而其复位后的值为0,即输入,因此如果不把引脚配置为输出,它的模式就是输入。类似地 pin_write 函数会改变PORTxn,其值为函数的第二个参数。 所以不配置输出而写高电平的结果就是,这一引脚的DDxn为0,PORTxn为1,是带上拉电阻的输入模式。上拉电阻相当于VCC接电阻后再接在引脚上,外部电路是引脚

[单片机]

单片机是由哪几部分组成的?

单片机是由哪几部分组成的? 答:单片机是在一块集成电路芯片上装有CPU和程序存储器、数据存储器、输入/输出接口电路、定时/计数器、中断控制器、模/数转换器、数/模转换器、调制解调器以及其他部件等的系统。视其型号不同,其组成部分各异。

[单片机]

飞思卡尔以全方位32位MCU抢攻智能手表商机

飞思卡尔(Freescale)将以全方位32位元微控制器(MCU)抢攻智慧手表商机。由于智慧手表须兼具运算、无线连结和长时间待机能力,对内建MCU的规格需求较一般物联网(IoT)装置更严格,因此飞思卡尔正全力扩充Cortex-M0+与Cortex-M4核心32位元MCU产品阵容,以满足各种等级的智慧手表设计,卡位市场先机。

图说:飞思卡尔市场行销暨业务发展经理刘聪雄认为,智慧手表与行动医疗结合的应用将愈来愈受到市场青睐,成为ICT业者未来发展重点。

飞思卡尔市场行销暨业务发展经理刘聪雄表示,继智慧型手机、平板装置后,智慧手表可望掀起新一波ICT产业荣景,因此不仅苹果(Apple)、索尼(Sony)和三星(Samsung

[单片机]

一种快速位同步时钟提取方案及实现

摘 要 :本文比较了两种常用位同步提取电路的优缺点,在此基础上提出了一种基于CPLD/FPGA、用于数字通信系统的新型快速位同步方案。此方案借助Altera的设计工具设计了位同步提取电路,并利用FPGA予以实现,同时给出了该电路的仿真试验波形图。 引言 在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发同步,而且在获取祯同步、群同步及对接收的数字码元进行各种处理的过程中,也为系统提供了一个基准的同步时钟。 随着可编程器件容量的增加,设计师倾向于把位同步电路设计在CPLD/FPGA芯片内部。因此,本文采用Quartus II软件设计了一种新型的位

[应用]

单片机创新实践应用.

单片机创新实践应用. 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号