S3C2440时钟控制逻辑可以产生FCLK、HCLK、PCLK和UCLK。FCLK为CPU时钟。HCLK为AHB总线外设时钟,包括存储控制器、中断控制器、LCD控制器、DMA控制器等。PCLK为APB总线外设时钟,包括看门狗、IIS、IIC、PWM定时器、MMC接口、ADC、UART、GPIO、RTC和SPI等等。UCLK专用于USB主机或设备接口时钟。

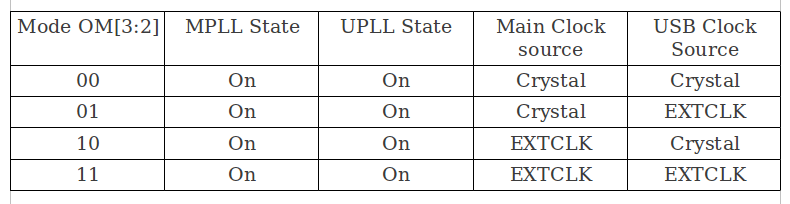

时钟源的选择:

时钟源的选择是通过OM3和OM2管脚控制的,时钟源可以是外部晶振,也可以是外部时钟。

S3C2440有两个锁相环(PLL),一个用于FCLK、HCLK和PCLK的MPLL,另一个专用于UCLK的UPLL。

MPLLCON和UPLLCON寄存器用于设置FCLK和UCLK的时钟频率,那么最后的时钟频率是如何计算的呢,有如下公式:

对于FCLK:

Fout= (2 * m * Fin) / (p * 2S)

m= (MDIV + 8), p = (PDIV + 2), s = SDIV

对于UCLK:

Fout= (m * Fin) / (p * 2S)

m= (MDIV + 8), p = (PDIV + 2), s = SDIV

S3C2440数据手册上也给出了典型值,我们也来验证一下他给的设置是否正确。比如UCLK为48MHz,他给的MDIV为56,PDIV为2,SDIV为2,那么UCLK为多少呢,依照上面给的公式计算得到如下值:(56+8)*12/((2+2)*2²)=48,结果正确。如果我要设置FCLK为400MHz,数据手册上也没有给出参考,唯一接近的是405MHz,没有关系,我们自己来计算,下面给出一组参考值:

MDIV= 92、PDIV= 1、 SDIV= 1,大家依照上面的公司计算一下,看FCLK是否为400MHz。

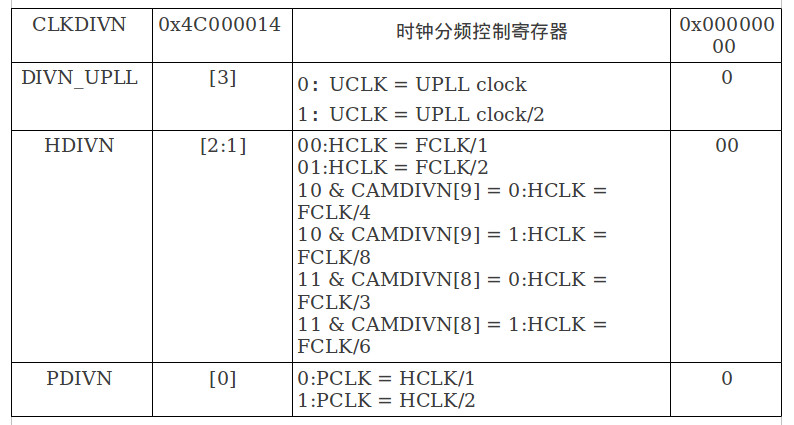

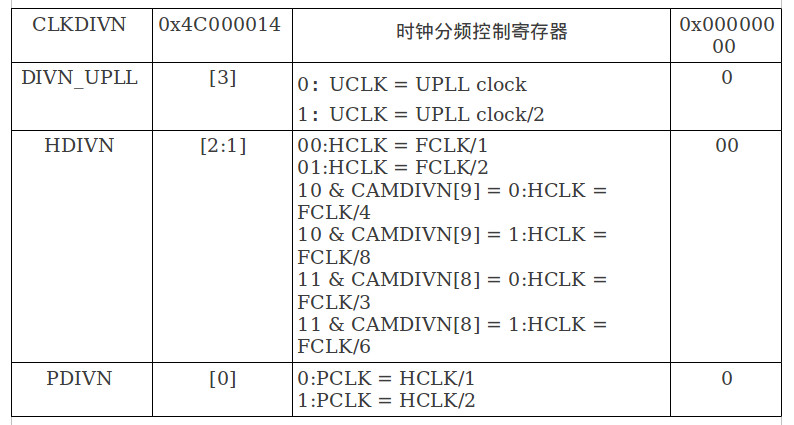

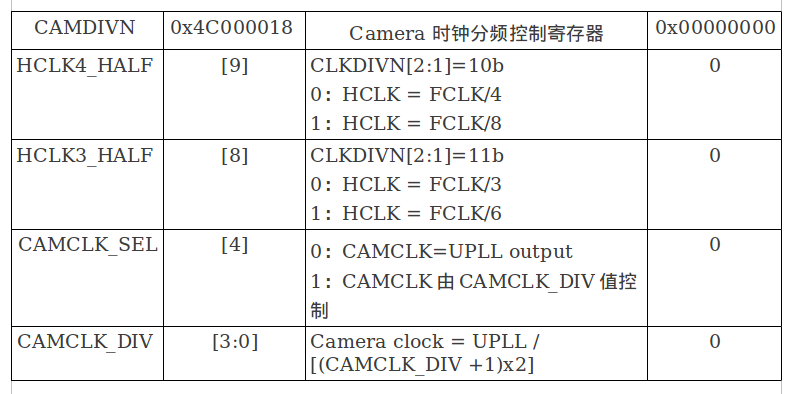

前面也只是设定了FCLK和UCLK的时钟,还有HCLK和PCLK没有设置,HCLK和PCLK是通过FCLK分频得来的。通过CLKDIVN寄存器来控制。

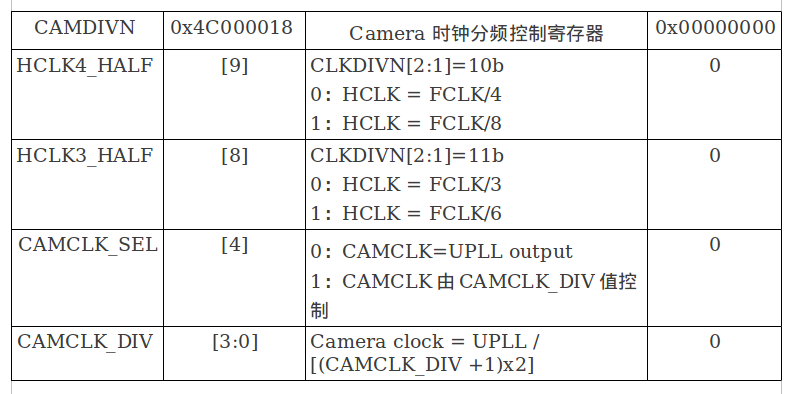

也就是说还和CAMDIVN寄存器有关。

关键字:S3C2440 时钟分析

引用地址:

S3C2440时钟分析

推荐阅读最新更新时间:2024-03-16 15:32

U-Boot移植(3)增加对S3C2440的支持

6、S3C2440是S3C2410的改进版,它们的操作基本相似,只是在系统时钟的设置、NAND Flash控制器的操作等方面有一些小差别。。而下面我要做的就是令一个U-Boot二进制代码既可以在S3C2410上运行,也可以在S3C2440上运行。 虽说我的板也是S3C2410的,但是增加S3C2440的U-Boot练习,可以提高我们的能力,为后面的学习打下基础。 GSTATUS1寄存器的值:0x32410000表示S3C2410,0x32410002表示S3C2440。 S3C2410:FCLK=200MHZ;S3C2440:FCLK=400MHZ,UCLK=48MHZ; 搞清楚之

[单片机]

基于Linux平台上S3C2440的物流配送系统设计

1 相关核心技术概述 1.1 移动定位技术 目前的移动定位技术已经非常成熟,最主要的有3类: ① 利用卫星进行后方交汇的定位技术, 即GPS(Global Positioning System,全球定位系统),是由美国建立的一个卫星导航定位系。利用该系统,用户可以在全球范围内实现全天候、连续、实时的三维导航定位和测速;另外,还能够进行高精度的时间传递和精密定位。 ② 利用移动通信技术提供位置服务的定位技术,即CellID (Cell Identification,小区识别码),通过识别网络中哪一个小区传输用户呼叫,并将该信息翻译成纬度和经度来确定用户位置,从而实现定位。确保终端在GPS定位失去信号的情况下, 保持最低限度的定位

[嵌入式]

基于S3c2440的I2C驱动与测试程序追踪交叉分析

VMware虚拟机+Fedora10, 硬件平台TQ2440, 内核2.6.30.4 对应的驱动程序豁然开朗, 然后自己添加了一些dev_dbg后, 对于不理解的地方也有了一定的参考提示, 记录下来与大家分享。 测试程序如下: /*i2c_test.c * hongtao_liu */ #include #include #include #include #include #include #include #include #define I2C_RETRIES 0x0701 #define I2C_ TI MEOUT 0x0702 #define I2C_RDWR 0x0707 /*********定义struct i

[单片机]

S3C2440裸机------LCD_LCD控制器编程

我们通过配置LCD控制器的相关寄存器实现这三个函数 struct lcd_controller s3c2440_lcd_controller = { .init = s3c2440_lcd_controller_init, .enalbe = s3c2440_lcd_controller_enalbe, .disable = s3c2440_lcd_controller_disable, }; 具体代码及相关寄存器注释如下: 1.s3c2440_lcd_controller.c #define HCLK 100 void jz2440_lcd_pin_init(void) { /* 初始化

[单片机]

S3C2440 Linux驱动移植——按键

开发板:TQ2440 内核版本:2.6.32 1. 硬件链接图 四个输入引脚: EINT0-----( GPF0 )----INPUT---K4 EINT2-----( GPF2 )----INPUT---K3 EINT4-----( GPF4 )----INPUT---K2 EINT1-----( GPF1 )----INPUT---K1 2. 相关的数据结构 移植所需要的数据结构位于include/linux/gpio_keys.h中。 #ifndef _GPIO_KEYS_H #define

[单片机]

arm920t中S3C2440、S3C2450和S3C6410的区别

三星目前推出了S3C6400和S3C6410,都是基于ARM架构的,而且硬件管脚兼容,应该说大致的功能基本相同,比较明显的区别就是S3C6410带有2D/3D硬件加速 S3C2440其实是一个很不错的CPU,价格便宜、内部资源多、最主要的是国内很多人使用,相关的资料比较多。ARM920T内核, 400M主频,支持NAND FLASH、NORFLASH、SDRAM、支持STN/TFT LCD、4通道DMA、3通道UART、2通道SPI、IIC总线、IIS/AC97音频控制器、SD/MMC控制器、2通道USB HOST 1通道USB DEVICE、4通道PWM、8通道A/D转换、触摸屏控制器、RTC、CMOS摄像头、多功能

[单片机]

信号完整性分析基础系列之九--时钟的抖动测量与分析

时钟是广泛用于计算机、通讯、消费电子产品的元器件,包括晶体振荡器和锁相环,主要用于系统收发数据的同步和锁存。如果时钟信号到达接收端时抖动较大,可能出现:并行总线中数据信号的建立和保持时间余量不够、串行信号接收端误码率高、系统不稳定等现象,因此时钟抖动的测量与分析非常重要。 时钟抖动的分类与定义 时钟抖动通常分为时间间隔误差(Time Interval Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cycle to cycle jitter)三种抖动。 TIE又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量。理想时间位置可以从待测试时钟中恢复,或

[测试测量]

s3c2440裸机-LCD编程(一、LCD硬件原理)

1.LCD示意图 下图是LCD示意图,里面的每个点就是一个像素点。 它里面有一个电子枪,一边移动,一边发出各种颜色的光。用动态图表示如下: 电子枪是如何移动的? 有一条CLK时钟线与LCD相连,每发出一次CLK(高低电平),电子枪就移动一个像素。 颜色如何确定? 由连接LCD的三组线RGB三原色混合而成:R(Red)、G(Green)、B(Blue)确定。 电子枪如何得知应跳到下一行? 有一条HSYNC信号线与LCD相连,每发出一次脉冲(高低电平),电子枪就跳到下一行,该信号叫做行同步信号。 电子枪如何得知应跳到原点? 有一条VSYNC信号线与LCD相连,每发出一次脉冲(高低电平),电子枪就跳到原点,该信号叫

[单片机]

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号