电压调节技术与频率调节技术的结合使用为时钟切换添加了新原则,以确保新时钟频率拥有安全的电压电平。此外,电压调节功能需要在SoC内创建电压域。这将在两个可变电压域之间或可变电压域和静态电压域之间创建电压域接口。跨越接口的可变电压电平差为接口设计带来了独特挑战。时钟、信号电平转换以及电压域隔离等问题都必须仔细考虑,以确保最短延迟和信号完整性。

先进电源控制器

作为美国国家半导体PowerWise技术的一部分,先进电源控制器(APC)旨在协助调节电压域的电压控制。APC支持闭环自适应电压调节(AVS)和开环动态电压调节(DVS)。APC支持动态频率调节功能,带有至时钟管理单元(CMU)的接口,可为SoC提供时钟信号。电压电平可通过PowerWise接口(PWI)传送给芯片外协同电源单元。硬件性能监控电路(HPM)用于AVS闭环电压控制。APC根据HPM提供的芯片性能信息,决定最佳的供电电压,以实现目标性能水平。在决定电压电平时,SoC制程变化、SoC晶粒温度变化、稳压器偏置或偏差以及系统静态电阻压降都会自动得到补偿。DVS模式则依照预先设定的电压频率对照表进行操作。

参考设计

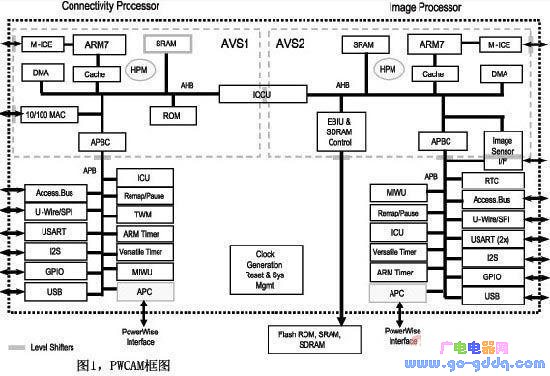

PowerWise Camera(PWCAM)参考设计测试芯片用于技术验证和演示。PWCAM是模拟通用双处理器架构。图1是PWCAM的框图。PWCAM包含两套独立的基于ARM7的处理器系统:连接处理器和图像处理器。每套系统都有一组AHB和APB外设。每个CPU、AHB和APB都是由同一系统时钟驱动,时钟频率高达96MHz。连接处理器和图像处理器通过核间通信单元(ICCU)进行通信。这个通信单元是异步AHB-AHB桥。只有图像处理器可以直接访问外部存储器。设计目标是为了将独立的频率和电压调节功能引入连接处理器和图像处理器,这要求对APC的设计和集成进行恰当区分。

AVS中的时钟切换

对于电压调节与频率调节功能整合而言,最重要的要求是在频率还未切换之前,确保新频率所需电压到位。如果调高时钟频率,在时钟切换为新频率之前,电压必须提升至足够高的水平。如果调低时钟频率,时钟可以立即切换为新频率,因为电压电平已经足够。为了满足这个要求,时钟调节控制必须通过APC。APC利用目标索引和当前索引等接口协议,来批准实际系统时钟切换。

AVS电压域分区

一般而言,电压调节与时钟频率调节总是结合在一起。时钟域边界自然成为AVS电压域边界的选择。时钟域边界的异步接口使得多电压AVS部署变得更为简单。然而,由于性能原因,有时可能需要采用同步接口。将IP块集成进AVS电压域通常需要IP块级的分区改变,以便分隔电压域。很多IP块包含不只一个时钟域。例如,外设块包含一个内部总线接口时钟和另一个外设时钟。内部总线时钟根据系统时钟进行调节,而外设时钟则按照固定频率运行。相对于对IP进行重新分区以将IP块集成到AVS电压域内,有时让IP块固定频率部分以最低AVS电压电平进行操作,从而使整个IP块集成到AVS电压域内,更为容易。

PWCAM分区需要考虑这些因素。图1给出带有电压域边界的PWCAM,用于控制AVS的嵌入式APC和HPM,以及需要信号水平转移的接口。此外,连接处理器内的SRAM也进行分区,以便由存储器保留电压供电。存储器保留电压可以在进行频率调节时追踪AVS电压,但有下限箝位电压,确保即使逻辑部分断电或在不合适电压电平下,SRAM始终保持有效数据。

电平转换及断电信号箝位

有两种电压域接口,一种是静态电压域和AVS电压域之间的接口;另一种是两个独立AVS电压域之间的接口。信号穿越电压域边界,需要将电平转换以便目的域能正确识别。

PWCAM 采用的电平转换策略确保进出域的信号都有位于AVS域边界的电平转换器。除了执行电平转换之外,电平转换器还可起到屏蔽作用,将信号保持在相应的电压域内,最大限度减少信号完整性问题。如果AVS电压域支持断电功能,系统在断电状态下将输入及输出箝定在已知状态非常重要。这种箝位功能很容易就能整合到电平转换器内。

电压域边界的同步定时

自适应调节电压域里的信号定时根据电压电平的变化而变化。如果电压域采用同步接口,在设计信号路径和时钟路径时,要仔细考虑定时路径的可变特性。

AC定时路径

如果任何交流定时路径(输入路径或输出路径)的部分在调节电压域内,输入设置/保持时间或输出有效时间在调节电压范围内大幅度波动。如果技术规格无法承受这样大的变动,则必须采取措施将这种变动减至最少。类似一般定时优化技术,通常是使取样反转尽量接近电压域边界。

内部定时路径

与可变定时相关的内部路径是指两个电压域之间的反转至反转(flop to flop)定时路径,而其中至少有一个是电压调节域。由于电压调节功能与时钟频率调节功能结合在一起,因此当电压向下调节时,会有更多的设置时间。时钟路径的可变定时则会使调节电压域与静态电压域之间的时钟偏差也随之改变。电压下调幅度越大,时钟偏差也越大。最后所得到的结果是信号路径的周期时间会缩短,而且也会出现保持时间的问题。添加时间延迟补偿电路以便为所有可能出现的定时 时间转变作出补偿并不可行,因为时钟的偏差幅度太大,实在无法预测。为了解决这个可变定时时间问题,关键是添加时钟同步功能,以尽量减少时钟偏差,更重要的是,使时钟偏差幅度可以预测。

AVS/DVS设计考虑因素

与典型系统设计相比,进行多电压调节电路设计需注意以下几方面:额外的资料库特征化和定时验证点;在设计体系、分区和编码等方面进行电压域考虑,协助正确布局;电平转换器插入及校验;扫描插入、缓冲插入及ECO都必须考虑电压域。

结论

由于电平调节的自适应性,多电压AVS对于功率优化是非常有效的。采用多个调节电压域,确实会使设计及实施变得更为复杂。但PWCAM测试芯片的例子表明,只要进行适当规划和执行,其复杂程度在可控范围内。功耗的大幅度降低表明这种努力是值得的。

上一篇:基于单片机的嵌入式网络接入设计方案

下一篇:基于G.729语音压缩编译码算法的嵌入式语音存储系统设计

推荐阅读最新更新时间:2024-03-16 15:54

ESP32-C6 系列芯片手册

ESP32-C6 系列芯片手册 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号