引言

在目前的掌上电脑等嵌入式系统中,SD(securedigital)卡以其体积小和引脚数少的优势,提供了比CF更好的外部设备扩展解决方案。因此,如何在系统中集成SDHost控制模块,以及在嵌入式操作系统里面实现其驱动程序,都是目前嵌入式系统设计者要考虑的问题。

本文实现所采用的开发平台是基于SAMSUNG公司的S3C2410AARM微处理器,利用处理内部的SD控制模块,采用GPIO扩展的方法实现SDHost控制器。

使用S3C2410A的SD控制模块,通过对GPIO功能的扩展来完成SD的检测和写保护的功能,实现SDHost控制器相对比较灵活。在进行驱动程序开发过程中,对SD卡检测进行防抖动处理是必要的,必须根据系统电路特性来确定合适的检测时机,在驱动程序里面实现防抖动处理,保证整个系统的效率。

1 SDHost硬件设计

SCDA1A0100是ALPS公司生产的SD卡连接插槽,采用高可用的滑动触点开关,能够准确地检测到卡插入的时机。

通过小型化和薄型化设计,已经广泛应用于PDA,数码相机和个人电脑。当插槽有SD卡插入时,SD卡会触动槽内的触点开关,引起卡的检测引脚和写保护引脚的相应电平变化。

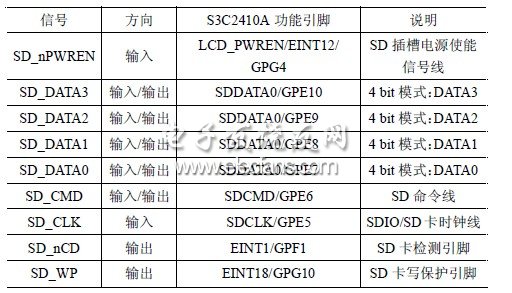

Samsung的S3C2410A内部支持SDHost的控制模块,有SDHost控制寄存器和可以用于SDHost控制器的IO引脚,可用编程的方法对其功能进行选择;但对于SD卡的检测,写保护和插槽的电源使能等功能没有专门的引脚。在本文实现中,对于卡检测、电源引脚,通过GPIO扩展来实现。部分引脚定义如表1所示。

表1 S3C2410A部分GPIO引脚功能定义

S3C2410A的GPIO引脚分为GPA,GPB等8组,每组的IO引脚有控制寄存器(GPxCON),数据寄存器(GPxDAT),Pull-Up寄存器(GPxUP)进行控制。每根引脚所在的GPxCON里有对应位控制其功能,通过对GPxCON编程来控制其功能,某一时刻,该引脚只能使用一种功能。

对于SD卡检测引脚,需要配置成外部中断源(EINTx),对应的EXTINT0,EXTINT1和EXTINT2寄存器控制该中断源的触发模式:低电平触发,高电平触发,前沿触发,后沿触发或是前后沿触发。

S3C2410A时钟控制逻辑有两个锁相环路PLL(phaseLOCkedloop):UPLL专用于USB时钟;MPLL能够产生系统要求的3种时钟信号:FCLK供CPU内核使用,HCLK供系统总线使用,PCLK供外部总线使用。通过对MPLL控制寄存器MPLLCON配置,可以产生需要的时钟频率。

在时钟控制逻辑里,寄存器CLKCON用来控制如USB,LCD,UART,SD等接口模块的时钟使能。其中bit[9]用于控制SD/MMC接口的时钟。SDHost控制器不能直接使用PCLK信号。正常工作模式下,FCLK为266MHz,PCLK为66.5MHz,而SD卡的最高时钟为25MHz,MMC卡最高为20MHz。通过对SDIPRE寄存器的bit[0-7]设置可以对PCLK进行分频,选择合适SD/MMC卡的工作频率。分频公式为:

Clockrate=PCLK/2/(SDIPRE[0-7]+1)

2 驱动程序的实现

2.1 驱动程序体系结构

我们为开发平台上运行的WindowsCE系统开发了SDHost控制器的驱动程序。WindowsCE下,驱动程序是用户态的DLL,这些DLL向内核提供一些接口函数,这样设备管理模块就可以通过这些函数与具体的硬件设备进行通信。

WindowsCE的驱动程序模型主要有两种类型:流式接口驱动和本地设备驱动。流式设备驱动向上层提供统一的流式设备接口,而本地设备驱动可根据具体设备要求提供相应接口。

本文实现中SDHost的驱动程序采用流式接口驱动模型。

驱动程序要实现相应的XXX_Open(),XXX_Close(),XXX_Init(),XXX_Deinit(),XXX_IOControl(),XXX_Read(),XXX_Write(),XXX_Seek(),XXX_PowerUp(),XXX_PowerDown()等接口函数,其中XXX为设备驱动的前缀,应用程序可以通过文件操作来控制设备。

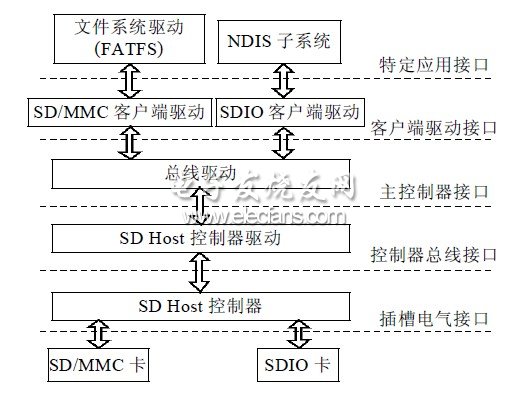

为了减少了SDHost驱动程序设计的复杂性,使其具有较好的可移植性,采用SDHostDDK,它在BSQUARESD协议栈的基础上,提供了平台独立的总线和客户端驱动和一组标准化的API供使用。BSQUARESD卡的协议栈结构如图1所示。

图1 SD卡协议栈体系结构

该结构的设计很大程度上减少了SDHost驱动程序设计的复杂性,使SDHost控制器驱动程序设计可以专着于硬件相关的部分。总线驱动是SD卡客户端驱动程序和SDHost驱动程序之间的一个抽象层,它为SD卡客户端驱动提供平台独立的服务接口。SDHost驱动程序需要完成处理器和硬件平台相关的处理,向上层驱动提供统一的服务接口。

2.2 中断控制

中断控制是设备驱动程序里的关键部分,它关系到操作系统的实时相应速度和系统的整体性能。WindowsCE是通用的嵌入式系统,它在中断处理方面也有一定实时能力。

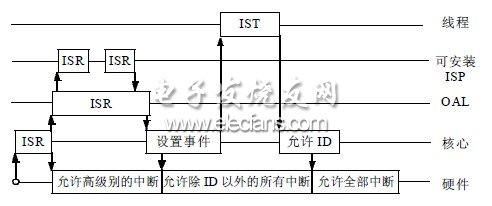

WindowsCE处理中断的过程分为两部分实现:核心的ISR和用户线程IST。ISR实现一般要求短小精悍、效率很高,它只实现简单的功能:响应设备中断并返回一个中断标识码。IST是用户态线程,负责处理具体的中断事务。

当有硬件设备产生中断时,系统进入核心ISR执行,响应设备中断并返回一个中断标识码,核心根据返回的中断标识码设置相应的事件,该事件将引起IST的执行,处理具体的中断事务。处理过程如图2所示。

图2 WindowsCE中断处理过程

本实现中用到了下列中断:SD卡检测中断,SDIO中断和DMA0中断(DMA0专用于SDHost的DMA数据传输)。SD卡检测中断IST负责检测SD卡的插入和拔出,通知上层应用SD插槽的状态;SDIO中断IST只是简单的通知总线驱动有SDIO中断产生,具体处理交给SDIO卡的驱动程序;DMA0中断IST负责处理SD的DMA数据传送。

在WindowsCE中,由于驱动程序DLL运行在用户态,因此驱动程序要访问硬件寄存器,必须在驱动程序的进程空间分配一段虚拟空间,然后将这段虚拟空间映射到硬件寄存器所映射到内核的虚拟地址才能够完成相应的访问。SDHost驱动程序在初始化的时候,必须进行资源分配和地址映射,配置好各个GPIO引脚的功能;然后需要创建事件和相应的中断标识码的关联,创建中断服务线程IST,准备进行中断响应服务。

3 卡检测与防抖动

系统初始化时,SD_nCD检测引脚被设置为上升沿和下降沿触发,因此引脚电平发生变化时,都会有中断产生。当硬件产生中断时,系统进入核心ISR,对SD_nCD进行检测,返回相应的中断标识码,对于是SD插入还是拔出,则由驱动程序的IST来处理。

由于SD卡插槽采用的是机械式开关,在插拔卡的时候,机械开关断开、闭合时会有抖动,导致SD卡检测引脚的电平不稳定,从而有可能引起对卡的状态的误判。这样会导致加载上层驱动,初始化失败造成系统宕机。为了使每次插拔只响应一次,必须要采用相应的方法来防止抖动,避开按键按下的抖动时间。

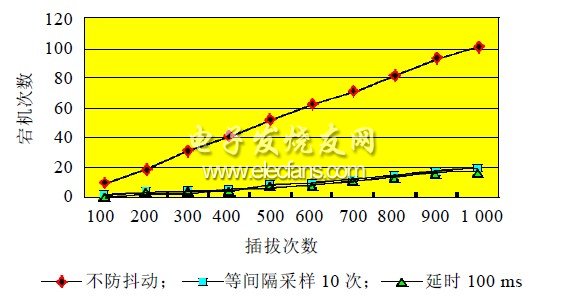

在驱动程序IST里采用延时采样的方法来避免抖动,同时也尝试了多次采样的检测方法来避开用户按键的抖动时间。

延时采样是IST在收到SD卡检测事件以后,并不是立刻进行引脚信号判断,而是延时一段时间采样,延迟时间要根据系统电路特性而定,然后检测引脚信号,判断插槽的状态是卡插入还是拔出。多次采样方法是IST在收到SD卡检测事件以后,要对引脚进行多次等间隔采样,根据采样出的多数电平信号的值来决定插槽卡的状态。多次采样的方法可以有更短的响应时间,当采样出的电平信号多数值不能决定卡的状态时,需要进行重新采样判断。

对于延时采样的防抖动方法,必须考虑到实现的效率。

ISR运行于系统核心态,它的延时会影响整个系统,导致用户的输入响应时间过长,造成整体性能的下降。而WindowsCE的驱动程序是用户态的DLL,作为用户进程来调度,因此在SDHost的驱动程序里实现防抖动,可保证系统整体性能不下降。

对于上述两种防抖动方法,我们进行了连续插拔的测试,结果如图3所示。测试结果表明,这两种方法都取得了较好的效果,基本上解决了SD卡检测的抖动问题。

图3 SD卡插拔宕机次数测试

4 结语

本文介绍的SDHost控制器已经应用在工程实践中,结果表明设计是灵活有效的,防抖动设计对于类似的设计也具有一定的借鉴意义。

上一篇:嵌入式操作系统中USB双向通信的设计与实现

下一篇:嵌入式实现地铁杂散电流监测装置

推荐阅读最新更新时间:2024-03-16 15:55

现代操作系统(原书第4版)

现代操作系统(原书第4版) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号