一、I2S控制器结构框图

S3C2440A的Inter-IC Sound (IIS)总线接口作为一个编解码接口连接外部8/16位立体声音频解码IC用于迷你碟机和可携式应用。IIS总线接口支持IIS总线数据格式和MSB-justified数据格式。该接口对FIFO的访问采用了DMA模式取代了中断。它可以在同一时间接收和发送数据。

图1 结构框图

总线接口,寄存器组和状态机(BRFC):总线接口逻辑和FIFO 访问由状态机控制。

5 位双预定标器(IPSR):一个预定标器用于IIS 总线接口的主时钟发生器,另外一个用作外部编解码时钟发生器。

64 位FIFO(TxFIFO 和RxFIFO):在发送数据传输时,数据写到TxFIFO;在接收数据传输时,从RxFIFO 读取数据。

主IISCLK 发生器(SCLKG):在主设备模式,串行位时钟是从主时钟生成。

通道发生器和状态机(CHNC):IISCLK 和iislrck 是由通道状态机生成并控制。

15 位移位寄存器(SFTR):在发送模式下并行数据移位成串行数据输出,在接收模式下串行数据输入移位成并行数据。

二、发送接收模式

1.通常传输

IIS 控制寄存器对于发送接收FIFO 有一个FIFO 准备标志位。当FIFO 准备发送数据时,如果FIFO 非空,FIFO 准备标志位置1。如果FIFO 为空,FIFO 准备标志位置0。当接收FIFO非满,对于接收FIFO 的FIFO 准备标志位置1。其指出FIFO 准备好接收数据。如果接收FIFO 为满,FIFO 准备标志置0。这些标志用于决定CPU 读写FIFO 的时间。用这种方法当CUP 在访问发送接收FIFO 时,串行数据能被发送和接收。

2.DMA 传输

在此模式下,发送或接收FIFO 对DMA 控制器是可访问的。在发送或接收模式下的DMA服务请求是由FIFO 准备标志自动执行。

3.发送和接收模式

在此模式下IIS 总线接口可以同时接收和发送数据。

三、音频串行接口格式

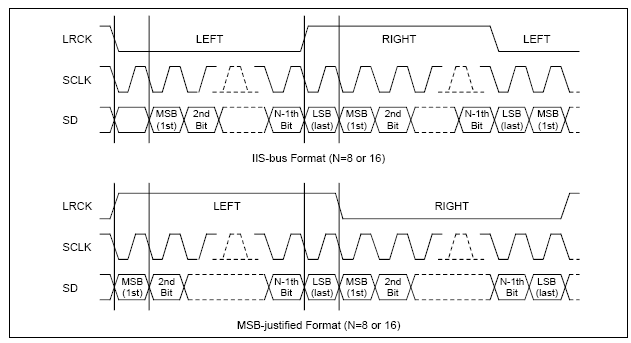

1.IIS 总线格式

IIS 总线有四线包括串行数据输入(IISDI),串行数据输出(IISDO),左右通道选择(IISLRCK)和串行位时钟(IISCLK)。生成IISLRCK 和IISCLK 的设备是主设备。串行数据以2 的补码发送,MSB(Most Significant Bit 最高位)先发。因为发送器和接收器可能有不同的字长,MSB(最高位)先发。发送器不必知道接收器可以处理多少位,接收器也不必知道会收到多少位。当系统字长大于发生器的字长,字为了数据发送而被截断(最低位被置0)。如果接收器接收大于其字长的位,在LSB(最低位)后的位被忽略。另外,如果接收器收到的位数小于其字长,缺少的位被置0。因此MSB 有一个固定的位置,而LSB 的位置取决于字长。只要IISLRCK 发送改变,发送器在一个时钟周期内发送下一个字的MSB。由发送器发送的串行数据可以和时钟信号的下降沿和上升沿同步。但是,串行数据必须在串行时钟信号的上升沿锁存到接收器。因此当同步上升沿的数据发送时有一些限制。左右通道选择线指出了正在发送的通道。IISLRCK 可以在串行时钟的下降沿或上升沿被改变,当时其不需要对称。在从设备,信号在串行时钟的下降沿或上升沿被锁存。在MSB 被发送,IISLRCK 线改变一个时钟周期。此允许发送器导出用于建立发送的串行数据同步时序。此外,其使能接收存储前一个字且为下一个字的接收清除输入。

2.MSB JUSTIFIED 格式

MSB JUSTIFIED 总线格式在结构上和IIS 总线格式。唯一和IIS 总线格式的区别,MSB JUSTIFIED 格式实现了只要IISLRCK 改变,发送器总是发送下一个字的MSB。

图2 IIS格式和MSB JUSTIFIED数据格式

四、IIS采集频率和主设备时钟

I2S主设备时钟频率可以通过采样频率来选择,这是因为I2S主设备时钟频率是由I2S分频器产生的(主设备时钟频率=PCLK/预分频器值),因此必须选择合适的预分频值和CODECLK的采样频率类型(256fs或384fs),才能获得合适的I2SLRCK频率(I2SLRCK频率=主设备时钟频率/CODECLK)。

串行位采用频率类型(16/32/48fs)可以通过配置信道的串行位数和CODECLK采样频率类型来完成(串行位时钟频率类型=CODECLK的采用类型/串行数据位数)。

五、IIS 总线接口特殊寄存器

I2S相关的寄存器包括I2S控制寄存器I2SCON、I2S模式寄存器I2SMOD、I2S分频寄存器I2SPSR、I2SFCON寄存器和FIFO寄存器。

1)I2SCON控制寄存器

I2SCON控制寄存器物理地址为0x55000000,可读/写,复位后值为0x100。寄存器各个比特位意义如下:

[8]左右声道标记,0=左声道,1=右声道;

[7]发送FIFO就绪标记,取0时表示没有就绪,取1时表示FIFO就绪;

[6]接收FIFO就绪标记,取0时表示没有就绪,取1时表示FIFO就绪;

[5]发送DMA请求使能,取0时请求禁止,取1时请求使能;

[4]接收DMA请求使能,取0时请求禁止,取1时请求使能;

[3]发送通道空闲命令,在空闲状态(暂停传输)时,I2SLRCK是不激活的,0表示I2SLRCK产生,1表示不产生;

[2]接收通道空闲命令,在空闲状态(暂停传输)时,I2SLRCK是不激活的,0表示I2SLRCK产生,1表示不产生;

[1]I2S预分频器使能,取0时预分频器禁止,取1时预分频器使能;

[0]I2S接口使能,取0时I2S禁止,取1时I2S使能。

2)I2SMOD模式寄存器

I2SMOD模式寄存器物理地址为0x55000004,可读/写,复位后值为0x000。寄存器各个比特位意义如下:

[8]主从模式选择,取0时为主模式,取1时为从模式;

[7:6]发送/接收模式选择,00=无,01=接收模式,10=发送模式,11=发送/接收模式;

[5]左右通道优先级,取0时右通道高左通道低,取1时右通道低左通道高;

[4]串行接口格式,取0时I2S兼容格式,取1时MSB可调格式;

[3]每通道串行数据位,取0时8位,取1时16位;

[2]主时钟频率选择,取0时主时钟是256fs(采样频率),取1时为384fs;

[1:0]串行位时钟频率选择,00=位时钟是16fs,01=位时钟是32fs,10=位时钟是48fs,11=未定义。

3)I2S分频寄存器I2SPSR

I2S分频寄存器物理地址为0x55000008,可读/写,复位后值为0x000。寄存器各个比特位意义如下:

[9:5]A预分频值,预分频器A的除因子,I2S总线接口主时钟=MCLK/A预分频因子;

[4:0]B预分频值,预分频器B的除因子,外部CODEC时钟=MCKL/B预分频因子。

4)I2SFCON寄存器

I2SFCON寄存器物理地址为0x5500000C,可读/写,复位后值为0x000。寄存器各个比特位意义如下:

[15]发送FIFO访问模式选择,取0时工作于普通模式,取1时工作在DMA模式;

[14]接收FIFO访问模式选择,取0时工作于普通模式,取1时工作在DMA模式;

[13]控制发送FIFO使能,取1时使能,取0时禁止;

[12]控制接收FIFO使能,取1时使能,取0时禁止;

[11:6]发送端FIFO数据计数,计数值0~32;

[5:0]接收端FIFO数据计数,计数值0~32。

5)FIFO寄存器I2SFIF

FIFO寄存器物理地址为0x55000010,可读/写,复位后值为0x000。寄存器各个比特位意义如下:I2S总线接口在发送/接收模式有两个64字节的FIFO,每个FIFO由宽16、深32的表组成,并且每个FIFO单元可以分别操作高字节或低字节。通过FIFO入口访问发送和接收FIFO,入口地址为0x55000010。

上一篇:s3c2440之IIS(2)I2S音频总线学习-数字音频技术

下一篇:S3C2440之IIS配置

推荐阅读最新更新时间:2024-11-16 23:27

设计资源 培训 开发板 精华推荐

- 【训练营】仿生机器狗

- LTC3541 的典型应用 - 高效率降压 + VLDO 稳压器

- OM13090: LPC54114音频和语音识别套件

- LT8607IMSE 5V、2MHz 降压型稳压器的典型应用电路

- 【训练营】一只狗腿子

- 使用 ColdFire MCF5208 拆分总线架构的系统设计,适用于 3.3V、32 位 SDR SDRAM 系统

- 使用 NXP Semiconductors 的 NE5580N 的参考设计

- RT5796A 1.5A、1MHz、5.5V CMCOT同步降压转换器典型应用

- IS31FL3216-QFLS2-EB,基于 IS31FL3216 16 通道 LED 驱动器的评估板

- 感测输出电流应用电路

西门子PLC从入门到精通彩图版 (杨锐)

西门子PLC从入门到精通彩图版 (杨锐) 西门子S7-1200-PLC编程及应用教程(第3版) (侍寿永 主编)

西门子S7-1200-PLC编程及应用教程(第3版) (侍寿永 主编) ESP32-S3源代码

ESP32-S3源代码 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号