参考电流

输出电流是通过设定流入外部电阻器的参考电流来设定的。如图1所示,内部子电路提供外部电阻600 mV的偏置电压。IREF引脚上的电压通过连接到NMOS M3的运算放大器U1和根据精确内置带隙电压基准产生的600 mV参考电压进行调节。流经外部电阻器R2的电流通过PMOS M1 & M2产生镜像,在硅片级调整M1/M2大小,获取1:10的比例。如此,M1流过1mA时,M2漏极可产生10mA。

电流流经NMOS M4/M5产生的电流镜像,这两个器件的净比例为1:25,此时10mA可在M5漏极产生250mA电流。由于外部LED连接到该漏极,因而流入LED的电流即为漏极电流,且该值仅与外部电阻器设定的参考电流和M1/M5总比率的乘积有关。

显然,子电路设计用于支持应用中需要的参考电流水平。由于每个LED最大负载电流为25 mA,参考电流最大值为100mA。如果外部电阻器下降到5.2 kΩ以下,参考电流将下降,且LED电流不能进一步增大,参见NCP5604数据表中的公差。

上电次序

假设芯片连接到适当的电源(置Vbat最小值为3V,最大值为5.5 V),启动引脚设置为高时,内置系统被启动,参见图2。此时,外部储能电容充电完成前,LED无电流流过,Vout电压必须高于正向电流产生前的LED Vf。另一方面,有意限制电池的启动输入电流,储能电容上电压的上升时间同样受到限制,而启动LED需要200ms。当然,对肉眼来说,200ms极快,同时对最终用户来说,该照明转瞬即逝。

另一方面,若LED关断,或正向电流关闭,储能电容缓慢放电:转换器不会从零重新启动,无需200ms也可达到LED Vf。

渐进启动/停止过程

基本概念是当启用信号设置为高或低时,逐渐打开/关闭LED,而不使用MCU端口上额外的输入/输出引脚。由于芯片未集成可编程寄存器,不可能用纯数字的方法提供该功能。替代方法是采用连接内置参考电流的模拟结构以控制LED电流。

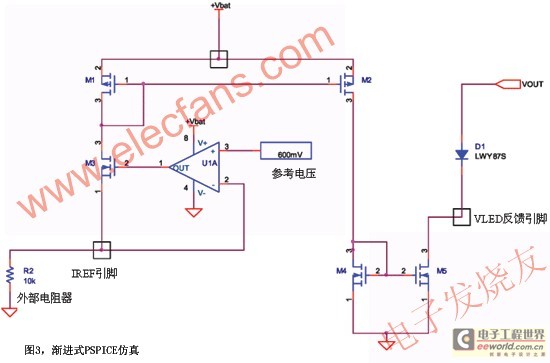

可以用伪镜像结构中的NPN晶体管开发简单的应用,强制参考电流按照如图3的PSPICE模型所示流入IREF引脚。电流镜像代表NCP5604电路,渐进功能用晶体管Q1和相连网络实现。电阻R2形成最大参考电流,从而实现LED最大正向电流流入。基本上,启动信号用于对连接在晶体管Q1基极/接地之间的电容C1进行指数式充电。一旦电压达到晶体管Vbe时,集电极电流流过,强制参考电流斜率根据R1/C1网络达到所需的时间。最后,Q1集电极电压受NCP5604提供的恒定电压钳制,参考电流为(Vref-Vcesat)/R2。一般来说,集电极/发射极压降较小(范围是50 mV),在无高精度要求的应用中可以忽略。

但是,计算外部电阻器时将其纳入考虑范围可适当补偿这种压降。PSPICE模型捕捉的波形展示了这种电路特性(图4)。

可以看到,关闭时的曲线比打开时平缓,原因是两个时间段的参考电压有很大不同。尽管这并非关键性问题,但一些应用可能需要更对称的时序,可以将额外电阻连接到小信号二极管来实现。图6根据图5 PSPICE基本电路图给出了波形,说明了通过接入D2和R8可以实现的性能。

典型应用如图7所示,时序可以调整,以便应对不同的状态。任何情况下,延迟电容(图7电路图中的C5)必须为陶瓷型,以减小漏电流,低成本的电解电容不适合在这应用。如前所述,无需MCU的额外输入/输出即可激发渐进时序,启动信号即可实现两种功能。

另一方面,电流参考电阻(图7电路图中的R3)减小到5.6 kΩ时,可补偿晶体管Q1的Vcesat。

图8、图9中的波形说明了采用Rb=1.3 MΩ/Cbe=2.2mF产生软启动时,输出至4个LED的电流均为25 mA。当然,通过调整Rb/Cbe网络可以增加或减小斜升延迟。但1.5 MΩ以上的Rb值将造成系统对环境噪声敏感。如前所述,Cbe电容不可采用低成本电解电容,必须采用陶瓷型电容,以实现所期望的长时序。

可以采用小信号NMOS器件替代外部晶体管Q1,如BSS138。由于门极输入不吸收电流,可以产生更大时延。虽然还可以采用更小的器件运行这种应用,但必须避免所选NMOS的大Rdson造成的非受控工作电流。实际上,对于Rdson额定值为5000Ω的器件,上述参数变化较大(在整个温度范围内大概为1:2),且输出电流同时变化,使得LED亮度不均匀。因此,必须选择Rdson较小的器件,以确保LED在正常工作中可准确控制。

另外,由于NMOS的Vt大于双极型器件Vbe的两倍,采用NMOS器件一般不会在开始时序上增加工作延迟:Vbe为0.6 V时,范围在1.5 V。图10和图11中的PSPICE波形解释了这种状态。设计人员可选择适当的器件类型,实现这种功能。

图7所示的电路图按照软启动观点的预期进行工作,但由于EN为低时,启动信号关闭直流/直流转换器,停止时序突然缩短,造成其它停止时序不相关。为避免形成这样的机制,当停止时序为关键问题时,应采用额外无源网络。图12中的电路图说明了将R/C/D网络连接到EN引脚方面的改进。

当启动信号升高时,二极管D1对电容C5快速充电,并且在EN引脚上产生一个可以忽略的延迟。但启动信号降低时,情况有所不同:此时与电容C5相连的电阻R2产生一个延迟,使直流/直流转换器保持足够长时间的工作,在关闭过程中产生渐进的调光。如果EN引脚永久连接到高(可能为Vbat),将NMOS用作

启动/关闭系统,或者如图13和图14所示,提供一个额外控制NMOS的引脚,便获得更精确的时序设定。

上一篇:固态非易失性电位器X9312在频率可调信号源中的应

下一篇:三相SPWM在变频器中的实现方法

- 热门资源推荐

- 热门放大器推荐

- NXP 2.5亿美元收购Aviva,但车载SerDes领域依然处于战国时期

- 应对 AI 时代的云工作负载,开发者正加速向 Arm 架构迁移

- 沉浸式体验漫威宇宙,英特尔锐炫显卡为《漫威争锋》提供Day 0支持

- 艾迈斯欧司朗与法雷奥携手革新车辆内饰,打造动态舱内环境

- 《嵌入式-STM32开发指南》第二部分 基础篇 - 第7章DMA(HAL库)

- 【“源”察秋毫系列】DC-DC电源效率测试,确保高效能与可靠性的关键步骤

- NVIDIA 推出高性价比的生成式 AI 超级计算机

- Mapbox与Arm合作推出虚拟主机 加速软件定义汽车导航

- 移植tslib和Qt5.6到三星s5pv210开发板

- 智能座舱新赛点在哪? 看这四款重磅新车

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 MAAPSS0104TR-1000

MAAPSS0104TR-1000

京公网安备 11010802033920号

京公网安备 11010802033920号