1 引言

随着Internet 的出现和以太网的迅速发展, 基于以太网的设备控制越来越多。目前市场上大部分以太网控制器采用的封装均超过80 引脚, 如RTL8019AS、DM9008、CS8900A 等。这些器件不仅结构复杂, 面积庞大, 且系统开销较大。近来, Microchip推出全球首枚28 引脚独立以太网控制器ENC28J60, 可为嵌入式系统提供低引脚数、低成本、精简的远程通讯解决方案。

设计了以ENC28J60 为核心的以太网接口实现方案, 描述了该系统硬件架构的设计方法。在简要介绍了以太网控制器ENC28J60 的结构、功能、外围电路的基础上, 对ENC28J60 与Atmega16 的SPI 通讯进行了阐述。此方案不仅成本低, 而且可以实现500Kbps 以上的传输速率, 满足了嵌入式系统的Internet 控制要求。

2 ENC28J60 网络接口体系结构

ENC28J60 是带有行业标准串行外设接口(Serial PeripheralInterface, SPI)的独立以太网控制器。它符合IEEE 802.3 的全部规范, 采用了一系列包过滤机制以对传入数据包进行限制。它还提供了一个内部DMA 模块, 以实现快速数据吞吐和硬件支持的IP 校验和计算。与主控制器的通信通过两个中断引脚(INT和WOL)和SPI 脚(SO、SI、SCK、CS)实现, 数据传输速率高达10Mb/s.两个专用的引脚(LEDA、LEDB)用于连接LED, 进行网络活动状态指示。图1 所示为ENC28J60 的典型应用电路。

ENC28J60 由7 个主要功能模块组成:SPI 接口, 充当主控制器和ENC28J60 之间通信通道; 控制寄存器, 用于控制和监视ENC28J60; 双端口RAM缓冲器, 用于接收和发送数据包; 判优器, 当DMA、发送和接收模块发出请求时对RAM缓冲器的访问进行控制; 总线接口, 对通过SPI 接收的数据和命令进行解析;MAC 模块:实现符合IEEE 802.3 标准的MAC 逻辑; PHY 模块, 对双绞线上的模拟数据进行编码和译码。ENC28J60 还包括其他支持模块, 诸如振荡器、片内稳压器、电平变换器(提供可以接受5V 电压的I/O 引脚)和系统控制逻辑。

根据以上说明, ENC28J60 应用于嵌入式网络接口是非常合适的, 有广阔的应用发展前景。

3 ENC28J60 在嵌入式网络接口的应用

3.1 硬件电路设计

利用ENC28J60 可以构成不同功能的网络终端节点, 如网络服务器、带Internet 功能的设备、远程监控(数据采集, 诊断)设备等。图2 所示为基于ENC28J60 的嵌入式网络接口的硬件电路原理图。电路中有:2 个LED 状态指示灯主要用来显示网络连接状态, 包括PHY 是否冲突、连接是否建立、是否接收数据、连接速度、双工模式等; 必需的偏置电阻R3(2kΩ, 精度为1%);高速局域网电磁隔离模块(即RJ45 以太网接口), 应用中,ENC28J60 的物理端口与隔离变压器HR901170A 连接时必须符合IEEE802.3 对物理层规范的要求, 如RJ45 的插孔与隔离变压器的间隔应尽量小, 输出和输入差分信号对的走线要有很好的隔离。

电路中的主控制器采用Atmel 公司的ATmega16 单片机,它具有先进的RISC(精简指令集计算机)结构、16 kB 可编程Flash 存储器、512 B 的EEPROM和1 kB 片内SRAM, 具有丰富的外设接口, 其SPI 接口允许ATmega16 与外设进行高速的同步数据传输。本设计中ATmega16 SPI 配置为主机模式,ENC28J60 为从设备。ATmega16 的SPI 工作模式由CPOL、CPHA 设置, 根据ENC28J60 的SPI 读写时序, ATmega16 的SPI工作模式应设置为模式0.ATmega16 通过将ENC28J60 的CS引脚置低实现与其的同步。SPI 时钟由写入到SPI 发送缓冲寄存器的数据启动, SPI MOSI(PB5)引脚上的数据发送秩序由寄存器SPCR 的DORD 位控制, 置位时数据的LSB(最低位)首先发送, 否则数据的MSB(最高位)首先发送。我们选择先发送MSB,同时接收到的数据传送到接收缓冲寄存器, CPU 进行右对齐从接收缓冲器中读取接收到的数据。应该注意, 当需要从ENC28J60 中读取多个数据时, 即使ENC28J60 并不需要ATmega16 串行输出的数据, 每读取一个数据前都要向SPI 发送缓冲器写一个数据以启动SPI 接口时钟。由于SPI 系统的发送方向只有1 个缓冲器, 而在接收方向有2 个缓冲器, 所以在发送时一定要等到移位过程全部结束后, 才能对SPI 数据寄存器执行写操作; 而在接收数据时, 需要在下一个字节移位过程结束之前通过访问SPI 数据寄存器读取当前接收到的数据, 否则第1 个数据丢失。

3.2 ENC28J60 软件初始化

在使用ENC28J60 发送和接收数据包前, 必须对器件进行初始化设置。根据不同的应用, 一些配置选项可能需要更改。初始化设置工作包括接收和发送缓冲器、接收过滤器、晶振启动时间、MAC 寄存器、PHY 寄存器。初始化芯片之前先关闭单片机的中断输入, 对RESET 引脚给定一个持续的低电平复位信号, 然后对相应的寄存器进行设置。设置完成所有需要的寄存器后, 判断以太网状态中的时钟启动标志位是否置位, 然后开中断。

系统初始化后进入主程序循环, 包括单片机的控制作用和网络数据传输。对于以太网传输部分来说。主要有两个作用:一是对要发送的数据按照以太网数据帧格式进行封装并发送; 二是对接收的以太网数据帧进行解包, 供应用程序使用。

3.3 ENC28J60 发送数据包

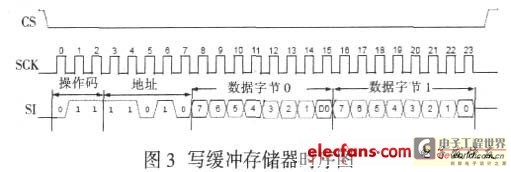

在进行数据包发送或接收时, 要先对写缓冲存储器(WriteBuffer Memory, WBM)命令掌握。WBM允许主控制器将字节写入8KB 发送和接收缓冲存储器。如果ECON2 寄存器中的AUTOINC 位置1, 那么在写完每个字节的最后一位之后,EWRPT 指针将会自动地递增指向下一个地址(当前地址加1)。

如果写入地址1FFF 且AUTOINC 置1, 则写指针加1 指向0000h.将CS 引脚拉为低电平启动WBM命令。然后将WBM操作码及随后的5 位常量1Ah 送入ENC28J60.在发送WBM命令和常量之后, 由EWRPT 指向的存储器中的数据将移入ENC28J60, 首先移入最高位。在接收到8 个数据位后, 如果AUTOINC 置1, 写指针将自动递增。主控制器可以继续在SCK引脚提供时种信号、在SI 引脚发送数据同时保持/CS 为低电平, 从而可以连续写入存储器。当AUTOINC 被使能时, 以该方式就可以连续地向缓冲存储器写入字节而无需多余的SPI命令。拉高CS 引脚电平可结束WBM命令。在WBM操作期间,SO 引脚一直为高阻态, WBM操作时序, 请参见图3.

ENC28J60 内的MAC 在发送时会自动生成前导符和帧起始定界符。此外, MAC 可根据配置生成填充(如果需要)和CRC字段。主控制器必须生成所有其他帧字段, 并将它们写入缓冲存储器, 以待发送。此外, ENC28J60 还要求在待发送的数据包前添加一个包控制字节。主控制器应:1.正确编程ETXST 指针,使之指向存储器中未用的单元。它将指向包控制字节, 在本设计方案中, 指针应编程为0120h; 2.使用WBM SPI 命令写入包控制字节、目标地址、源MAC 地址、类型/ 长度和数据有效负载; 3.正确编程ETXND 指针。它应指向数据有效负载的最后一个字节, 在本设计方案中, 指针应编程为0156h; 4.将EIR.TXIF位清零、将EIE.TXIE 位和EIE.INTIE 位置1 允许在发送完成后产生中断(如果需要); 5.将ECON1.TXRTS 位置1 开始发送。如果在TXRTS 位置1 时正在进行DMA 操作, ENC28J60 会等待DMA 操作完成再发送。这种等待是必需的, 因为DMA 和发送引擎共享同一个存储器访问端口。同样如果在TXRTS 已置1后, ECON1 中DMAST 位才置1, DMA 在TXRTS 位清零前不会采取任何动作。如果正在进行发送, 不应通过SPI 读取或写入任何待发送的字节。主控制器将TXRTS 位清零可取消发送。如果数据包发送完成或因错误取消而中止发送, ECON1.TXRTS位会被清零, 一个7 字节的发送状态向量将被写入由ETXND +1 指向的单元, EIR.TXIF 会被置1 并产生中断(如果允许)。要验证数据包是否成功发送, 应读取ESTAT.TXABRT 位。如果该位置1, 主控制器在查询发送状态向量的各个字段外, 还应查询ESTAT.LATECOL 位, 以确定失败的原因。下面给出写数据包的源代码:

3.3 ENC28J60 接收数据包

假设接收缓冲器已完成初始化, MAC 已正确配置而且接收过滤器已配置为接收以太网数据包, 主控制器应该:1.如果需要在接收到数据包时产生一个中断, 就要将EIE.PKTIE 位和EIE.INTIE位置1; 2. 如果需要在由于缓冲空间不足导致数据包丢失时产生一个中断, 就要将EIR.RXERIF 位清零, 并将EIE.RXERIE位和EIE.INTIE 位置1; 3. 通过将ECON1.RXEN 位置1使能接收。在将RXEN 置1 后, 将不能修改双工模式和接收缓冲器起始和结束指针。此外, 要阻止不期望接收的数据包, 在更改接收过滤器配置寄存器(ERXFCON) 和MAC 地址前建议将RXEN 清零。在使能接收后, 没有过滤掉的数据包将写入循环接收缓冲器。任何不符合过滤条件的数据包将被丢弃, 但主控制器无法识别一个数据包已被丢弃。当接收到一个数据包并将其完整写入缓冲器时, EPKTCNT 寄存器将递增, EIR.PKTIF 位将置1, 并产生一个中断(如果允许), 同时硬件写指针ERXWRPT 自动递增。

4 结束语

本文作者的创新点: 通过ENC28J60 芯片所设计的嵌入式网络接口可以在多种环境中应用, 能按需要进行配置来完成系统功能,并且在成本、体积、功耗、灵活性等方面具有明显的优势,能为智能化仪器与设备、信息家电等开拓新的应用前景。

上一篇:经典案例分享:两种键盘扫描方法比较分析

下一篇:嵌入式系统结构与协同性探讨

推荐阅读最新更新时间:2023-10-12 20:40

嵌入式C编程与Atmel AVR_(美国)

嵌入式C编程与Atmel AVR_(美国) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号