摘要:ADuC845是ADI公司新推出的嵌有单指令周期8052闪存MCU、带两路24位Δ-∑A/D、双12位D/A以及两个灵活脉宽调制输出的高性能24位数据采集与处理系统芯片。该芯片的数据处理速度达12MIPS,且设计简单,噪声低,非常适用于精密仪器仪表。文中详细介绍了该芯片的功能特点和工作原理,给出该芯片的应用方法。

关键词:ADuC845 数据采集 转换器 存储器

1 概述

ADuC845是ADI公司新推出的高性能24位数据采集与处理系统,它内部集成有两个高分辨率的Δ-∑ADC、10/8通道输入多路复用器、一个8位MCU和程序/数据闪速/电擦除存储器。同时可提供62k字节的闪速/电擦除程序存储器,4k字节闪速/电擦除数据存储器和2304字节的数据RAM。

ADuC845可通过一个片内锁存环PLL产生一个12.58MHz的高频时钟,以使之运行于32kHz外部晶振。该时钟可通过一个从MCU核心时钟工作频率分离的可编程时钟发送。片内微控制器是一个优化的单指令周期8052闪存MCU。该MCU在保持与8051指令系统兼容的同时,具有12.58MIPS的性能。该芯片的两个独立的ADC(主ADC和辅助ADC)由一个输入多路复用器,一个温度传感器和一个可直接测量低幅度信号的可编程增益放大器PGA组成。主、辅ADC都采用高频“斩波”技术来提供优良的直流(DC)失调和失调漂移指标,因而非常适合用于低温漂且对噪声抑制和抗电磁干扰能力要求较高的应用场合。

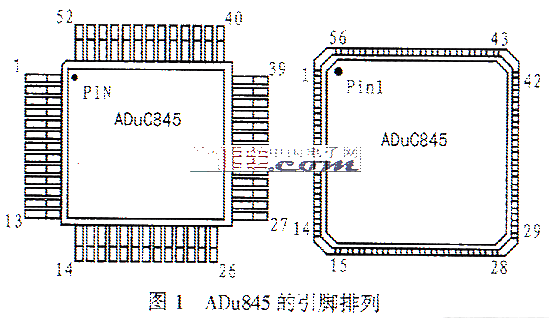

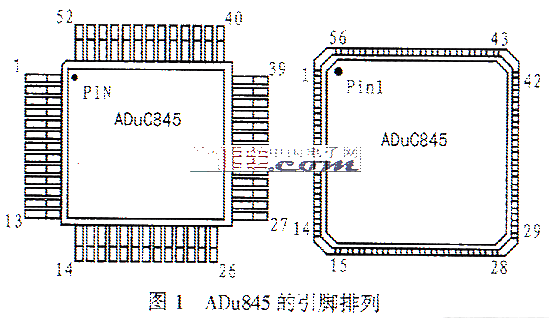

ADuC845具有串行下载和调度模式,可通过EA引脚提供引脚竞争模式,同时支持Quick Start开发系统和低成本的软件和硬件工具。该芯片具有52引脚塑料四方扁平封装(MQFP)和56引脚芯片级封装(CSP)。

2 ADuC845的性能特点

2.1 高分辨率Δ-∑ADC

*带有2个独立的10通道、24位模/数转换器(ADC);

*24位无失码主ADC;

*在60Hz范围内有20位有效分辨率(17.4位峰-峰分辨率);

*芯片的失调漂移为10nV/℃,增益漂移为0.5ppm/℃。

2.2 存储器

*62k字节片内闪速/电擦除程序存储器;

*4k字节片内闪速/电擦除数据存储器;

*闪速/电擦除存储器可使用100年,可重复擦写10万次;

*有3种闪速/电擦除程序存储器安全模式;

*在线串行下载(无需外部硬件);

*带有高速用户下载(5秒)功能;

*带有2304字节片内数据RAM。

2.3 基于8051的内核

*具有与8051兼容的指令系统;

*高性能单指令周期内核;

*可使用32kHz外部晶振;

*具有片内可编程锁相环PLL(最高时钟频率12.58MHz);

*有3个16位定时/计数器;

*有26条可编程输入/输出线;

*11个中断源,2个优先级;

*双数据指针,扩展的11位堆栈指针。

2.4 片内外围设备

*内部电源复位电路;

*12位电压输出DAC;

*双16位Δ-∑DAC/PWM;

*片内温度传感器;

*双激励电流源;

*时间间隔计数器(唤醒/RTC定时器);

*UART,I2C和SPI串行接口;

*高速波特率发生器(包括115,200);

*看门狗定时器(WDT);

*电源监视器(PSM)。

2.5 电源

*可用3V和5V电压工作;

*正常情况下为2.3mA/3.6V(核心时钟频率为1.57MHz);

*掉电保持电流为20μA,可唤桓定时运行。

3 ADuC845的引脚功能

ADuC845的引脚排列如图1所示,其中采用56引脚封装的管脚功能如下:

56脚(P1.0/AIN1):上电缺省设置为AIN1模拟输入。使用AINCON时,AIN1用作伪差分输入;使用AIN2时,该脚用作全差分对的正向输入。P1.0端口无数输出驱动器。为把其配置为数字输入,应把0写至端口值。作数字输入时,该引脚必须由外部驱动到高电平或低电平。

1脚(P1.1/AIN2):上电缺省设置为AIN2模拟输入。使用AINCON时,AIN2用作伪差分输入;使用AIN1时,用作全差分对的负向输入。输入同P1.0。

2脚(P1.2/AIN3/REFIN2+):上电缺省设置为AIN3模拟输入。使用AINCOM时,AIN3用作伪差分输入;使用AIN4时,用作全差分对的正向输入。数字输入同P1.0。另外,该引脚亦可用作第二个外部差分参考输入的正向输入端。

3脚(P1.3/AIN4/REFIN2-):上电缺省设置为AIN4模拟输入。使用AINCOM时,AIN4用作伪差分输入;使用AIN3时,用作全差分对的负向输入。数字输入同P1.0。另外,该引脚亦可用作第二个外部差分参考输入的负向输入端。

4脚(AVDD):模拟电源。

5,6脚(AGND):模拟地。

7脚(REFIN-):外部差分参考输入的负向输入端。

8脚(REFIN+):外部差分参考输入的正向输入端。

9脚(P1.4/AIN5):上电缺省设置为AIN5模拟输入。使用AINCOM时,AIN5用作伪差分输入;使用AIN6时,用作全差分对的正向输入。输入同P1.0。

10脚(P1.5/AIN6):上电缺省设置为AIN6模拟输入。使用AINCOM时,AIN6用作伪差分输入;使用AIN5时,用作差分对的负向输入。输入同P1.0。

11脚(P1.6/AIN7/IEXC1):上电缺省设置为AIN7模拟输入。使用AINCOM时,AIN7用作伪差分输入;使用AIN8时,用作全差分对的正向输入。该引脚可配置1"2个电流源。数字输入同P1.0。

12脚(P1.7/AIN8/IEXC2):上电缺省设置为AIN8模拟输入。使用AINCOM时,AIN8用作伪差分输入;使用AIN7时,用作全差分对的负向输入。该引脚可配置1"2个电流源。数字输入同P1.0。

13脚(AINCOM/DAC):若选定相关的伪差分输入,则所有的模拟输入必须参考此引脚。该引脚亦可作为DAC的输出引脚之一。

14脚(DAC):若DAC使能,则该引脚输出DAC电压。

15脚(AIN9):使用AINCOM时,AIN9用作伪差分输入;使用AIN10时,用作全差分对的正向输入。

16脚(AIN10):使用AINCOM时,AIN10用作伪差分输入;使用AIN9时,用作全差分对的负向输入。

17脚(RESET):复位输入。当振荡器运行时,该引脚上长达16个主时钟周期的高电平半使器件复位。

18"21,24"27脚(P3.0"P3.7):P3口是具有内部上拉电阻的双向口。当写1的端口3被内部上拉至高电平时,它们可用作输入。由于有内部上拉电阻,被外部拉至低电平的端口3引脚将提供电流。当驱动一个0-1的输出转换时,上拉功能将被激活并持续2个内部时钟周期的指令循环。

18脚(P3.0/RED):UART串行口接收数据。

19脚(P3.1/TXD):UART串行口发送数据。

20脚(P3.2/INT0):外部中断0,此引脚也可用作选通门,控制定时器0的输入。

21脚(P3.3/INT1):外部中断0,此引脚也可用作选通门,控制定时器1的输入。

24脚(P3.4/T0):定时器/计数器0输入。

25脚(P3.5/T1):定时器/计数器1输入。

26脚(P3.6/WR):写控制信号。把来自P0口的数据字节锁存入外部数据存储器。

27脚(P3.7/RD):读控制信号。将外部数据存储器中的数据读到P0口。

22,36,51脚(DVDD):数字电源。

23,37,38脚(DGND):数字地。

28脚(SCLK):I2C串行接口时钟。作输入口使用时,除输出逻辑低电平外,该引脚为施密特触发输入,且存在一个弱的内部上拉。此引脚亦可作为数字输出口使用,通常由软件控制。

29脚(SDATA):I2C串行数据输入口。作为输入口时,该引脚有一个弱的内部上拉出现,除非它输出逻辑低电平。

30"33,39"42(P2.0"P2.7):P2口是具有内部上拉电阻的双向口。当写1的端口2被内部上拉电阻拉至高电平时,这些引脚可用作输入。由于内部上拉电阻,被外部拉至低电平的端口2引脚将提供电流。在访问24位外部数据存储器空间的过程中P2口发出中和高地址字节。

30脚(P2.0/SCLOCK):SPI串行接口时钟。作输入口使用时,除输出逻辑低电平外,该引脚为施密特触发输入,且存在一个弱的内部上拉。

31脚(P2.1/MOSI):用于SPI接口的SPI主输出/从输入数据I/O引脚。

32脚(P2.3/SS/T2):SPI接口的从属选择输入,该引脚有一个弱的上拉作用。该引脚能给定时器2提供时钟输入,此项功能启动时,计数器2增加坟数以响应T2输入引脚出现的负跳变。

39脚(P2.4/T2EX):用于向定时器2提供控制输入。此项功能启动时,此引脚上出现的负跳变将使定时器2捕获或重载。

40脚(P2.5/PWM0):若PWM使能,则该引脚输出PWM0。

41脚(P2.6/PWM1):若PWM使能,则该引脚输出PWM1。

42脚(P2.7/PWMCLK):若PWM使能,则该引脚提供外部PWM时钟。

34脚(XTAL1):晶振反相器输入。

35脚(XTAL2):晶振反相器输出。

43脚(EA):外部访问使能,逻辑输入。当保持高电平时,此输入使能器件从地址为0000H"F7FFH的内部程序存储器内取回代码。ADuC845无外部程序存储器访问功能。为了确定代码执行模式,该引脚在外部复位结束时起作用,或将其作为器件电源周期的一部分。

44脚(PSEN):程序存储使能引脚,逻辑输出。除了在外部数据存储访问期间外,该脚每6个时钟周期有效一次。而在内部程序执行期间,此引脚保持高电平。当该引脚通过上电复位电阻或作为器件电源周期的一部分被拉至低电平时,PSEN引脚也可用作使能下载模式。

45脚(ALE):地址锁存使能,逻辑输出。在外部存储器访问期间,此输出用于把地址的低字节(适于24位数据地址空间访问的页字节)锁存在外部存储器。除了在外部数据存储器访问期间,它每6个时钟周期被激活一次。通过设置PCON SFR的PCON.4位,可禁止此引脚工作。

46"49,52"55脚(P0.0"P0.7):P0口是8位漏极开路双向I/O端口。写1的端口0引脚悬空,在此状态下可用作高阻抗输入。驱动外部逻辑高电平时,需在此端口接一个外部上拉电阻。在访问外部程序和数据存储器期间,P0口也是多路复用的低位地址和数据总线。

2 ADuC845的性能特点

2.1 高分辨率Δ-∑ADC

*带有2个独立的10通道、24位模/数转换器(ADC);

*24位无失码主ADC;

*在60Hz范围内有20位有效分辨率(17.4位峰-峰分辨率);

*芯片的失调漂移为10nV/℃,增益漂移为0.5ppm/℃。

2.2 存储器

*62k字节片内闪速/电擦除程序存储器;

*4k字节片内闪速/电擦除数据存储器;

*闪速/电擦除存储器可使用100年,可重复擦写10万次;

*有3种闪速/电擦除程序存储器安全模式;

*在线串行下载(无需外部硬件);

*带有高速用户下载(5秒)功能;

*带有2304字节片内数据RAM。

2.3 基于8051的内核

*具有与8051兼容的指令系统;

*高性能单指令周期内核;

*可使用32kHz外部晶振;

*具有片内可编程锁相环PLL(最高时钟频率12.58MHz);

*有3个16位定时/计数器;

*有26条可编程输入/输出线;

*11个中断源,2个优先级;

*双数据指针,扩展的11位堆栈指针。

2.4 片内外围设备

*内部电源复位电路;

*12位电压输出DAC;

*双16位Δ-∑DAC/PWM;

*片内温度传感器;

*双激励电流源;

*时间间隔计数器(唤醒/RTC定时器);

*UART,I2C和SPI串行接口;

*高速波特率发生器(包括115,200);

*看门狗定时器(WDT);

*电源监视器(PSM)。

2.5 电源

*可用3V和5V电压工作;

*正常情况下为2.3mA/3.6V(核心时钟频率为1.57MHz);

*掉电保持电流为20μA,可唤桓定时运行。

3 ADuC845的引脚功能

ADuC845的引脚排列如图1所示,其中采用56引脚封装的管脚功能如下:

56脚(P1.0/AIN1):上电缺省设置为AIN1模拟输入。使用AINCON时,AIN1用作伪差分输入;使用AIN2时,该脚用作全差分对的正向输入。P1.0端口无数输出驱动器。为把其配置为数字输入,应把0写至端口值。作数字输入时,该引脚必须由外部驱动到高电平或低电平。

1脚(P1.1/AIN2):上电缺省设置为AIN2模拟输入。使用AINCON时,AIN2用作伪差分输入;使用AIN1时,用作全差分对的负向输入。输入同P1.0。

2脚(P1.2/AIN3/REFIN2+):上电缺省设置为AIN3模拟输入。使用AINCOM时,AIN3用作伪差分输入;使用AIN4时,用作全差分对的正向输入。数字输入同P1.0。另外,该引脚亦可用作第二个外部差分参考输入的正向输入端。

3脚(P1.3/AIN4/REFIN2-):上电缺省设置为AIN4模拟输入。使用AINCOM时,AIN4用作伪差分输入;使用AIN3时,用作全差分对的负向输入。数字输入同P1.0。另外,该引脚亦可用作第二个外部差分参考输入的负向输入端。

4脚(AVDD):模拟电源。

5,6脚(AGND):模拟地。

7脚(REFIN-):外部差分参考输入的负向输入端。

8脚(REFIN+):外部差分参考输入的正向输入端。

9脚(P1.4/AIN5):上电缺省设置为AIN5模拟输入。使用AINCOM时,AIN5用作伪差分输入;使用AIN6时,用作全差分对的正向输入。输入同P1.0。

10脚(P1.5/AIN6):上电缺省设置为AIN6模拟输入。使用AINCOM时,AIN6用作伪差分输入;使用AIN5时,用作差分对的负向输入。输入同P1.0。

11脚(P1.6/AIN7/IEXC1):上电缺省设置为AIN7模拟输入。使用AINCOM时,AIN7用作伪差分输入;使用AIN8时,用作全差分对的正向输入。该引脚可配置1"2个电流源。数字输入同P1.0。

12脚(P1.7/AIN8/IEXC2):上电缺省设置为AIN8模拟输入。使用AINCOM时,AIN8用作伪差分输入;使用AIN7时,用作全差分对的负向输入。该引脚可配置1"2个电流源。数字输入同P1.0。

13脚(AINCOM/DAC):若选定相关的伪差分输入,则所有的模拟输入必须参考此引脚。该引脚亦可作为DAC的输出引脚之一。

14脚(DAC):若DAC使能,则该引脚输出DAC电压。

15脚(AIN9):使用AINCOM时,AIN9用作伪差分输入;使用AIN10时,用作全差分对的正向输入。

16脚(AIN10):使用AINCOM时,AIN10用作伪差分输入;使用AIN9时,用作全差分对的负向输入。

17脚(RESET):复位输入。当振荡器运行时,该引脚上长达16个主时钟周期的高电平半使器件复位。

18"21,24"27脚(P3.0"P3.7):P3口是具有内部上拉电阻的双向口。当写1的端口3被内部上拉至高电平时,它们可用作输入。由于有内部上拉电阻,被外部拉至低电平的端口3引脚将提供电流。当驱动一个0-1的输出转换时,上拉功能将被激活并持续2个内部时钟周期的指令循环。

18脚(P3.0/RED):UART串行口接收数据。

19脚(P3.1/TXD):UART串行口发送数据。

20脚(P3.2/INT0):外部中断0,此引脚也可用作选通门,控制定时器0的输入。

21脚(P3.3/INT1):外部中断0,此引脚也可用作选通门,控制定时器1的输入。

24脚(P3.4/T0):定时器/计数器0输入。

25脚(P3.5/T1):定时器/计数器1输入。

26脚(P3.6/WR):写控制信号。把来自P0口的数据字节锁存入外部数据存储器。

27脚(P3.7/RD):读控制信号。将外部数据存储器中的数据读到P0口。

22,36,51脚(DVDD):数字电源。

23,37,38脚(DGND):数字地。

28脚(SCLK):I2C串行接口时钟。作输入口使用时,除输出逻辑低电平外,该引脚为施密特触发输入,且存在一个弱的内部上拉。此引脚亦可作为数字输出口使用,通常由软件控制。

29脚(SDATA):I2C串行数据输入口。作为输入口时,该引脚有一个弱的内部上拉出现,除非它输出逻辑低电平。

30"33,39"42(P2.0"P2.7):P2口是具有内部上拉电阻的双向口。当写1的端口2被内部上拉电阻拉至高电平时,这些引脚可用作输入。由于内部上拉电阻,被外部拉至低电平的端口2引脚将提供电流。在访问24位外部数据存储器空间的过程中P2口发出中和高地址字节。

30脚(P2.0/SCLOCK):SPI串行接口时钟。作输入口使用时,除输出逻辑低电平外,该引脚为施密特触发输入,且存在一个弱的内部上拉。

31脚(P2.1/MOSI):用于SPI接口的SPI主输出/从输入数据I/O引脚。

32脚(P2.3/SS/T2):SPI接口的从属选择输入,该引脚有一个弱的上拉作用。该引脚能给定时器2提供时钟输入,此项功能启动时,计数器2增加坟数以响应T2输入引脚出现的负跳变。

39脚(P2.4/T2EX):用于向定时器2提供控制输入。此项功能启动时,此引脚上出现的负跳变将使定时器2捕获或重载。

40脚(P2.5/PWM0):若PWM使能,则该引脚输出PWM0。

41脚(P2.6/PWM1):若PWM使能,则该引脚输出PWM1。

42脚(P2.7/PWMCLK):若PWM使能,则该引脚提供外部PWM时钟。

34脚(XTAL1):晶振反相器输入。

35脚(XTAL2):晶振反相器输出。

43脚(EA):外部访问使能,逻辑输入。当保持高电平时,此输入使能器件从地址为0000H"F7FFH的内部程序存储器内取回代码。ADuC845无外部程序存储器访问功能。为了确定代码执行模式,该引脚在外部复位结束时起作用,或将其作为器件电源周期的一部分。

44脚(PSEN):程序存储使能引脚,逻辑输出。除了在外部数据存储访问期间外,该脚每6个时钟周期有效一次。而在内部程序执行期间,此引脚保持高电平。当该引脚通过上电复位电阻或作为器件电源周期的一部分被拉至低电平时,PSEN引脚也可用作使能下载模式。

45脚(ALE):地址锁存使能,逻辑输出。在外部存储器访问期间,此输出用于把地址的低字节(适于24位数据地址空间访问的页字节)锁存在外部存储器。除了在外部数据存储器访问期间,它每6个时钟周期被激活一次。通过设置PCON SFR的PCON.4位,可禁止此引脚工作。

46"49,52"55脚(P0.0"P0.7):P0口是8位漏极开路双向I/O端口。写1的端口0引脚悬空,在此状态下可用作高阻抗输入。驱动外部逻辑高电平时,需在此端口接一个外部上拉电阻。在访问外部程序和数据存储器期间,P0口也是多路复用的低位地址和数据总线。

4 ADuC845的结构原理

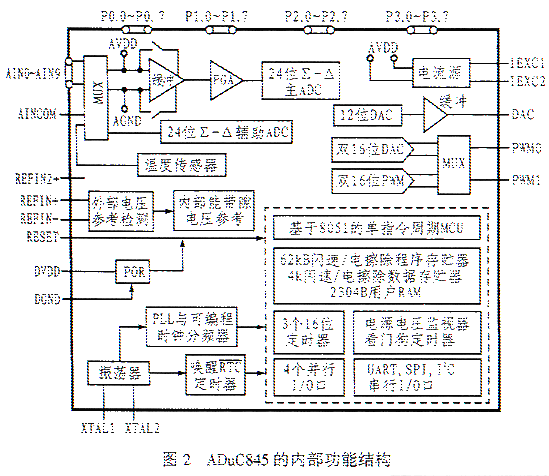

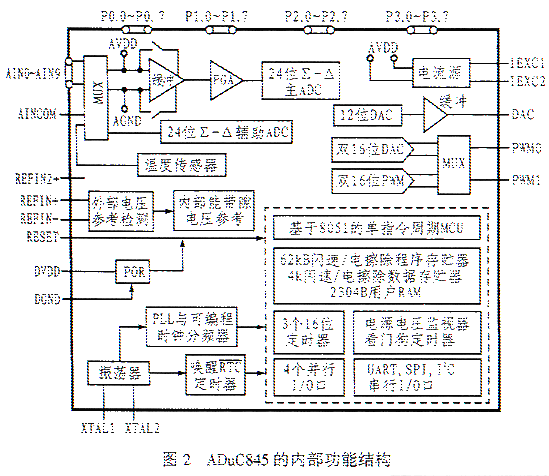

ADuC845是高度集成的24位数据采集系统,该芯片主要由两个多通道且皆可达到24位分辨率的A/D转换器、双D/A转换器以及一个8位可编程微控制器组成,其内部功能结构如图2所法。此外,ADuC845还内嵌一个单指令周期的8052闪存MCU,其片内独立的数据闪存可提供更加安全的非易失性读写功能。

4.1 ADC电路

ADuC845内含两个10通道(MQFP封装为0通道)24位Δ-∑ADC(主通道和辅助通道)、一个片内可编程增益放大器和一个用于测量宽动态范围的低频信号数字滤波器。它可被设置成4/5个全差分输入通道或8/10个伪差分通道。主通道具有缓冲器和内部缓冲禁止功能。缓冲输入通道意味着这部分电路可处理较高内阻的信号源,而且可在输入通道前加入模拟RC滤波器(以便滤波噪声和降低射频干扰)。主通道输入范围为%26;#177;20mV"%26;#177;2.56之间可分为8档,使用时可任选一档。这些通道用于转换直接来自传感器的信号,且没有外部信号条件要求。内部缓冲禁止时,可以采用外部缓冲。当内部缓冲器使能时,必须对负输入通道进行100mV的补偿,以解决缓冲器内共模输入范围有限的问题。辅助通道用于接收辅助信号的输入,此通道无缓冲器,只有一个固定有%26;#177;2.56V的增益范围。

由于ADuC845的两个A/D通道都采用Δ-∑转换技术,因而可实现24位无失码的优良性能。器件工作时,先由Δ-∑调制器将输入采样信号转换成数字脉冲串,脉冲串的工作周期包含了数字信息。然后采用Sinc3可编程低通滤波器对调制器的输出数据流进行10中抽1,以得到按可编程数据输出率从5.35Hz"105.03Hz给出的有效数据转换结果。ADuC845对调制器信号流有抽取使能和抽取禁止两种操作模式。ADCMODE寄存器内的CHOP位控制抽取操作的使能和禁止。

AD通道的设置和控制是通过专用寄存器块(SFR)中的一组寄存器来实现的。其名称以及功能如下:

ADCSTAT:状态寄存器。保持主通道和辅助通道的一般状态,包括数据准备就绪、校准状态和一些出错信号。

ADCMODE:模式寄存器。控制主通道和辅助通道的操作模式。

ADC0CON1:主通道控制寄存器1。控制主通道的配置,包括主通道的缓冲器、单极和双极译码以及模数转换通道的范围配置等。

ADC0CON2:主通道控制寄存器2。用于控制主通道的配置。

ADC1CON:辅助通道控制寄存器。控制辅助通道的配置,包括辅助通道的参考选择、通道选择及单极和双极译码。

SF:数字滤波器寄存器。通过调节器波器参数来控制主、辅通道数据的更新速率。

ICON:恒流源控制寄存器。允许用户控制片内不同的恒流源。

ADC0L/M/H:用于存放主通道的24位转换结果;

ADC1L/H:用于存放辅助通道的24位转换结果。

OF0L/M/H:用于存放主通道偏移校准系数;

OF1L/H:用于存放辅助通道偏移校准系数;

GN0L/M/H:用于存放主通道增益校准系数。

GN1LH:用于存放辅助通道增益校准系数。

4.2 ADuC845中的存储器

ADuC845为设计者提供了2个闪速/电擦除存储器阵列,即片内62kB闪速/电擦除程序存储器和片内4kB闪速/电擦除数据存储器,并具有256B通用RAM及2kB内部XRAM。

a.闪速/电擦除程序存储器

ADuC845包含一个64k字节闪速/电擦除程序存储器。其中低62k字节供用户使用,可用作程序存储器或附加NV数据存储器。高2k字节包含一个水久嵌入的固件,允许在线串行下载、串行调试和非嵌入性单引脚竞争。此固件也包含一个上电配置程序,该程序将工厂标准系数下载到各种标准外设内,如ADC、温度传感器、电流源等。这2k字节的固件隐藏在用户代码中,若对此空间进行读操作的结果为0,则用户代码出现NOP指令。在上电或硬件复位过程中,当EA引脚接至高电平时,存储器默认从内部62kB的内速/电擦除程序空间都代码的执行变得容易,无需任何外部分离的ROM器件。程序存储器可使用串行下载模式、常规的第三方提供的存储器编程器或用户在用户下载模式中定义的协议进行在线编程。正常模式下,可用两种方式编程,即:

(1)串行下载(在线编程)

ADuC845可方便地通过标准UART串行口下载程序代码。如果PSEN引脚通过外部1kΩ下拉电阻被拉至低电平,则在复位和上电后,ADuC845可进入串行下载模式。一旦处于此模式,隐藏的嵌入式下载内核开始工作,用户可以把代码下载到程序存储器,同时器件仍位于其目标应用硬件中。PC串行下载的可执行程序是作为ADuC845 QiuckStart开发系统的一部分提供的。

(2)并行编程

并行编程模式与常规的第三方闪速或EEPROM器件编程完全兼容。在此模式下,P0和P2口用作外部地址总线接口,P3口用作外部数据总线接口。P1.0用作写使能选通,P1.1"P1.4端口用作通用配置口,在并行编程期间,它可伙各种编程和擦除操作进行配置。

ADuC845具有片内加密特性,可提供三种安全模式。这些模式可被独立激活,以防止程序存储空间被自由读取。三种安全模式如下:

*加锁模式

该模式可锁存代码存储器,禁止程序存储器的并行编程,但允许在并行模式下下对此存储器进行读操作,或者通过外部存储器的MOVC命令对其进行读操作。在串行下载或并行编程模式下,通过启动“擦除代码及数据”命令使此模式无效。

*加密模式

该模式能锁存代码存储器,禁止程序存储器的并行编程,且不允许在并行模式下读/校验程序存储器或通过外部存储器的MOVC命令对内部存储器进行读操作。在串行下载或并行编程模式下,通过启动“擦除代码及数据”命令可使此模式无效。

*串行安全模式

该模式禁止串行下载代码。如果串行安全模式被激活,且试图将存储器在PSEN引脚为低电平时复位到串行下载模式,则存储器将此复位仅看作正常复位,因此,它将不会进入串行下载模式,而仅执行一个正常复位程序。在并行编程模式下,使用“擦除代码和数据”命令时,此模式无效。

b.闪速/电擦除数据存储器

闪速/电擦除数据存储器容量为4kB,它被配置为1024页,每页4个字节。它和其它外围设备一样,可通过是映射到SFR空间的寄存器组与此存储器空间相接。4个数据寄存器组(EDATA1"EDATA4)用于保存4B页数据。页寻址是通过EADRH和EADRL两个寄存器实现的。ECON是一个8位控制寄存器,这可写入9个闪速/电擦除存储器访问命令之一,以使能各种读、写、擦除和校验模式。

此存储器可用作通用非易失性缓存区,分别是高128RAM和低128B RAM。低128B RAM可通过直接或间接寻址访问,而高128B RAM只能通过间接寻址访问,原因在于它与只能通过直接寻址访问的SFR共用同一地址空间。内部数据存储器的低128字节映射中,最低的32字节分为4个区,每区含8个寄存器,编号为R0"R7。寄存器区分紧接的16字节(128位)构成了位可寻址的存储器空间块,位地址00H"07H。堆栈可位于内部存储器地址空间的任一位置,其深度可扩展到2048字节。复位初始化堆栈指针到07H。由于装载堆栈前访问或压入地址已加1的SP,因此,装载堆栈从08H开始,即从R0寄存器开始。若使用不止一个寄存器块,则堆栈指针必须被初始化到RAM区而不是用于数据保存。

d.内部XRAM

ADuC845包含一个2k字节的片内扩展数字存储器。此存储器通过MOVX指令访问。若CFG845.0位被置位,则2k字节的内部XRAM被映射到2k字节外部地址空间的底部,否则半对外部数据存储器进行访问,其方式就和标准8051一样。一旦24位DPTR溢出0007FFH,此时即便CFG845.0位被置位,系统仍可外部数据存储器进行访问。当访问内部XARM时,P0、P2引脚及RD、WR选通在每个标准8051 MOVX指令执行时将不被输出,这就允许应用将这些引脚用作标准I/O。内部XRAM的高1792字节配置为外扩的11位堆栈指地。缺省设置时,堆栈的操作同8052一样,还通用RAM内从FF到00H翻转。但在ADuC845上,通过设置CFG845.7可以使能11位的外扩堆栈指针,这种情况下,堆栈将在RAM内的FFH到XRAM内的0100H之间翻转。

4.3 串行I/O口

ADuC845具有三种串行输入/输出接口:通用串行异步接口、串行外设接口(SPI)和I2C串行接口。这里仅介绍后两种。

(1) SPI串行接口

ADuC845片内集成了一个完整的串行外设接口(SPI)。SPI是工业标准的同步串行接口,它允许8位数据同时同步地被发送和接收。需要注意的是,SPI引脚与P2引脚复用。只用SPE被置位时,复用的引脚才具有SPI功能。否则,随着SPI被清零,这些引脚将保持标准的P2口功能。该系统可配置为主、从两种操作,并由标准的4引脚组成:

SCLOCK:主机的串行时钟线,通过MOSI和MISO数据线同步传输和接收数据。每个SCLOCK周期传输和接收一个单数据位。发送/接收1B的数据需要8个SCLOCK周期。SCLOCK引脚在主模式下配置为输出,在从模式下配置为输入。主模式下,时钟的波特率、极性和相位可由SPICON来设置。

MISO:主机输入/从机输出引脚。设计时应将主机的MISO端口与从机的MISO端口相连以进行高位在前的数据交换。

MOSI:主机输出/从机输入引脚。主机的MISO应与从机的MISO相连以进行高位在前的数据交换。

MOSI:主机输出/从机输入引脚。主机的MISO应与从机的MISO相连以进行高位在前的数据交换。

SS:从机选择引脚,低电平有效。当SS引脚为低电平时,数据仅在从模式下接收和发送,这允许ADuC845用于单主机、多从机的SPI配置。

(2)I2C串行接口

ADuC845支持完全的I2C串行接口。此接口可配置为软件主操作和硬件从操作模式。I2C接口可同时用作SPI接口,它可供用户使用且其不与芯片上使用其它I/O口复用,这就意味着ADuC845芯片片上任何其它I/O口复用,这就意味着ADuC845芯片上的I2C接口和SPI接口可同时使用。当使用I2C接口时,由于他们都使用同一中断程序,在有中断产生时,必须查询接口以确定是哪一个接口触发职断服务程序请求。该接口使用如下两个引脚:

SDATA:数据I/O;

SCLK:串行时钟;

控制I2C接口的寄存器及其功能如下:

I2CCOM:I2C控制寄存器;

I2CADD:保存一个用于I2C接口的外设地址;

I2CADD1:保存一个用于I2C接口的外设地址;

I2CDAT:传输数据或读接收到的数据。访问I2CDAT可自动清除任一未处理的I2C中断和I2CCON SFR中的I2CI位。在每个中断周期内,用户代码仅能访问I2CDAT一次。

5 结束语

ADI公司的ADuC845集成了精密数据转换器、闪存和可编程微控制器,非常适合工业和仪器仪表应用中要求精确测量宽动态范围低频信号的应用场合,例如智能传感器、温度与压力传感器、称重仪、便携式仪器、电池供电系统、4"20mA控制环路和病人监护系统等。此外,该器件在主ADC和辅助ADC都采用了ADI公司的高频“斩波”专利技术,可以提供优良有直流(DC)失调和失调漂移指标,故其也非常适合于低温漂且对噪声抑制和抗电磁干扰能力要求较高的应用场合。

4 ADuC845的结构原理

ADuC845是高度集成的24位数据采集系统,该芯片主要由两个多通道且皆可达到24位分辨率的A/D转换器、双D/A转换器以及一个8位可编程微控制器组成,其内部功能结构如图2所法。此外,ADuC845还内嵌一个单指令周期的8052闪存MCU,其片内独立的数据闪存可提供更加安全的非易失性读写功能。

4.1 ADC电路

ADuC845内含两个10通道(MQFP封装为0通道)24位Δ-∑ADC(主通道和辅助通道)、一个片内可编程增益放大器和一个用于测量宽动态范围的低频信号数字滤波器。它可被设置成4/5个全差分输入通道或8/10个伪差分通道。主通道具有缓冲器和内部缓冲禁止功能。缓冲输入通道意味着这部分电路可处理较高内阻的信号源,而且可在输入通道前加入模拟RC滤波器(以便滤波噪声和降低射频干扰)。主通道输入范围为%26;#177;20mV"%26;#177;2.56之间可分为8档,使用时可任选一档。这些通道用于转换直接来自传感器的信号,且没有外部信号条件要求。内部缓冲禁止时,可以采用外部缓冲。当内部缓冲器使能时,必须对负输入通道进行100mV的补偿,以解决缓冲器内共模输入范围有限的问题。辅助通道用于接收辅助信号的输入,此通道无缓冲器,只有一个固定有%26;#177;2.56V的增益范围。

由于ADuC845的两个A/D通道都采用Δ-∑转换技术,因而可实现24位无失码的优良性能。器件工作时,先由Δ-∑调制器将输入采样信号转换成数字脉冲串,脉冲串的工作周期包含了数字信息。然后采用Sinc3可编程低通滤波器对调制器的输出数据流进行10中抽1,以得到按可编程数据输出率从5.35Hz"105.03Hz给出的有效数据转换结果。ADuC845对调制器信号流有抽取使能和抽取禁止两种操作模式。ADCMODE寄存器内的CHOP位控制抽取操作的使能和禁止。

AD通道的设置和控制是通过专用寄存器块(SFR)中的一组寄存器来实现的。其名称以及功能如下:

ADCSTAT:状态寄存器。保持主通道和辅助通道的一般状态,包括数据准备就绪、校准状态和一些出错信号。

ADCMODE:模式寄存器。控制主通道和辅助通道的操作模式。

ADC0CON1:主通道控制寄存器1。控制主通道的配置,包括主通道的缓冲器、单极和双极译码以及模数转换通道的范围配置等。

ADC0CON2:主通道控制寄存器2。用于控制主通道的配置。

ADC1CON:辅助通道控制寄存器。控制辅助通道的配置,包括辅助通道的参考选择、通道选择及单极和双极译码。

SF:数字滤波器寄存器。通过调节器波器参数来控制主、辅通道数据的更新速率。

ICON:恒流源控制寄存器。允许用户控制片内不同的恒流源。

ADC0L/M/H:用于存放主通道的24位转换结果;

ADC1L/H:用于存放辅助通道的24位转换结果。

OF0L/M/H:用于存放主通道偏移校准系数;

OF1L/H:用于存放辅助通道偏移校准系数;

GN0L/M/H:用于存放主通道增益校准系数。

GN1LH:用于存放辅助通道增益校准系数。

4.2 ADuC845中的存储器

ADuC845为设计者提供了2个闪速/电擦除存储器阵列,即片内62kB闪速/电擦除程序存储器和片内4kB闪速/电擦除数据存储器,并具有256B通用RAM及2kB内部XRAM。

a.闪速/电擦除程序存储器

ADuC845包含一个64k字节闪速/电擦除程序存储器。其中低62k字节供用户使用,可用作程序存储器或附加NV数据存储器。高2k字节包含一个水久嵌入的固件,允许在线串行下载、串行调试和非嵌入性单引脚竞争。此固件也包含一个上电配置程序,该程序将工厂标准系数下载到各种标准外设内,如ADC、温度传感器、电流源等。这2k字节的固件隐藏在用户代码中,若对此空间进行读操作的结果为0,则用户代码出现NOP指令。在上电或硬件复位过程中,当EA引脚接至高电平时,存储器默认从内部62kB的内速/电擦除程序空间都代码的执行变得容易,无需任何外部分离的ROM器件。程序存储器可使用串行下载模式、常规的第三方提供的存储器编程器或用户在用户下载模式中定义的协议进行在线编程。正常模式下,可用两种方式编程,即:

(1)串行下载(在线编程)

ADuC845可方便地通过标准UART串行口下载程序代码。如果PSEN引脚通过外部1kΩ下拉电阻被拉至低电平,则在复位和上电后,ADuC845可进入串行下载模式。一旦处于此模式,隐藏的嵌入式下载内核开始工作,用户可以把代码下载到程序存储器,同时器件仍位于其目标应用硬件中。PC串行下载的可执行程序是作为ADuC845 QiuckStart开发系统的一部分提供的。

(2)并行编程

并行编程模式与常规的第三方闪速或EEPROM器件编程完全兼容。在此模式下,P0和P2口用作外部地址总线接口,P3口用作外部数据总线接口。P1.0用作写使能选通,P1.1"P1.4端口用作通用配置口,在并行编程期间,它可伙各种编程和擦除操作进行配置。

ADuC845具有片内加密特性,可提供三种安全模式。这些模式可被独立激活,以防止程序存储空间被自由读取。三种安全模式如下:

*加锁模式

该模式可锁存代码存储器,禁止程序存储器的并行编程,但允许在并行模式下下对此存储器进行读操作,或者通过外部存储器的MOVC命令对其进行读操作。在串行下载或并行编程模式下,通过启动“擦除代码及数据”命令使此模式无效。

*加密模式

该模式能锁存代码存储器,禁止程序存储器的并行编程,且不允许在并行模式下读/校验程序存储器或通过外部存储器的MOVC命令对内部存储器进行读操作。在串行下载或并行编程模式下,通过启动“擦除代码及数据”命令可使此模式无效。

*串行安全模式

该模式禁止串行下载代码。如果串行安全模式被激活,且试图将存储器在PSEN引脚为低电平时复位到串行下载模式,则存储器将此复位仅看作正常复位,因此,它将不会进入串行下载模式,而仅执行一个正常复位程序。在并行编程模式下,使用“擦除代码和数据”命令时,此模式无效。

b.闪速/电擦除数据存储器

闪速/电擦除数据存储器容量为4kB,它被配置为1024页,每页4个字节。它和其它外围设备一样,可通过是映射到SFR空间的寄存器组与此存储器空间相接。4个数据寄存器组(EDATA1"EDATA4)用于保存4B页数据。页寻址是通过EADRH和EADRL两个寄存器实现的。ECON是一个8位控制寄存器,这可写入9个闪速/电擦除存储器访问命令之一,以使能各种读、写、擦除和校验模式。

此存储器可用作通用非易失性缓存区,分别是高128RAM和低128B RAM。低128B RAM可通过直接或间接寻址访问,而高128B RAM只能通过间接寻址访问,原因在于它与只能通过直接寻址访问的SFR共用同一地址空间。内部数据存储器的低128字节映射中,最低的32字节分为4个区,每区含8个寄存器,编号为R0"R7。寄存器区分紧接的16字节(128位)构成了位可寻址的存储器空间块,位地址00H"07H。堆栈可位于内部存储器地址空间的任一位置,其深度可扩展到2048字节。复位初始化堆栈指针到07H。由于装载堆栈前访问或压入地址已加1的SP,因此,装载堆栈从08H开始,即从R0寄存器开始。若使用不止一个寄存器块,则堆栈指针必须被初始化到RAM区而不是用于数据保存。

d.内部XRAM

ADuC845包含一个2k字节的片内扩展数字存储器。此存储器通过MOVX指令访问。若CFG845.0位被置位,则2k字节的内部XRAM被映射到2k字节外部地址空间的底部,否则半对外部数据存储器进行访问,其方式就和标准8051一样。一旦24位DPTR溢出0007FFH,此时即便CFG845.0位被置位,系统仍可外部数据存储器进行访问。当访问内部XARM时,P0、P2引脚及RD、WR选通在每个标准8051 MOVX指令执行时将不被输出,这就允许应用将这些引脚用作标准I/O。内部XRAM的高1792字节配置为外扩的11位堆栈指地。缺省设置时,堆栈的操作同8052一样,还通用RAM内从FF到00H翻转。但在ADuC845上,通过设置CFG845.7可以使能11位的外扩堆栈指针,这种情况下,堆栈将在RAM内的FFH到XRAM内的0100H之间翻转。

4.3 串行I/O口

ADuC845具有三种串行输入/输出接口:通用串行异步接口、串行外设接口(SPI)和I2C串行接口。这里仅介绍后两种。

(1) SPI串行接口

ADuC845片内集成了一个完整的串行外设接口(SPI)。SPI是工业标准的同步串行接口,它允许8位数据同时同步地被发送和接收。需要注意的是,SPI引脚与P2引脚复用。只用SPE被置位时,复用的引脚才具有SPI功能。否则,随着SPI被清零,这些引脚将保持标准的P2口功能。该系统可配置为主、从两种操作,并由标准的4引脚组成:

SCLOCK:主机的串行时钟线,通过MOSI和MISO数据线同步传输和接收数据。每个SCLOCK周期传输和接收一个单数据位。发送/接收1B的数据需要8个SCLOCK周期。SCLOCK引脚在主模式下配置为输出,在从模式下配置为输入。主模式下,时钟的波特率、极性和相位可由SPICON来设置。

MISO:主机输入/从机输出引脚。设计时应将主机的MISO端口与从机的MISO端口相连以进行高位在前的数据交换。

MOSI:主机输出/从机输入引脚。主机的MISO应与从机的MISO相连以进行高位在前的数据交换。

MOSI:主机输出/从机输入引脚。主机的MISO应与从机的MISO相连以进行高位在前的数据交换。

SS:从机选择引脚,低电平有效。当SS引脚为低电平时,数据仅在从模式下接收和发送,这允许ADuC845用于单主机、多从机的SPI配置。

(2)I2C串行接口

ADuC845支持完全的I2C串行接口。此接口可配置为软件主操作和硬件从操作模式。I2C接口可同时用作SPI接口,它可供用户使用且其不与芯片上使用其它I/O口复用,这就意味着ADuC845芯片片上任何其它I/O口复用,这就意味着ADuC845芯片上的I2C接口和SPI接口可同时使用。当使用I2C接口时,由于他们都使用同一中断程序,在有中断产生时,必须查询接口以确定是哪一个接口触发职断服务程序请求。该接口使用如下两个引脚:

SDATA:数据I/O;

SCLK:串行时钟;

控制I2C接口的寄存器及其功能如下:

I2CCOM:I2C控制寄存器;

I2CADD:保存一个用于I2C接口的外设地址;

I2CADD1:保存一个用于I2C接口的外设地址;

I2CDAT:传输数据或读接收到的数据。访问I2CDAT可自动清除任一未处理的I2C中断和I2CCON SFR中的I2CI位。在每个中断周期内,用户代码仅能访问I2CDAT一次。

5 结束语

ADI公司的ADuC845集成了精密数据转换器、闪存和可编程微控制器,非常适合工业和仪器仪表应用中要求精确测量宽动态范围低频信号的应用场合,例如智能传感器、温度与压力传感器、称重仪、便携式仪器、电池供电系统、4"20mA控制环路和病人监护系统等。此外,该器件在主ADC和辅助ADC都采用了ADI公司的高频“斩波”专利技术,可以提供优良有直流(DC)失调和失调漂移指标,故其也非常适合于低温漂且对噪声抑制和抗电磁干扰能力要求较高的应用场合。

编辑: 引用地址:内嵌闪存MCU的高性能多通道24位采集系统ADuC845

2 ADuC845的性能特点

2.1 高分辨率Δ-∑ADC

*带有2个独立的10通道、24位模/数转换器(ADC);

*24位无失码主ADC;

*在60Hz范围内有20位有效分辨率(17.4位峰-峰分辨率);

*芯片的失调漂移为10nV/℃,增益漂移为0.5ppm/℃。

2.2 存储器

*62k字节片内闪速/电擦除程序存储器;

*4k字节片内闪速/电擦除数据存储器;

*闪速/电擦除存储器可使用100年,可重复擦写10万次;

*有3种闪速/电擦除程序存储器安全模式;

*在线串行下载(无需外部硬件);

*带有高速用户下载(5秒)功能;

*带有2304字节片内数据RAM。

2.3 基于8051的内核

*具有与8051兼容的指令系统;

*高性能单指令周期内核;

*可使用32kHz外部晶振;

*具有片内可编程锁相环PLL(最高时钟频率12.58MHz);

*有3个16位定时/计数器;

*有26条可编程输入/输出线;

*11个中断源,2个优先级;

*双数据指针,扩展的11位堆栈指针。

2.4 片内外围设备

*内部电源复位电路;

*12位电压输出DAC;

*双16位Δ-∑DAC/PWM;

*片内温度传感器;

*双激励电流源;

*时间间隔计数器(唤醒/RTC定时器);

*UART,I2C和SPI串行接口;

*高速波特率发生器(包括115,200);

*看门狗定时器(WDT);

*电源监视器(PSM)。

2.5 电源

*可用3V和5V电压工作;

*正常情况下为2.3mA/3.6V(核心时钟频率为1.57MHz);

*掉电保持电流为20μA,可唤桓定时运行。

3 ADuC845的引脚功能

ADuC845的引脚排列如图1所示,其中采用56引脚封装的管脚功能如下:

56脚(P1.0/AIN1):上电缺省设置为AIN1模拟输入。使用AINCON时,AIN1用作伪差分输入;使用AIN2时,该脚用作全差分对的正向输入。P1.0端口无数输出驱动器。为把其配置为数字输入,应把0写至端口值。作数字输入时,该引脚必须由外部驱动到高电平或低电平。

1脚(P1.1/AIN2):上电缺省设置为AIN2模拟输入。使用AINCON时,AIN2用作伪差分输入;使用AIN1时,用作全差分对的负向输入。输入同P1.0。

2脚(P1.2/AIN3/REFIN2+):上电缺省设置为AIN3模拟输入。使用AINCOM时,AIN3用作伪差分输入;使用AIN4时,用作全差分对的正向输入。数字输入同P1.0。另外,该引脚亦可用作第二个外部差分参考输入的正向输入端。

3脚(P1.3/AIN4/REFIN2-):上电缺省设置为AIN4模拟输入。使用AINCOM时,AIN4用作伪差分输入;使用AIN3时,用作全差分对的负向输入。数字输入同P1.0。另外,该引脚亦可用作第二个外部差分参考输入的负向输入端。

4脚(AVDD):模拟电源。

5,6脚(AGND):模拟地。

7脚(REFIN-):外部差分参考输入的负向输入端。

8脚(REFIN+):外部差分参考输入的正向输入端。

9脚(P1.4/AIN5):上电缺省设置为AIN5模拟输入。使用AINCOM时,AIN5用作伪差分输入;使用AIN6时,用作全差分对的正向输入。输入同P1.0。

10脚(P1.5/AIN6):上电缺省设置为AIN6模拟输入。使用AINCOM时,AIN6用作伪差分输入;使用AIN5时,用作差分对的负向输入。输入同P1.0。

11脚(P1.6/AIN7/IEXC1):上电缺省设置为AIN7模拟输入。使用AINCOM时,AIN7用作伪差分输入;使用AIN8时,用作全差分对的正向输入。该引脚可配置1"2个电流源。数字输入同P1.0。

12脚(P1.7/AIN8/IEXC2):上电缺省设置为AIN8模拟输入。使用AINCOM时,AIN8用作伪差分输入;使用AIN7时,用作全差分对的负向输入。该引脚可配置1"2个电流源。数字输入同P1.0。

13脚(AINCOM/DAC):若选定相关的伪差分输入,则所有的模拟输入必须参考此引脚。该引脚亦可作为DAC的输出引脚之一。

14脚(DAC):若DAC使能,则该引脚输出DAC电压。

15脚(AIN9):使用AINCOM时,AIN9用作伪差分输入;使用AIN10时,用作全差分对的正向输入。

16脚(AIN10):使用AINCOM时,AIN10用作伪差分输入;使用AIN9时,用作全差分对的负向输入。

17脚(RESET):复位输入。当振荡器运行时,该引脚上长达16个主时钟周期的高电平半使器件复位。

18"21,24"27脚(P3.0"P3.7):P3口是具有内部上拉电阻的双向口。当写1的端口3被内部上拉至高电平时,它们可用作输入。由于有内部上拉电阻,被外部拉至低电平的端口3引脚将提供电流。当驱动一个0-1的输出转换时,上拉功能将被激活并持续2个内部时钟周期的指令循环。

18脚(P3.0/RED):UART串行口接收数据。

19脚(P3.1/TXD):UART串行口发送数据。

20脚(P3.2/INT0):外部中断0,此引脚也可用作选通门,控制定时器0的输入。

21脚(P3.3/INT1):外部中断0,此引脚也可用作选通门,控制定时器1的输入。

24脚(P3.4/T0):定时器/计数器0输入。

25脚(P3.5/T1):定时器/计数器1输入。

26脚(P3.6/WR):写控制信号。把来自P0口的数据字节锁存入外部数据存储器。

27脚(P3.7/RD):读控制信号。将外部数据存储器中的数据读到P0口。

22,36,51脚(DVDD):数字电源。

23,37,38脚(DGND):数字地。

28脚(SCLK):I2C串行接口时钟。作输入口使用时,除输出逻辑低电平外,该引脚为施密特触发输入,且存在一个弱的内部上拉。此引脚亦可作为数字输出口使用,通常由软件控制。

29脚(SDATA):I2C串行数据输入口。作为输入口时,该引脚有一个弱的内部上拉出现,除非它输出逻辑低电平。

30"33,39"42(P2.0"P2.7):P2口是具有内部上拉电阻的双向口。当写1的端口2被内部上拉电阻拉至高电平时,这些引脚可用作输入。由于内部上拉电阻,被外部拉至低电平的端口2引脚将提供电流。在访问24位外部数据存储器空间的过程中P2口发出中和高地址字节。

30脚(P2.0/SCLOCK):SPI串行接口时钟。作输入口使用时,除输出逻辑低电平外,该引脚为施密特触发输入,且存在一个弱的内部上拉。

31脚(P2.1/MOSI):用于SPI接口的SPI主输出/从输入数据I/O引脚。

32脚(P2.3/SS/T2):SPI接口的从属选择输入,该引脚有一个弱的上拉作用。该引脚能给定时器2提供时钟输入,此项功能启动时,计数器2增加坟数以响应T2输入引脚出现的负跳变。

39脚(P2.4/T2EX):用于向定时器2提供控制输入。此项功能启动时,此引脚上出现的负跳变将使定时器2捕获或重载。

40脚(P2.5/PWM0):若PWM使能,则该引脚输出PWM0。

41脚(P2.6/PWM1):若PWM使能,则该引脚输出PWM1。

42脚(P2.7/PWMCLK):若PWM使能,则该引脚提供外部PWM时钟。

34脚(XTAL1):晶振反相器输入。

35脚(XTAL2):晶振反相器输出。

43脚(EA):外部访问使能,逻辑输入。当保持高电平时,此输入使能器件从地址为0000H"F7FFH的内部程序存储器内取回代码。ADuC845无外部程序存储器访问功能。为了确定代码执行模式,该引脚在外部复位结束时起作用,或将其作为器件电源周期的一部分。

44脚(PSEN):程序存储使能引脚,逻辑输出。除了在外部数据存储访问期间外,该脚每6个时钟周期有效一次。而在内部程序执行期间,此引脚保持高电平。当该引脚通过上电复位电阻或作为器件电源周期的一部分被拉至低电平时,PSEN引脚也可用作使能下载模式。

45脚(ALE):地址锁存使能,逻辑输出。在外部存储器访问期间,此输出用于把地址的低字节(适于24位数据地址空间访问的页字节)锁存在外部存储器。除了在外部数据存储器访问期间,它每6个时钟周期被激活一次。通过设置PCON SFR的PCON.4位,可禁止此引脚工作。

46"49,52"55脚(P0.0"P0.7):P0口是8位漏极开路双向I/O端口。写1的端口0引脚悬空,在此状态下可用作高阻抗输入。驱动外部逻辑高电平时,需在此端口接一个外部上拉电阻。在访问外部程序和数据存储器期间,P0口也是多路复用的低位地址和数据总线。

2 ADuC845的性能特点

2.1 高分辨率Δ-∑ADC

*带有2个独立的10通道、24位模/数转换器(ADC);

*24位无失码主ADC;

*在60Hz范围内有20位有效分辨率(17.4位峰-峰分辨率);

*芯片的失调漂移为10nV/℃,增益漂移为0.5ppm/℃。

2.2 存储器

*62k字节片内闪速/电擦除程序存储器;

*4k字节片内闪速/电擦除数据存储器;

*闪速/电擦除存储器可使用100年,可重复擦写10万次;

*有3种闪速/电擦除程序存储器安全模式;

*在线串行下载(无需外部硬件);

*带有高速用户下载(5秒)功能;

*带有2304字节片内数据RAM。

2.3 基于8051的内核

*具有与8051兼容的指令系统;

*高性能单指令周期内核;

*可使用32kHz外部晶振;

*具有片内可编程锁相环PLL(最高时钟频率12.58MHz);

*有3个16位定时/计数器;

*有26条可编程输入/输出线;

*11个中断源,2个优先级;

*双数据指针,扩展的11位堆栈指针。

2.4 片内外围设备

*内部电源复位电路;

*12位电压输出DAC;

*双16位Δ-∑DAC/PWM;

*片内温度传感器;

*双激励电流源;

*时间间隔计数器(唤醒/RTC定时器);

*UART,I2C和SPI串行接口;

*高速波特率发生器(包括115,200);

*看门狗定时器(WDT);

*电源监视器(PSM)。

2.5 电源

*可用3V和5V电压工作;

*正常情况下为2.3mA/3.6V(核心时钟频率为1.57MHz);

*掉电保持电流为20μA,可唤桓定时运行。

3 ADuC845的引脚功能

ADuC845的引脚排列如图1所示,其中采用56引脚封装的管脚功能如下:

56脚(P1.0/AIN1):上电缺省设置为AIN1模拟输入。使用AINCON时,AIN1用作伪差分输入;使用AIN2时,该脚用作全差分对的正向输入。P1.0端口无数输出驱动器。为把其配置为数字输入,应把0写至端口值。作数字输入时,该引脚必须由外部驱动到高电平或低电平。

1脚(P1.1/AIN2):上电缺省设置为AIN2模拟输入。使用AINCON时,AIN2用作伪差分输入;使用AIN1时,用作全差分对的负向输入。输入同P1.0。

2脚(P1.2/AIN3/REFIN2+):上电缺省设置为AIN3模拟输入。使用AINCOM时,AIN3用作伪差分输入;使用AIN4时,用作全差分对的正向输入。数字输入同P1.0。另外,该引脚亦可用作第二个外部差分参考输入的正向输入端。

3脚(P1.3/AIN4/REFIN2-):上电缺省设置为AIN4模拟输入。使用AINCOM时,AIN4用作伪差分输入;使用AIN3时,用作全差分对的负向输入。数字输入同P1.0。另外,该引脚亦可用作第二个外部差分参考输入的负向输入端。

4脚(AVDD):模拟电源。

5,6脚(AGND):模拟地。

7脚(REFIN-):外部差分参考输入的负向输入端。

8脚(REFIN+):外部差分参考输入的正向输入端。

9脚(P1.4/AIN5):上电缺省设置为AIN5模拟输入。使用AINCOM时,AIN5用作伪差分输入;使用AIN6时,用作全差分对的正向输入。输入同P1.0。

10脚(P1.5/AIN6):上电缺省设置为AIN6模拟输入。使用AINCOM时,AIN6用作伪差分输入;使用AIN5时,用作差分对的负向输入。输入同P1.0。

11脚(P1.6/AIN7/IEXC1):上电缺省设置为AIN7模拟输入。使用AINCOM时,AIN7用作伪差分输入;使用AIN8时,用作全差分对的正向输入。该引脚可配置1"2个电流源。数字输入同P1.0。

12脚(P1.7/AIN8/IEXC2):上电缺省设置为AIN8模拟输入。使用AINCOM时,AIN8用作伪差分输入;使用AIN7时,用作全差分对的负向输入。该引脚可配置1"2个电流源。数字输入同P1.0。

13脚(AINCOM/DAC):若选定相关的伪差分输入,则所有的模拟输入必须参考此引脚。该引脚亦可作为DAC的输出引脚之一。

14脚(DAC):若DAC使能,则该引脚输出DAC电压。

15脚(AIN9):使用AINCOM时,AIN9用作伪差分输入;使用AIN10时,用作全差分对的正向输入。

16脚(AIN10):使用AINCOM时,AIN10用作伪差分输入;使用AIN9时,用作全差分对的负向输入。

17脚(RESET):复位输入。当振荡器运行时,该引脚上长达16个主时钟周期的高电平半使器件复位。

18"21,24"27脚(P3.0"P3.7):P3口是具有内部上拉电阻的双向口。当写1的端口3被内部上拉至高电平时,它们可用作输入。由于有内部上拉电阻,被外部拉至低电平的端口3引脚将提供电流。当驱动一个0-1的输出转换时,上拉功能将被激活并持续2个内部时钟周期的指令循环。

18脚(P3.0/RED):UART串行口接收数据。

19脚(P3.1/TXD):UART串行口发送数据。

20脚(P3.2/INT0):外部中断0,此引脚也可用作选通门,控制定时器0的输入。

21脚(P3.3/INT1):外部中断0,此引脚也可用作选通门,控制定时器1的输入。

24脚(P3.4/T0):定时器/计数器0输入。

25脚(P3.5/T1):定时器/计数器1输入。

26脚(P3.6/WR):写控制信号。把来自P0口的数据字节锁存入外部数据存储器。

27脚(P3.7/RD):读控制信号。将外部数据存储器中的数据读到P0口。

22,36,51脚(DVDD):数字电源。

23,37,38脚(DGND):数字地。

28脚(SCLK):I2C串行接口时钟。作输入口使用时,除输出逻辑低电平外,该引脚为施密特触发输入,且存在一个弱的内部上拉。此引脚亦可作为数字输出口使用,通常由软件控制。

29脚(SDATA):I2C串行数据输入口。作为输入口时,该引脚有一个弱的内部上拉出现,除非它输出逻辑低电平。

30"33,39"42(P2.0"P2.7):P2口是具有内部上拉电阻的双向口。当写1的端口2被内部上拉电阻拉至高电平时,这些引脚可用作输入。由于内部上拉电阻,被外部拉至低电平的端口2引脚将提供电流。在访问24位外部数据存储器空间的过程中P2口发出中和高地址字节。

30脚(P2.0/SCLOCK):SPI串行接口时钟。作输入口使用时,除输出逻辑低电平外,该引脚为施密特触发输入,且存在一个弱的内部上拉。

31脚(P2.1/MOSI):用于SPI接口的SPI主输出/从输入数据I/O引脚。

32脚(P2.3/SS/T2):SPI接口的从属选择输入,该引脚有一个弱的上拉作用。该引脚能给定时器2提供时钟输入,此项功能启动时,计数器2增加坟数以响应T2输入引脚出现的负跳变。

39脚(P2.4/T2EX):用于向定时器2提供控制输入。此项功能启动时,此引脚上出现的负跳变将使定时器2捕获或重载。

40脚(P2.5/PWM0):若PWM使能,则该引脚输出PWM0。

41脚(P2.6/PWM1):若PWM使能,则该引脚输出PWM1。

42脚(P2.7/PWMCLK):若PWM使能,则该引脚提供外部PWM时钟。

34脚(XTAL1):晶振反相器输入。

35脚(XTAL2):晶振反相器输出。

43脚(EA):外部访问使能,逻辑输入。当保持高电平时,此输入使能器件从地址为0000H"F7FFH的内部程序存储器内取回代码。ADuC845无外部程序存储器访问功能。为了确定代码执行模式,该引脚在外部复位结束时起作用,或将其作为器件电源周期的一部分。

44脚(PSEN):程序存储使能引脚,逻辑输出。除了在外部数据存储访问期间外,该脚每6个时钟周期有效一次。而在内部程序执行期间,此引脚保持高电平。当该引脚通过上电复位电阻或作为器件电源周期的一部分被拉至低电平时,PSEN引脚也可用作使能下载模式。

45脚(ALE):地址锁存使能,逻辑输出。在外部存储器访问期间,此输出用于把地址的低字节(适于24位数据地址空间访问的页字节)锁存在外部存储器。除了在外部数据存储器访问期间,它每6个时钟周期被激活一次。通过设置PCON SFR的PCON.4位,可禁止此引脚工作。

46"49,52"55脚(P0.0"P0.7):P0口是8位漏极开路双向I/O端口。写1的端口0引脚悬空,在此状态下可用作高阻抗输入。驱动外部逻辑高电平时,需在此端口接一个外部上拉电阻。在访问外部程序和数据存储器期间,P0口也是多路复用的低位地址和数据总线。

4 ADuC845的结构原理

ADuC845是高度集成的24位数据采集系统,该芯片主要由两个多通道且皆可达到24位分辨率的A/D转换器、双D/A转换器以及一个8位可编程微控制器组成,其内部功能结构如图2所法。此外,ADuC845还内嵌一个单指令周期的8052闪存MCU,其片内独立的数据闪存可提供更加安全的非易失性读写功能。

4.1 ADC电路

ADuC845内含两个10通道(MQFP封装为0通道)24位Δ-∑ADC(主通道和辅助通道)、一个片内可编程增益放大器和一个用于测量宽动态范围的低频信号数字滤波器。它可被设置成4/5个全差分输入通道或8/10个伪差分通道。主通道具有缓冲器和内部缓冲禁止功能。缓冲输入通道意味着这部分电路可处理较高内阻的信号源,而且可在输入通道前加入模拟RC滤波器(以便滤波噪声和降低射频干扰)。主通道输入范围为%26;#177;20mV"%26;#177;2.56之间可分为8档,使用时可任选一档。这些通道用于转换直接来自传感器的信号,且没有外部信号条件要求。内部缓冲禁止时,可以采用外部缓冲。当内部缓冲器使能时,必须对负输入通道进行100mV的补偿,以解决缓冲器内共模输入范围有限的问题。辅助通道用于接收辅助信号的输入,此通道无缓冲器,只有一个固定有%26;#177;2.56V的增益范围。

由于ADuC845的两个A/D通道都采用Δ-∑转换技术,因而可实现24位无失码的优良性能。器件工作时,先由Δ-∑调制器将输入采样信号转换成数字脉冲串,脉冲串的工作周期包含了数字信息。然后采用Sinc3可编程低通滤波器对调制器的输出数据流进行10中抽1,以得到按可编程数据输出率从5.35Hz"105.03Hz给出的有效数据转换结果。ADuC845对调制器信号流有抽取使能和抽取禁止两种操作模式。ADCMODE寄存器内的CHOP位控制抽取操作的使能和禁止。

AD通道的设置和控制是通过专用寄存器块(SFR)中的一组寄存器来实现的。其名称以及功能如下:

ADCSTAT:状态寄存器。保持主通道和辅助通道的一般状态,包括数据准备就绪、校准状态和一些出错信号。

ADCMODE:模式寄存器。控制主通道和辅助通道的操作模式。

ADC0CON1:主通道控制寄存器1。控制主通道的配置,包括主通道的缓冲器、单极和双极译码以及模数转换通道的范围配置等。

ADC0CON2:主通道控制寄存器2。用于控制主通道的配置。

ADC1CON:辅助通道控制寄存器。控制辅助通道的配置,包括辅助通道的参考选择、通道选择及单极和双极译码。

SF:数字滤波器寄存器。通过调节器波器参数来控制主、辅通道数据的更新速率。

ICON:恒流源控制寄存器。允许用户控制片内不同的恒流源。

ADC0L/M/H:用于存放主通道的24位转换结果;

ADC1L/H:用于存放辅助通道的24位转换结果。

OF0L/M/H:用于存放主通道偏移校准系数;

OF1L/H:用于存放辅助通道偏移校准系数;

GN0L/M/H:用于存放主通道增益校准系数。

GN1LH:用于存放辅助通道增益校准系数。

4.2 ADuC845中的存储器

ADuC845为设计者提供了2个闪速/电擦除存储器阵列,即片内62kB闪速/电擦除程序存储器和片内4kB闪速/电擦除数据存储器,并具有256B通用RAM及2kB内部XRAM。

a.闪速/电擦除程序存储器

ADuC845包含一个64k字节闪速/电擦除程序存储器。其中低62k字节供用户使用,可用作程序存储器或附加NV数据存储器。高2k字节包含一个水久嵌入的固件,允许在线串行下载、串行调试和非嵌入性单引脚竞争。此固件也包含一个上电配置程序,该程序将工厂标准系数下载到各种标准外设内,如ADC、温度传感器、电流源等。这2k字节的固件隐藏在用户代码中,若对此空间进行读操作的结果为0,则用户代码出现NOP指令。在上电或硬件复位过程中,当EA引脚接至高电平时,存储器默认从内部62kB的内速/电擦除程序空间都代码的执行变得容易,无需任何外部分离的ROM器件。程序存储器可使用串行下载模式、常规的第三方提供的存储器编程器或用户在用户下载模式中定义的协议进行在线编程。正常模式下,可用两种方式编程,即:

(1)串行下载(在线编程)

ADuC845可方便地通过标准UART串行口下载程序代码。如果PSEN引脚通过外部1kΩ下拉电阻被拉至低电平,则在复位和上电后,ADuC845可进入串行下载模式。一旦处于此模式,隐藏的嵌入式下载内核开始工作,用户可以把代码下载到程序存储器,同时器件仍位于其目标应用硬件中。PC串行下载的可执行程序是作为ADuC845 QiuckStart开发系统的一部分提供的。

(2)并行编程

并行编程模式与常规的第三方闪速或EEPROM器件编程完全兼容。在此模式下,P0和P2口用作外部地址总线接口,P3口用作外部数据总线接口。P1.0用作写使能选通,P1.1"P1.4端口用作通用配置口,在并行编程期间,它可伙各种编程和擦除操作进行配置。

ADuC845具有片内加密特性,可提供三种安全模式。这些模式可被独立激活,以防止程序存储空间被自由读取。三种安全模式如下:

*加锁模式

该模式可锁存代码存储器,禁止程序存储器的并行编程,但允许在并行模式下下对此存储器进行读操作,或者通过外部存储器的MOVC命令对其进行读操作。在串行下载或并行编程模式下,通过启动“擦除代码及数据”命令使此模式无效。

*加密模式

该模式能锁存代码存储器,禁止程序存储器的并行编程,且不允许在并行模式下读/校验程序存储器或通过外部存储器的MOVC命令对内部存储器进行读操作。在串行下载或并行编程模式下,通过启动“擦除代码及数据”命令可使此模式无效。

*串行安全模式

该模式禁止串行下载代码。如果串行安全模式被激活,且试图将存储器在PSEN引脚为低电平时复位到串行下载模式,则存储器将此复位仅看作正常复位,因此,它将不会进入串行下载模式,而仅执行一个正常复位程序。在并行编程模式下,使用“擦除代码和数据”命令时,此模式无效。

b.闪速/电擦除数据存储器

闪速/电擦除数据存储器容量为4kB,它被配置为1024页,每页4个字节。它和其它外围设备一样,可通过是映射到SFR空间的寄存器组与此存储器空间相接。4个数据寄存器组(EDATA1"EDATA4)用于保存4B页数据。页寻址是通过EADRH和EADRL两个寄存器实现的。ECON是一个8位控制寄存器,这可写入9个闪速/电擦除存储器访问命令之一,以使能各种读、写、擦除和校验模式。

此存储器可用作通用非易失性缓存区,分别是高128RAM和低128B RAM。低128B RAM可通过直接或间接寻址访问,而高128B RAM只能通过间接寻址访问,原因在于它与只能通过直接寻址访问的SFR共用同一地址空间。内部数据存储器的低128字节映射中,最低的32字节分为4个区,每区含8个寄存器,编号为R0"R7。寄存器区分紧接的16字节(128位)构成了位可寻址的存储器空间块,位地址00H"07H。堆栈可位于内部存储器地址空间的任一位置,其深度可扩展到2048字节。复位初始化堆栈指针到07H。由于装载堆栈前访问或压入地址已加1的SP,因此,装载堆栈从08H开始,即从R0寄存器开始。若使用不止一个寄存器块,则堆栈指针必须被初始化到RAM区而不是用于数据保存。

d.内部XRAM

ADuC845包含一个2k字节的片内扩展数字存储器。此存储器通过MOVX指令访问。若CFG845.0位被置位,则2k字节的内部XRAM被映射到2k字节外部地址空间的底部,否则半对外部数据存储器进行访问,其方式就和标准8051一样。一旦24位DPTR溢出0007FFH,此时即便CFG845.0位被置位,系统仍可外部数据存储器进行访问。当访问内部XARM时,P0、P2引脚及RD、WR选通在每个标准8051 MOVX指令执行时将不被输出,这就允许应用将这些引脚用作标准I/O。内部XRAM的高1792字节配置为外扩的11位堆栈指地。缺省设置时,堆栈的操作同8052一样,还通用RAM内从FF到00H翻转。但在ADuC845上,通过设置CFG845.7可以使能11位的外扩堆栈指针,这种情况下,堆栈将在RAM内的FFH到XRAM内的0100H之间翻转。

4.3 串行I/O口

ADuC845具有三种串行输入/输出接口:通用串行异步接口、串行外设接口(SPI)和I2C串行接口。这里仅介绍后两种。

(1) SPI串行接口

ADuC845片内集成了一个完整的串行外设接口(SPI)。SPI是工业标准的同步串行接口,它允许8位数据同时同步地被发送和接收。需要注意的是,SPI引脚与P2引脚复用。只用SPE被置位时,复用的引脚才具有SPI功能。否则,随着SPI被清零,这些引脚将保持标准的P2口功能。该系统可配置为主、从两种操作,并由标准的4引脚组成:

SCLOCK:主机的串行时钟线,通过MOSI和MISO数据线同步传输和接收数据。每个SCLOCK周期传输和接收一个单数据位。发送/接收1B的数据需要8个SCLOCK周期。SCLOCK引脚在主模式下配置为输出,在从模式下配置为输入。主模式下,时钟的波特率、极性和相位可由SPICON来设置。

MISO:主机输入/从机输出引脚。设计时应将主机的MISO端口与从机的MISO端口相连以进行高位在前的数据交换。

MOSI:主机输出/从机输入引脚。主机的MISO应与从机的MISO相连以进行高位在前的数据交换。

MOSI:主机输出/从机输入引脚。主机的MISO应与从机的MISO相连以进行高位在前的数据交换。

SS:从机选择引脚,低电平有效。当SS引脚为低电平时,数据仅在从模式下接收和发送,这允许ADuC845用于单主机、多从机的SPI配置。

(2)I2C串行接口

ADuC845支持完全的I2C串行接口。此接口可配置为软件主操作和硬件从操作模式。I2C接口可同时用作SPI接口,它可供用户使用且其不与芯片上使用其它I/O口复用,这就意味着ADuC845芯片片上任何其它I/O口复用,这就意味着ADuC845芯片上的I2C接口和SPI接口可同时使用。当使用I2C接口时,由于他们都使用同一中断程序,在有中断产生时,必须查询接口以确定是哪一个接口触发职断服务程序请求。该接口使用如下两个引脚:

SDATA:数据I/O;

SCLK:串行时钟;

控制I2C接口的寄存器及其功能如下:

I2CCOM:I2C控制寄存器;

I2CADD:保存一个用于I2C接口的外设地址;

I2CADD1:保存一个用于I2C接口的外设地址;

I2CDAT:传输数据或读接收到的数据。访问I2CDAT可自动清除任一未处理的I2C中断和I2CCON SFR中的I2CI位。在每个中断周期内,用户代码仅能访问I2CDAT一次。

5 结束语

ADI公司的ADuC845集成了精密数据转换器、闪存和可编程微控制器,非常适合工业和仪器仪表应用中要求精确测量宽动态范围低频信号的应用场合,例如智能传感器、温度与压力传感器、称重仪、便携式仪器、电池供电系统、4"20mA控制环路和病人监护系统等。此外,该器件在主ADC和辅助ADC都采用了ADI公司的高频“斩波”专利技术,可以提供优良有直流(DC)失调和失调漂移指标,故其也非常适合于低温漂且对噪声抑制和抗电磁干扰能力要求较高的应用场合。

4 ADuC845的结构原理

ADuC845是高度集成的24位数据采集系统,该芯片主要由两个多通道且皆可达到24位分辨率的A/D转换器、双D/A转换器以及一个8位可编程微控制器组成,其内部功能结构如图2所法。此外,ADuC845还内嵌一个单指令周期的8052闪存MCU,其片内独立的数据闪存可提供更加安全的非易失性读写功能。

4.1 ADC电路

ADuC845内含两个10通道(MQFP封装为0通道)24位Δ-∑ADC(主通道和辅助通道)、一个片内可编程增益放大器和一个用于测量宽动态范围的低频信号数字滤波器。它可被设置成4/5个全差分输入通道或8/10个伪差分通道。主通道具有缓冲器和内部缓冲禁止功能。缓冲输入通道意味着这部分电路可处理较高内阻的信号源,而且可在输入通道前加入模拟RC滤波器(以便滤波噪声和降低射频干扰)。主通道输入范围为%26;#177;20mV"%26;#177;2.56之间可分为8档,使用时可任选一档。这些通道用于转换直接来自传感器的信号,且没有外部信号条件要求。内部缓冲禁止时,可以采用外部缓冲。当内部缓冲器使能时,必须对负输入通道进行100mV的补偿,以解决缓冲器内共模输入范围有限的问题。辅助通道用于接收辅助信号的输入,此通道无缓冲器,只有一个固定有%26;#177;2.56V的增益范围。

由于ADuC845的两个A/D通道都采用Δ-∑转换技术,因而可实现24位无失码的优良性能。器件工作时,先由Δ-∑调制器将输入采样信号转换成数字脉冲串,脉冲串的工作周期包含了数字信息。然后采用Sinc3可编程低通滤波器对调制器的输出数据流进行10中抽1,以得到按可编程数据输出率从5.35Hz"105.03Hz给出的有效数据转换结果。ADuC845对调制器信号流有抽取使能和抽取禁止两种操作模式。ADCMODE寄存器内的CHOP位控制抽取操作的使能和禁止。

AD通道的设置和控制是通过专用寄存器块(SFR)中的一组寄存器来实现的。其名称以及功能如下:

ADCSTAT:状态寄存器。保持主通道和辅助通道的一般状态,包括数据准备就绪、校准状态和一些出错信号。

ADCMODE:模式寄存器。控制主通道和辅助通道的操作模式。

ADC0CON1:主通道控制寄存器1。控制主通道的配置,包括主通道的缓冲器、单极和双极译码以及模数转换通道的范围配置等。

ADC0CON2:主通道控制寄存器2。用于控制主通道的配置。

ADC1CON:辅助通道控制寄存器。控制辅助通道的配置,包括辅助通道的参考选择、通道选择及单极和双极译码。

SF:数字滤波器寄存器。通过调节器波器参数来控制主、辅通道数据的更新速率。

ICON:恒流源控制寄存器。允许用户控制片内不同的恒流源。

ADC0L/M/H:用于存放主通道的24位转换结果;

ADC1L/H:用于存放辅助通道的24位转换结果。

OF0L/M/H:用于存放主通道偏移校准系数;

OF1L/H:用于存放辅助通道偏移校准系数;

GN0L/M/H:用于存放主通道增益校准系数。

GN1LH:用于存放辅助通道增益校准系数。

4.2 ADuC845中的存储器

ADuC845为设计者提供了2个闪速/电擦除存储器阵列,即片内62kB闪速/电擦除程序存储器和片内4kB闪速/电擦除数据存储器,并具有256B通用RAM及2kB内部XRAM。

a.闪速/电擦除程序存储器

ADuC845包含一个64k字节闪速/电擦除程序存储器。其中低62k字节供用户使用,可用作程序存储器或附加NV数据存储器。高2k字节包含一个水久嵌入的固件,允许在线串行下载、串行调试和非嵌入性单引脚竞争。此固件也包含一个上电配置程序,该程序将工厂标准系数下载到各种标准外设内,如ADC、温度传感器、电流源等。这2k字节的固件隐藏在用户代码中,若对此空间进行读操作的结果为0,则用户代码出现NOP指令。在上电或硬件复位过程中,当EA引脚接至高电平时,存储器默认从内部62kB的内速/电擦除程序空间都代码的执行变得容易,无需任何外部分离的ROM器件。程序存储器可使用串行下载模式、常规的第三方提供的存储器编程器或用户在用户下载模式中定义的协议进行在线编程。正常模式下,可用两种方式编程,即:

(1)串行下载(在线编程)

ADuC845可方便地通过标准UART串行口下载程序代码。如果PSEN引脚通过外部1kΩ下拉电阻被拉至低电平,则在复位和上电后,ADuC845可进入串行下载模式。一旦处于此模式,隐藏的嵌入式下载内核开始工作,用户可以把代码下载到程序存储器,同时器件仍位于其目标应用硬件中。PC串行下载的可执行程序是作为ADuC845 QiuckStart开发系统的一部分提供的。

(2)并行编程

并行编程模式与常规的第三方闪速或EEPROM器件编程完全兼容。在此模式下,P0和P2口用作外部地址总线接口,P3口用作外部数据总线接口。P1.0用作写使能选通,P1.1"P1.4端口用作通用配置口,在并行编程期间,它可伙各种编程和擦除操作进行配置。

ADuC845具有片内加密特性,可提供三种安全模式。这些模式可被独立激活,以防止程序存储空间被自由读取。三种安全模式如下:

*加锁模式

该模式可锁存代码存储器,禁止程序存储器的并行编程,但允许在并行模式下下对此存储器进行读操作,或者通过外部存储器的MOVC命令对其进行读操作。在串行下载或并行编程模式下,通过启动“擦除代码及数据”命令使此模式无效。

*加密模式

该模式能锁存代码存储器,禁止程序存储器的并行编程,且不允许在并行模式下读/校验程序存储器或通过外部存储器的MOVC命令对内部存储器进行读操作。在串行下载或并行编程模式下,通过启动“擦除代码及数据”命令可使此模式无效。

*串行安全模式

该模式禁止串行下载代码。如果串行安全模式被激活,且试图将存储器在PSEN引脚为低电平时复位到串行下载模式,则存储器将此复位仅看作正常复位,因此,它将不会进入串行下载模式,而仅执行一个正常复位程序。在并行编程模式下,使用“擦除代码和数据”命令时,此模式无效。

b.闪速/电擦除数据存储器

闪速/电擦除数据存储器容量为4kB,它被配置为1024页,每页4个字节。它和其它外围设备一样,可通过是映射到SFR空间的寄存器组与此存储器空间相接。4个数据寄存器组(EDATA1"EDATA4)用于保存4B页数据。页寻址是通过EADRH和EADRL两个寄存器实现的。ECON是一个8位控制寄存器,这可写入9个闪速/电擦除存储器访问命令之一,以使能各种读、写、擦除和校验模式。

此存储器可用作通用非易失性缓存区,分别是高128RAM和低128B RAM。低128B RAM可通过直接或间接寻址访问,而高128B RAM只能通过间接寻址访问,原因在于它与只能通过直接寻址访问的SFR共用同一地址空间。内部数据存储器的低128字节映射中,最低的32字节分为4个区,每区含8个寄存器,编号为R0"R7。寄存器区分紧接的16字节(128位)构成了位可寻址的存储器空间块,位地址00H"07H。堆栈可位于内部存储器地址空间的任一位置,其深度可扩展到2048字节。复位初始化堆栈指针到07H。由于装载堆栈前访问或压入地址已加1的SP,因此,装载堆栈从08H开始,即从R0寄存器开始。若使用不止一个寄存器块,则堆栈指针必须被初始化到RAM区而不是用于数据保存。

d.内部XRAM

ADuC845包含一个2k字节的片内扩展数字存储器。此存储器通过MOVX指令访问。若CFG845.0位被置位,则2k字节的内部XRAM被映射到2k字节外部地址空间的底部,否则半对外部数据存储器进行访问,其方式就和标准8051一样。一旦24位DPTR溢出0007FFH,此时即便CFG845.0位被置位,系统仍可外部数据存储器进行访问。当访问内部XARM时,P0、P2引脚及RD、WR选通在每个标准8051 MOVX指令执行时将不被输出,这就允许应用将这些引脚用作标准I/O。内部XRAM的高1792字节配置为外扩的11位堆栈指地。缺省设置时,堆栈的操作同8052一样,还通用RAM内从FF到00H翻转。但在ADuC845上,通过设置CFG845.7可以使能11位的外扩堆栈指针,这种情况下,堆栈将在RAM内的FFH到XRAM内的0100H之间翻转。

4.3 串行I/O口

ADuC845具有三种串行输入/输出接口:通用串行异步接口、串行外设接口(SPI)和I2C串行接口。这里仅介绍后两种。

(1) SPI串行接口

ADuC845片内集成了一个完整的串行外设接口(SPI)。SPI是工业标准的同步串行接口,它允许8位数据同时同步地被发送和接收。需要注意的是,SPI引脚与P2引脚复用。只用SPE被置位时,复用的引脚才具有SPI功能。否则,随着SPI被清零,这些引脚将保持标准的P2口功能。该系统可配置为主、从两种操作,并由标准的4引脚组成:

SCLOCK:主机的串行时钟线,通过MOSI和MISO数据线同步传输和接收数据。每个SCLOCK周期传输和接收一个单数据位。发送/接收1B的数据需要8个SCLOCK周期。SCLOCK引脚在主模式下配置为输出,在从模式下配置为输入。主模式下,时钟的波特率、极性和相位可由SPICON来设置。

MISO:主机输入/从机输出引脚。设计时应将主机的MISO端口与从机的MISO端口相连以进行高位在前的数据交换。

MOSI:主机输出/从机输入引脚。主机的MISO应与从机的MISO相连以进行高位在前的数据交换。

MOSI:主机输出/从机输入引脚。主机的MISO应与从机的MISO相连以进行高位在前的数据交换。

SS:从机选择引脚,低电平有效。当SS引脚为低电平时,数据仅在从模式下接收和发送,这允许ADuC845用于单主机、多从机的SPI配置。

(2)I2C串行接口

ADuC845支持完全的I2C串行接口。此接口可配置为软件主操作和硬件从操作模式。I2C接口可同时用作SPI接口,它可供用户使用且其不与芯片上使用其它I/O口复用,这就意味着ADuC845芯片片上任何其它I/O口复用,这就意味着ADuC845芯片上的I2C接口和SPI接口可同时使用。当使用I2C接口时,由于他们都使用同一中断程序,在有中断产生时,必须查询接口以确定是哪一个接口触发职断服务程序请求。该接口使用如下两个引脚:

SDATA:数据I/O;

SCLK:串行时钟;

控制I2C接口的寄存器及其功能如下:

I2CCOM:I2C控制寄存器;

I2CADD:保存一个用于I2C接口的外设地址;

I2CADD1:保存一个用于I2C接口的外设地址;

I2CDAT:传输数据或读接收到的数据。访问I2CDAT可自动清除任一未处理的I2C中断和I2CCON SFR中的I2CI位。在每个中断周期内,用户代码仅能访问I2CDAT一次。

5 结束语

ADI公司的ADuC845集成了精密数据转换器、闪存和可编程微控制器,非常适合工业和仪器仪表应用中要求精确测量宽动态范围低频信号的应用场合,例如智能传感器、温度与压力传感器、称重仪、便携式仪器、电池供电系统、4"20mA控制环路和病人监护系统等。此外,该器件在主ADC和辅助ADC都采用了ADI公司的高频“斩波”专利技术,可以提供优良有直流(DC)失调和失调漂移指标,故其也非常适合于低温漂且对噪声抑制和抗电磁干扰能力要求较高的应用场合。

上一篇:针对音视频应用的新型模拟器件及综述

下一篇:制备超低静态电流电荷泵

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 LT1457IN8

LT1457IN8

京公网安备 11010802033920号

京公网安备 11010802033920号