摘 要:本文采用锁相环开环传输函数波特图对三阶电荷泵锁相环进行了系统级设计,并且对相位裕度与建立时间,稳定性与环路带宽这两对矛盾进行了权衡。然后在SIMULINK中建立了包含电荷泵锁相环离散时间特性和非线性本质的行为模型,并进行了仿真验证。

关键词:电荷泵锁相环; 时钟合成器; 波特图; 行为模型

[b]引言

[/b] 锁相环是现代通信系统中的关键模块,通常集成在系统芯片上,其主要应用领域为:数据通信中的时钟与数据恢复、无线通信中的频率合成器、微处理器中的时钟合成与同步等。电荷泵锁相环是当今最流行的锁相环结构,为了减小压控振荡器控制电压的纹波,它采用了二阶无源环路滤波器,这样就构成了三阶电荷泵锁相环。系统级设计与仿真验证是锁相环设计的第一步和关键的一步。本文对一种用作时钟倍频器的三阶电荷泵锁相环进行了系统级设计与仿真验证,仿真环境采用SIMULINK。

图1 电荷泵锁相环结构

图1 电荷泵锁相环结构

图2 相位域模型

图2 相位域模型

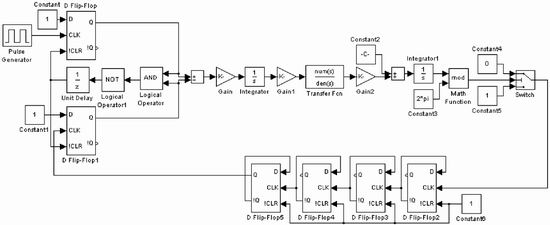

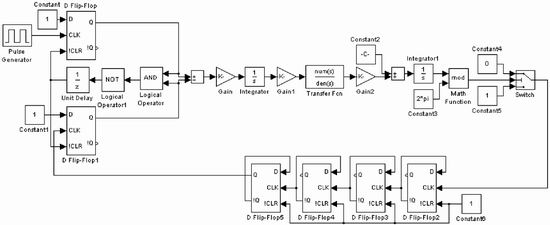

图3 电荷泵锁相环行为模型

[b]电荷泵锁相环的基本原理与设计方法

[/b] 用作时钟倍频器的三阶电荷泵锁相环结构如图1所示,包括由晶体振荡器产生的参考时钟、鉴频鉴相器、电荷泵、环路滤波器、压控振荡器和分频器。鉴频鉴相器比较两个信号的相位与频率差,并产生控制信号给电荷泵,电荷泵相应地给环路滤波器充放电。压控振荡器的输出频率正比于环路滤波器上的控制电压,最终使参考时钟与分频器的输出信号同频同相,即压控振荡器的输出信号频率为参考时钟频率的N倍。

一个电荷泵锁相环的工作过程分为频率牵引过程和相位锁定过程,频率牵引过程是一个完全的非线性过程,相位锁定过程是一个近似的线性过程。电荷泵锁相环本质上是一个离散时间采样的动态系统,当环路带宽远远小于参考时钟频率时,可以采用连续时间近似;当相位误差在鉴频鉴相器的鉴相范围内时,可以采用线性近似。这样,当电荷泵锁相环处于相位锁定过程时,就可以得到一个线性连续时间的相位域模型,如图2所示。其中Kpfdcp是鉴频鉴相器和电荷泵一起构成的鉴相器增益,并有Kpfdcp=Ip/2p,Ip为电荷泵的充放电电流,Kvco为压控振荡器的增益,N为分频器的分频比,F(s)为环路滤波器的传输函数。一阶无源环路滤波器由一个电容C1与一个电阻R1串联构成,二阶无源环路滤波器中再加上一个电容C2与先前的R1C1并联来减小控制电压纹波,从而得:

其中

下面讨论用开环传输函数的波特图对三阶电荷泵锁相环进行系统级设计的方法,由图2可以得到开环传输函数为:

令开环传输函数的单位增益带宽为Wu,为了使开环传输函数在单位增益带宽下的相位裕度最大,设G(s)的零点低于Wu,即Wz=Wu/X;同时设G(s)的极点以相同的比例因子高于Wu,即Wp=XWu,则开环传输函数被改写为:

开环传输函数在单位增益带宽的相位裕度为:

同时得开环传输函数单位增益带宽为:

因此,可以把开环传输函数进一步改写为:

从而得出三阶电荷泵锁相环的闭环传输函数为:

在本文设计的时钟倍频器中,晶振输入的参考时钟频率为25MHz,压控振荡器的输出增益为,电荷泵电流为100mA,分频器的分频比N=16。跟据前面的电路参数,电荷泵锁相环的环路增益相对较高,为了保证电荷泵锁相环的稳定性,并抑制控制电压上的纹波,所以将此时钟倍频器中的三阶电荷泵锁相环设计成窄带锁相环,其开环单位增益带宽为fu=Wu/2p=0.317MHz。同时,为了有相当的开环相位裕度和较快的闭环线性建立时间,取开环传输函数在单位增益带宽的相位裕度,则有X=2.45。 最后得到C1=0.4167nF,C2=0.0833nF和R1=2.88KW。

图3 电荷泵锁相环行为模型

[b]电荷泵锁相环的基本原理与设计方法

[/b] 用作时钟倍频器的三阶电荷泵锁相环结构如图1所示,包括由晶体振荡器产生的参考时钟、鉴频鉴相器、电荷泵、环路滤波器、压控振荡器和分频器。鉴频鉴相器比较两个信号的相位与频率差,并产生控制信号给电荷泵,电荷泵相应地给环路滤波器充放电。压控振荡器的输出频率正比于环路滤波器上的控制电压,最终使参考时钟与分频器的输出信号同频同相,即压控振荡器的输出信号频率为参考时钟频率的N倍。

一个电荷泵锁相环的工作过程分为频率牵引过程和相位锁定过程,频率牵引过程是一个完全的非线性过程,相位锁定过程是一个近似的线性过程。电荷泵锁相环本质上是一个离散时间采样的动态系统,当环路带宽远远小于参考时钟频率时,可以采用连续时间近似;当相位误差在鉴频鉴相器的鉴相范围内时,可以采用线性近似。这样,当电荷泵锁相环处于相位锁定过程时,就可以得到一个线性连续时间的相位域模型,如图2所示。其中Kpfdcp是鉴频鉴相器和电荷泵一起构成的鉴相器增益,并有Kpfdcp=Ip/2p,Ip为电荷泵的充放电电流,Kvco为压控振荡器的增益,N为分频器的分频比,F(s)为环路滤波器的传输函数。一阶无源环路滤波器由一个电容C1与一个电阻R1串联构成,二阶无源环路滤波器中再加上一个电容C2与先前的R1C1并联来减小控制电压纹波,从而得:

其中

下面讨论用开环传输函数的波特图对三阶电荷泵锁相环进行系统级设计的方法,由图2可以得到开环传输函数为:

令开环传输函数的单位增益带宽为Wu,为了使开环传输函数在单位增益带宽下的相位裕度最大,设G(s)的零点低于Wu,即Wz=Wu/X;同时设G(s)的极点以相同的比例因子高于Wu,即Wp=XWu,则开环传输函数被改写为:

开环传输函数在单位增益带宽的相位裕度为:

同时得开环传输函数单位增益带宽为:

因此,可以把开环传输函数进一步改写为:

从而得出三阶电荷泵锁相环的闭环传输函数为:

在本文设计的时钟倍频器中,晶振输入的参考时钟频率为25MHz,压控振荡器的输出增益为,电荷泵电流为100mA,分频器的分频比N=16。跟据前面的电路参数,电荷泵锁相环的环路增益相对较高,为了保证电荷泵锁相环的稳定性,并抑制控制电压上的纹波,所以将此时钟倍频器中的三阶电荷泵锁相环设计成窄带锁相环,其开环单位增益带宽为fu=Wu/2p=0.317MHz。同时,为了有相当的开环相位裕度和较快的闭环线性建立时间,取开环传输函数在单位增益带宽的相位裕度,则有X=2.45。 最后得到C1=0.4167nF,C2=0.0833nF和R1=2.88KW。

图4 输入相位阶跃时的波形

图4 输入相位阶跃时的波形

图5 输入频率阶跃时的波形

电荷泵锁相环在SIMULINK中的建模与仿真

为了对所设计的三阶电荷泵锁相环进行系统级验证并分析其动态特性,本文在通用的仿真环境SIMULINK中建立了其行为模型,并进行了动态特性的仿真验证。

整个用作时钟生成器的三阶电荷泵锁相环在SIMULINK中的行为模型如图3所示,其中鉴频鉴相器由两个带使能的D触发器、一个与运算、一个非运算和一个延迟单元组成,两个D触发器的Q输出端一方面作为控制信号up、down传送给电荷泵,另一方面作为反馈信号产生与运算的复位信号;用一个脉冲发生器来代替参考时钟,并与一个D触发器的CLK端相连,另一个D触发器的CLK端接分频器的输出信号。

电荷泵被模拟为一个减运算和一个增益级,增益级的增益为电荷泵的电流。二阶无源环路滤波器被模拟为一个积分环节、一个增益级和一个传输函数环节,相应的参数由环路滤波器的传输函数F(s)确定。压控振荡器被模拟为一个增益级、一个相加运算、一个积分环节、一个模2p运算和一个开关环节,其中增益级的增益为压控振荡器的增益Kvco,相加运算的另一输入端接的恒量是压控振荡器的中心频率,积分环节将频率变为相位,模2p运算把相位信号变为周期为2p的锯齿波信号,开关环节再把周期为2p的锯齿波信号变为方波时钟信号。分频器由四个异步二分频器级连而成,每个异步二分频器均是由!Q端与D端相连的D触发器构成。

图3所示的三阶电荷泵锁相环行为模型完全能够模拟电荷泵锁相环的离散采样本质和非线性本质,这样就可以通过仿真来得到比较接近实际情形的电荷泵锁相环动态特性,并验证采用线性连续时间近似理论所设计的电荷泵锁相环。图4是参考输入信号发生相位阶跃时环路滤波器输出电压的波形,此波形非常类似于将三阶电荷泵锁相环近似处理为线性连续时间系统时所得的瞬态响应,由图4可以得到:建立时间tsettle=6ms。图5是参考输入信号发生5MHz频率阶跃时环路滤波器输出电压的波形,从起始时刻到波形第一次达到稳态值的时刻为频率牵引过程,由图可知频率牵引过程是一个完全的非线性过程,时间为7.3ms;此后是相位锁定过程,是一个近似的线性过程,时间为5.7ms。

[b]结语

[/b] 本文采用锁相环开环传输函数波特图对三阶电荷泵锁相环进行了系统级设计,并用SIMULINK进行了仿真验证,对锁相环设计中的相位裕度与建立时间,稳定性与环路带宽这两对矛盾进行了很好的权衡。

[url=http://www.eaw.com.cn/UploadFiles/2005-7/200572010554197.jpg]文章相关公式下载[/url]

参考文献

1 Behzad Razavi. Design of Analog CMOS Integrated Circuits.McGraw-Hill,2001

2 F. M. Gardner. Charge-pump phase-lock loops. IEEE Trans. Commun.,Nov.1980

3 Cicero S. Vaucher. An Adaptive PLL Tuning System Architecture Combining High Spectral Purity and Fast Settling Time. IEEE J.Solid-State Circuits,April 2000

图5 输入频率阶跃时的波形

电荷泵锁相环在SIMULINK中的建模与仿真

为了对所设计的三阶电荷泵锁相环进行系统级验证并分析其动态特性,本文在通用的仿真环境SIMULINK中建立了其行为模型,并进行了动态特性的仿真验证。

整个用作时钟生成器的三阶电荷泵锁相环在SIMULINK中的行为模型如图3所示,其中鉴频鉴相器由两个带使能的D触发器、一个与运算、一个非运算和一个延迟单元组成,两个D触发器的Q输出端一方面作为控制信号up、down传送给电荷泵,另一方面作为反馈信号产生与运算的复位信号;用一个脉冲发生器来代替参考时钟,并与一个D触发器的CLK端相连,另一个D触发器的CLK端接分频器的输出信号。

电荷泵被模拟为一个减运算和一个增益级,增益级的增益为电荷泵的电流。二阶无源环路滤波器被模拟为一个积分环节、一个增益级和一个传输函数环节,相应的参数由环路滤波器的传输函数F(s)确定。压控振荡器被模拟为一个增益级、一个相加运算、一个积分环节、一个模2p运算和一个开关环节,其中增益级的增益为压控振荡器的增益Kvco,相加运算的另一输入端接的恒量是压控振荡器的中心频率,积分环节将频率变为相位,模2p运算把相位信号变为周期为2p的锯齿波信号,开关环节再把周期为2p的锯齿波信号变为方波时钟信号。分频器由四个异步二分频器级连而成,每个异步二分频器均是由!Q端与D端相连的D触发器构成。

图3所示的三阶电荷泵锁相环行为模型完全能够模拟电荷泵锁相环的离散采样本质和非线性本质,这样就可以通过仿真来得到比较接近实际情形的电荷泵锁相环动态特性,并验证采用线性连续时间近似理论所设计的电荷泵锁相环。图4是参考输入信号发生相位阶跃时环路滤波器输出电压的波形,此波形非常类似于将三阶电荷泵锁相环近似处理为线性连续时间系统时所得的瞬态响应,由图4可以得到:建立时间tsettle=6ms。图5是参考输入信号发生5MHz频率阶跃时环路滤波器输出电压的波形,从起始时刻到波形第一次达到稳态值的时刻为频率牵引过程,由图可知频率牵引过程是一个完全的非线性过程,时间为7.3ms;此后是相位锁定过程,是一个近似的线性过程,时间为5.7ms。

[b]结语

[/b] 本文采用锁相环开环传输函数波特图对三阶电荷泵锁相环进行了系统级设计,并用SIMULINK进行了仿真验证,对锁相环设计中的相位裕度与建立时间,稳定性与环路带宽这两对矛盾进行了很好的权衡。

[url=http://www.eaw.com.cn/UploadFiles/2005-7/200572010554197.jpg]文章相关公式下载[/url]

参考文献

1 Behzad Razavi. Design of Analog CMOS Integrated Circuits.McGraw-Hill,2001

2 F. M. Gardner. Charge-pump phase-lock loops. IEEE Trans. Commun.,Nov.1980

3 Cicero S. Vaucher. An Adaptive PLL Tuning System Architecture Combining High Spectral Purity and Fast Settling Time. IEEE J.Solid-State Circuits,April 2000

编辑: 引用地址:三阶电荷泵锁相环系统级设计与仿真验证

图1 电荷泵锁相环结构

图1 电荷泵锁相环结构

图2 相位域模型

图2 相位域模型

图3 电荷泵锁相环行为模型

[b]电荷泵锁相环的基本原理与设计方法

[/b] 用作时钟倍频器的三阶电荷泵锁相环结构如图1所示,包括由晶体振荡器产生的参考时钟、鉴频鉴相器、电荷泵、环路滤波器、压控振荡器和分频器。鉴频鉴相器比较两个信号的相位与频率差,并产生控制信号给电荷泵,电荷泵相应地给环路滤波器充放电。压控振荡器的输出频率正比于环路滤波器上的控制电压,最终使参考时钟与分频器的输出信号同频同相,即压控振荡器的输出信号频率为参考时钟频率的N倍。

一个电荷泵锁相环的工作过程分为频率牵引过程和相位锁定过程,频率牵引过程是一个完全的非线性过程,相位锁定过程是一个近似的线性过程。电荷泵锁相环本质上是一个离散时间采样的动态系统,当环路带宽远远小于参考时钟频率时,可以采用连续时间近似;当相位误差在鉴频鉴相器的鉴相范围内时,可以采用线性近似。这样,当电荷泵锁相环处于相位锁定过程时,就可以得到一个线性连续时间的相位域模型,如图2所示。其中Kpfdcp是鉴频鉴相器和电荷泵一起构成的鉴相器增益,并有Kpfdcp=Ip/2p,Ip为电荷泵的充放电电流,Kvco为压控振荡器的增益,N为分频器的分频比,F(s)为环路滤波器的传输函数。一阶无源环路滤波器由一个电容C1与一个电阻R1串联构成,二阶无源环路滤波器中再加上一个电容C2与先前的R1C1并联来减小控制电压纹波,从而得:

其中

下面讨论用开环传输函数的波特图对三阶电荷泵锁相环进行系统级设计的方法,由图2可以得到开环传输函数为:

令开环传输函数的单位增益带宽为Wu,为了使开环传输函数在单位增益带宽下的相位裕度最大,设G(s)的零点低于Wu,即Wz=Wu/X;同时设G(s)的极点以相同的比例因子高于Wu,即Wp=XWu,则开环传输函数被改写为:

开环传输函数在单位增益带宽的相位裕度为:

同时得开环传输函数单位增益带宽为:

因此,可以把开环传输函数进一步改写为:

从而得出三阶电荷泵锁相环的闭环传输函数为:

在本文设计的时钟倍频器中,晶振输入的参考时钟频率为25MHz,压控振荡器的输出增益为,电荷泵电流为100mA,分频器的分频比N=16。跟据前面的电路参数,电荷泵锁相环的环路增益相对较高,为了保证电荷泵锁相环的稳定性,并抑制控制电压上的纹波,所以将此时钟倍频器中的三阶电荷泵锁相环设计成窄带锁相环,其开环单位增益带宽为fu=Wu/2p=0.317MHz。同时,为了有相当的开环相位裕度和较快的闭环线性建立时间,取开环传输函数在单位增益带宽的相位裕度,则有X=2.45。 最后得到C1=0.4167nF,C2=0.0833nF和R1=2.88KW。

图3 电荷泵锁相环行为模型

[b]电荷泵锁相环的基本原理与设计方法

[/b] 用作时钟倍频器的三阶电荷泵锁相环结构如图1所示,包括由晶体振荡器产生的参考时钟、鉴频鉴相器、电荷泵、环路滤波器、压控振荡器和分频器。鉴频鉴相器比较两个信号的相位与频率差,并产生控制信号给电荷泵,电荷泵相应地给环路滤波器充放电。压控振荡器的输出频率正比于环路滤波器上的控制电压,最终使参考时钟与分频器的输出信号同频同相,即压控振荡器的输出信号频率为参考时钟频率的N倍。

一个电荷泵锁相环的工作过程分为频率牵引过程和相位锁定过程,频率牵引过程是一个完全的非线性过程,相位锁定过程是一个近似的线性过程。电荷泵锁相环本质上是一个离散时间采样的动态系统,当环路带宽远远小于参考时钟频率时,可以采用连续时间近似;当相位误差在鉴频鉴相器的鉴相范围内时,可以采用线性近似。这样,当电荷泵锁相环处于相位锁定过程时,就可以得到一个线性连续时间的相位域模型,如图2所示。其中Kpfdcp是鉴频鉴相器和电荷泵一起构成的鉴相器增益,并有Kpfdcp=Ip/2p,Ip为电荷泵的充放电电流,Kvco为压控振荡器的增益,N为分频器的分频比,F(s)为环路滤波器的传输函数。一阶无源环路滤波器由一个电容C1与一个电阻R1串联构成,二阶无源环路滤波器中再加上一个电容C2与先前的R1C1并联来减小控制电压纹波,从而得:

其中

下面讨论用开环传输函数的波特图对三阶电荷泵锁相环进行系统级设计的方法,由图2可以得到开环传输函数为:

令开环传输函数的单位增益带宽为Wu,为了使开环传输函数在单位增益带宽下的相位裕度最大,设G(s)的零点低于Wu,即Wz=Wu/X;同时设G(s)的极点以相同的比例因子高于Wu,即Wp=XWu,则开环传输函数被改写为:

开环传输函数在单位增益带宽的相位裕度为:

同时得开环传输函数单位增益带宽为:

因此,可以把开环传输函数进一步改写为:

从而得出三阶电荷泵锁相环的闭环传输函数为:

在本文设计的时钟倍频器中,晶振输入的参考时钟频率为25MHz,压控振荡器的输出增益为,电荷泵电流为100mA,分频器的分频比N=16。跟据前面的电路参数,电荷泵锁相环的环路增益相对较高,为了保证电荷泵锁相环的稳定性,并抑制控制电压上的纹波,所以将此时钟倍频器中的三阶电荷泵锁相环设计成窄带锁相环,其开环单位增益带宽为fu=Wu/2p=0.317MHz。同时,为了有相当的开环相位裕度和较快的闭环线性建立时间,取开环传输函数在单位增益带宽的相位裕度,则有X=2.45。 最后得到C1=0.4167nF,C2=0.0833nF和R1=2.88KW。

图4 输入相位阶跃时的波形

图4 输入相位阶跃时的波形

图5 输入频率阶跃时的波形

电荷泵锁相环在SIMULINK中的建模与仿真

为了对所设计的三阶电荷泵锁相环进行系统级验证并分析其动态特性,本文在通用的仿真环境SIMULINK中建立了其行为模型,并进行了动态特性的仿真验证。

整个用作时钟生成器的三阶电荷泵锁相环在SIMULINK中的行为模型如图3所示,其中鉴频鉴相器由两个带使能的D触发器、一个与运算、一个非运算和一个延迟单元组成,两个D触发器的Q输出端一方面作为控制信号up、down传送给电荷泵,另一方面作为反馈信号产生与运算的复位信号;用一个脉冲发生器来代替参考时钟,并与一个D触发器的CLK端相连,另一个D触发器的CLK端接分频器的输出信号。

电荷泵被模拟为一个减运算和一个增益级,增益级的增益为电荷泵的电流。二阶无源环路滤波器被模拟为一个积分环节、一个增益级和一个传输函数环节,相应的参数由环路滤波器的传输函数F(s)确定。压控振荡器被模拟为一个增益级、一个相加运算、一个积分环节、一个模2p运算和一个开关环节,其中增益级的增益为压控振荡器的增益Kvco,相加运算的另一输入端接的恒量是压控振荡器的中心频率,积分环节将频率变为相位,模2p运算把相位信号变为周期为2p的锯齿波信号,开关环节再把周期为2p的锯齿波信号变为方波时钟信号。分频器由四个异步二分频器级连而成,每个异步二分频器均是由!Q端与D端相连的D触发器构成。

图3所示的三阶电荷泵锁相环行为模型完全能够模拟电荷泵锁相环的离散采样本质和非线性本质,这样就可以通过仿真来得到比较接近实际情形的电荷泵锁相环动态特性,并验证采用线性连续时间近似理论所设计的电荷泵锁相环。图4是参考输入信号发生相位阶跃时环路滤波器输出电压的波形,此波形非常类似于将三阶电荷泵锁相环近似处理为线性连续时间系统时所得的瞬态响应,由图4可以得到:建立时间tsettle=6ms。图5是参考输入信号发生5MHz频率阶跃时环路滤波器输出电压的波形,从起始时刻到波形第一次达到稳态值的时刻为频率牵引过程,由图可知频率牵引过程是一个完全的非线性过程,时间为7.3ms;此后是相位锁定过程,是一个近似的线性过程,时间为5.7ms。

[b]结语

[/b] 本文采用锁相环开环传输函数波特图对三阶电荷泵锁相环进行了系统级设计,并用SIMULINK进行了仿真验证,对锁相环设计中的相位裕度与建立时间,稳定性与环路带宽这两对矛盾进行了很好的权衡。

[url=http://www.eaw.com.cn/UploadFiles/2005-7/200572010554197.jpg]文章相关公式下载[/url]

参考文献

1 Behzad Razavi. Design of Analog CMOS Integrated Circuits.McGraw-Hill,2001

2 F. M. Gardner. Charge-pump phase-lock loops. IEEE Trans. Commun.,Nov.1980

3 Cicero S. Vaucher. An Adaptive PLL Tuning System Architecture Combining High Spectral Purity and Fast Settling Time. IEEE J.Solid-State Circuits,April 2000

图5 输入频率阶跃时的波形

电荷泵锁相环在SIMULINK中的建模与仿真

为了对所设计的三阶电荷泵锁相环进行系统级验证并分析其动态特性,本文在通用的仿真环境SIMULINK中建立了其行为模型,并进行了动态特性的仿真验证。

整个用作时钟生成器的三阶电荷泵锁相环在SIMULINK中的行为模型如图3所示,其中鉴频鉴相器由两个带使能的D触发器、一个与运算、一个非运算和一个延迟单元组成,两个D触发器的Q输出端一方面作为控制信号up、down传送给电荷泵,另一方面作为反馈信号产生与运算的复位信号;用一个脉冲发生器来代替参考时钟,并与一个D触发器的CLK端相连,另一个D触发器的CLK端接分频器的输出信号。

电荷泵被模拟为一个减运算和一个增益级,增益级的增益为电荷泵的电流。二阶无源环路滤波器被模拟为一个积分环节、一个增益级和一个传输函数环节,相应的参数由环路滤波器的传输函数F(s)确定。压控振荡器被模拟为一个增益级、一个相加运算、一个积分环节、一个模2p运算和一个开关环节,其中增益级的增益为压控振荡器的增益Kvco,相加运算的另一输入端接的恒量是压控振荡器的中心频率,积分环节将频率变为相位,模2p运算把相位信号变为周期为2p的锯齿波信号,开关环节再把周期为2p的锯齿波信号变为方波时钟信号。分频器由四个异步二分频器级连而成,每个异步二分频器均是由!Q端与D端相连的D触发器构成。

图3所示的三阶电荷泵锁相环行为模型完全能够模拟电荷泵锁相环的离散采样本质和非线性本质,这样就可以通过仿真来得到比较接近实际情形的电荷泵锁相环动态特性,并验证采用线性连续时间近似理论所设计的电荷泵锁相环。图4是参考输入信号发生相位阶跃时环路滤波器输出电压的波形,此波形非常类似于将三阶电荷泵锁相环近似处理为线性连续时间系统时所得的瞬态响应,由图4可以得到:建立时间tsettle=6ms。图5是参考输入信号发生5MHz频率阶跃时环路滤波器输出电压的波形,从起始时刻到波形第一次达到稳态值的时刻为频率牵引过程,由图可知频率牵引过程是一个完全的非线性过程,时间为7.3ms;此后是相位锁定过程,是一个近似的线性过程,时间为5.7ms。

[b]结语

[/b] 本文采用锁相环开环传输函数波特图对三阶电荷泵锁相环进行了系统级设计,并用SIMULINK进行了仿真验证,对锁相环设计中的相位裕度与建立时间,稳定性与环路带宽这两对矛盾进行了很好的权衡。

[url=http://www.eaw.com.cn/UploadFiles/2005-7/200572010554197.jpg]文章相关公式下载[/url]

参考文献

1 Behzad Razavi. Design of Analog CMOS Integrated Circuits.McGraw-Hill,2001

2 F. M. Gardner. Charge-pump phase-lock loops. IEEE Trans. Commun.,Nov.1980

3 Cicero S. Vaucher. An Adaptive PLL Tuning System Architecture Combining High Spectral Purity and Fast Settling Time. IEEE J.Solid-State Circuits,April 2000

嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练 UA748HC

UA748HC

京公网安备 11010802033920号

京公网安备 11010802033920号