0 引言

锁相(Phase Lock)技术是一种相位负反馈频率控制技术,该技术在锁定时无剩余频差,并具有良好的窄带载波跟踪性能和带宽调制跟踪性能,而且对相位噪声和杂散也具有很好的抑制作用。因此,通过锁相频率合成技术实现的频率源已在通信、电视等领域得了广泛应用。本文介绍的ADl公司的ADF4360系列芯片就是用于无线通信射频系统(GSM,DECT,PCS,WCDMA。DCS)基站和WLAN混频电路的一款性价比很高,且应用范围较广的锁相芯片。

1 ADF4360_4的性能特点

ADF4360_4丰要由数字鉴相器、电荷泵、R分频器、A,B计数器及双模前置P/P+1分频器等组成。数字鉴相器对R计数器与N计数器的输出信号进行相位比较,得到一个误差电压。14bit可编程参考R分频器对外部晶振分频后得到参考频率。该器件可以通过可编程6位A计数器、13位B计数器及双模前置分频器(P/P+1)来共同完成主分频比N (N=BP+A)。因此,设计时只需外加环路滤波器,并选择合适的参考值,即可获得稳定的频率输出,其输出频率为:

f0=fvco=N (fi/R)

式中,fi为参考频率,它可由高稳定度晶体振荡器提供。而其鉴相频率fr为:

fr=fi/R

其中,fi应小于8 MHz。

ADF4360_4是美国ADI公司生产的的高性能锁相频率合成芯片,主要用于无线发射机和接收机中为上下变频提供本振信号。该器件的主要特点如下:

(1)该合成器的输出频率范围为1450~1750MHz;并可选择二分频。选择二分频时,可输出725~875 MHz的频率信号;

(2)工作电压为3~3.6 V;

(3)合成器的输出信号的功率可控制范围为-13~-4 dbm;

(4)可编程双模前置分频器的分频比为8/9、16/17、32/33等;

(5)能够进行模拟和数字锁定检测;

(6)芯片内部集成又VCO。

ADF4360_4是一款双模前置分频型单环频率合成器,该器件可在不改变频率分辨率的同时,有效地提高频率合成器的输山频率。图1所示是一个双模前置型锁相频率合成器的工作原理方框图。

在图1所示的器件结构中, (P+1)/P为高速双模前置分频器,其分频模数为P+1和P,此外,系统中的A为脉冲吞咽可编程计数器;B为主可编程计数器;MC为模控制逻辑电路。

双模前置分频器通常只有两个计数工作模式,但工作时只要一个模控制信号就可以实现简单的换模计数工作,而不需要采用类似可编程分频器那样复杂的预置操作,因而其工作频率可以做得像固定分频器那样高。事实上,双模前置分频器可以很好地解决固定前置分频器提高输出频率f0和降低频率分辨率△f 0的矛盾。

2 ADF4360_4的应用电路

利用锁相环频率合成器件设计的本振源能为混频电路提供良好的本振载波。图2所示是利用ADF460_4作为混频器本振源的具体电路。电路中的外部晶振为20 MHz的高稳定度晶体振荡器。该电路可将来自AP的2.4 GHz信号下变换到950MHz,以供WLAN中的混频器使用,并最终使信号可以在特定的电缆上传输。

本电路用ADF4360_4来产生1.5 GHz的本地振荡信号(LO)。电路中的晶体振荡器不仅要给ADF4360_4提供参考频率,还要给控制ADF4360_4的FPGA芯片提供时钟。使用时,该晶振应接到ADF4360_4的参考时钟输入引脚CLK_ref,且其内部电荷泵输出引脚CP(ChargePump)与VCO输出引脚VTUNE之间还应接入环路滤波电路。

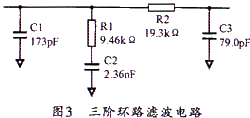

图3所示是一个三阶环路滤波电路,在该电路中,PFD的相位检测频率fr为200 kHz,相位裕量为φP。由于系统外接的晶体振荡器的频率源为20 MHz,所以,可以据此计算出其参考分频比R为100。事实上,在设计时,可以利用ADI公司提供的ADIsimPLL工具计算出三阶环路滤波器的元件参数如下:

R1=9.46 kΩ,C1=173 pF,C2=2.36 nF,R2=19.3 kΩ,C3=79 pF。

3 ADF4360_4的FPGA初始化

每次给ADF4360_4加电时,都必须给内部数字寄存器写入一定的值才能获得需要的本振输出。而每次掉电后,原来写入内部数字寄存器的值也随之消失。所以,设计时可用FPGA控制板来写入数据。FPGA可选用ALTERA公司的EP1C3T100C6芯片,同时也可以外接20MHz的石英晶振来为其提供时钟。FPGA板上设置的5个按键分别为RESET(复位键)、CE(使能键)、R (R输入键)、C(C输入键)和N(N输入键)。EP1C3T100C6的双向I/O口77、78、79分别接ADF4360_4的LE、DATA、CLK,其中CLK为串行时钟输入,DATA为串行数据输入,LE为加载使能,该位为逻辑“1”时表示加载,LE由FPGA板子上的CE使能键控制。每次加载数据时。应先按RESET键复位,然后按CE使能键。这样,当FP-GA板和ADF4360_4连通后,即可传输数据,然后依次按R、C、N以使数据依次写入。

数据输入时,首先由DATA在每个CLK的上升沿从MSB(最高有效位)开始依次写入24位移位寄存器中的数据并一次性锁存到目标寄存器,然后再进行下一个目标寄存器的初始化。目标寄存器的选择可由移位寄存器中的最末两位DB1和DB0来决定。对寄存器赋值的顺序为R-C-N。而且C和N寄存器的赋值间隔应大于5 ms。图4所示为其数据写入时序图。

本系统的数据输入控制程序可用Verilog吾言编写,同时可在Quartus6.0下编写编译并配置芯片管脚。由于本系统的源程序很大,限于篇幅,这里只给出R寄存器赋值的部分代码:

4 结束语

利用锁相频率合成芯片ADF4360_4可为混频电路设计本振信号源。本文给出了用ADF4360-4设计混频器本振信号源的关键参数及设计方法,同时给出了ADF4360_4芯片的控制方法及程序。事实上,利用ADF4360_4锁相频率合成器可在许多通信系统中简化倍频装置和电路结构,降低功耗和设备成本,因而可在射频电路系统(如无线局域网)中得到广泛应用。

上一篇:提高非接触有值IC卡操作的可靠性研究

下一篇:GPS远端定位监控系统的设计

推荐阅读最新更新时间:2024-05-07 15:59

- 高通推出其首款 RISC-V 架构可编程连接模组 QCC74xM,支持 Wi-Fi 6 等协议

- Microchip推出广泛的IGBT 7 功率器件组合,专为可持续发展、电动出行和数据中心应用而设计

- 英飞凌推出新型高性能微控制器AURIX™ TC4Dx

- Rambus宣布推出业界首款HBM4控制器IP,加速下一代AI工作负载

- 恩智浦FRDM平台助力无线连接

- 大联大诠鼎集团推出基于Qualcomm产品的Wi-Fi 7家庭网关方案

- 专访Silicon Labs:深度探讨蓝牙6.0的未来发展趋势

- Works With线上开发者大会即将展开,在线领略全球活动内容精髓

- 智能无处不在:安谋科技“周易”NPU开启端侧AI新时代

GJB 179A-1996 计数抽样检验程序及表

GJB 179A-1996 计数抽样检验程序及表 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号