摘要:介绍了一种超宽带雷达信号波形产生器的设计与实现,信号由DDS+PLL+混频器产生。该产生器采用高性能数字锁相环芯片Q3236、压控振荡器Q3500-0916T和混频器IAM-81008构成核心单元,利用新型低频和超带通滤波器完成超宽带雷达信号。这种超宽带雷达信号的实现对提高现有雷达的性能以及研制新一代高性能雷达都具有重要意义。

关键词:超宽带 直接数字合成 锁相环 混频器 滤波器

1 总体方案的拟定

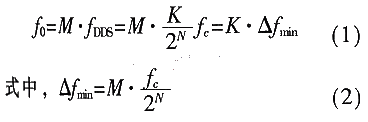

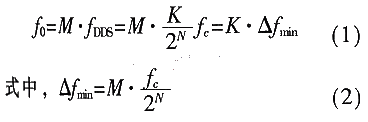

超宽带雷达信号电路方框图如图1所示。它的基本原理是利用参考源DDS的微小频率变化激励锁相环输出频率f0的大范围变化,具体公式如下:

图1

本文以产生160MHz~650MHz的超宽带信号为例,输入的较低频率由DDS产生,输出的较高频率由DDS+PLL+混频器产生,即用3.3MHz的DDS输出信号激励PLL,产生1160MHz~1650MHz信号。该信号与1000MHz本振混频即可产生160MHz~650MHz信号(其中N=32,M=360)。

2 单元电路的选择、设计与仿真

锁相环由Qualcomm公司新推出的高性能数字锁相环芯片Q3236、压控振荡器Q3500C-0916T和抑制滤波器组成,混频器采用HP公司的IAM-81008。放大器中的反馈放大器采用微波单片集成放大器,选用HP公司的INA-02186硅双极MMIC反馈放大器;而线性放大器选用MC10H115,是四个用于整形且通过长线传输不同信号的放大器。本地振荡器采用一个晶振倍频源,倍频至1000MHz,为降低倍频源的输出杂散分量,在输出端进行滤波,以得到频谱纯净的本振源信号。为了缩短频率合成器频率的转换时间,在锁相环路基础上外加快速捕获电路。快速捕获电路是采用频率数字变换辅助捕获方法获得捕获的。

图1

本文以产生160MHz~650MHz的超宽带信号为例,输入的较低频率由DDS产生,输出的较高频率由DDS+PLL+混频器产生,即用3.3MHz的DDS输出信号激励PLL,产生1160MHz~1650MHz信号。该信号与1000MHz本振混频即可产生160MHz~650MHz信号(其中N=32,M=360)。

2 单元电路的选择、设计与仿真

锁相环由Qualcomm公司新推出的高性能数字锁相环芯片Q3236、压控振荡器Q3500C-0916T和抑制滤波器组成,混频器采用HP公司的IAM-81008。放大器中的反馈放大器采用微波单片集成放大器,选用HP公司的INA-02186硅双极MMIC反馈放大器;而线性放大器选用MC10H115,是四个用于整形且通过长线传输不同信号的放大器。本地振荡器采用一个晶振倍频源,倍频至1000MHz,为降低倍频源的输出杂散分量,在输出端进行滤波,以得到频谱纯净的本振源信号。为了缩短频率合成器频率的转换时间,在锁相环路基础上外加快速捕获电路。快速捕获电路是采用频率数字变换辅助捕获方法获得捕获的。

图1中的环路滤波器采用带预积分的有源积分滤波器,如图2所示。

就阻带衰减的陡度而言,以椭圆函数滤波器最好,所以抑制滤波器选择椭圆函数滤波器。在本电路中,参考输入频率为10MHz,参考分频比为3,故鉴频鉴相器输出为3.33MHz。为降低整个频率综合器的杂散噪声和相位噪声,设计时考虑到从0~1.2MHz的范围内衰0.2dB,而3MHz以上的范围衰减大于60dB,最后设计的抑制滤波器如图3所示。其幅频特性如图4所示。

图1中的环路滤波器采用带预积分的有源积分滤波器,如图2所示。

就阻带衰减的陡度而言,以椭圆函数滤波器最好,所以抑制滤波器选择椭圆函数滤波器。在本电路中,参考输入频率为10MHz,参考分频比为3,故鉴频鉴相器输出为3.33MHz。为降低整个频率综合器的杂散噪声和相位噪声,设计时考虑到从0~1.2MHz的范围内衰0.2dB,而3MHz以上的范围衰减大于60dB,最后设计的抑制滤波器如图3所示。其幅频特性如图4所示。

为了达到超带宽,160MHz~650MHz带通滤波器采用电容耦合的节点耦合滤波器进行设计,所设计的滤波器电路如图5所示。

对所设计的带通滤波器用PSPICE进行仿真,其幅频特性(V(R2))如图6所示。

图5

3 系统的连线与测试

在完成上述单元电路器件的选择和设计以后,用PROTEL对电路的PCB板图进行具体布局和布线。在布线的过程中要注意电源的供电、器件的接地和耦合器件间的屏蔽。最后所设计的超宽带雷达信号产生电路的信号产生结果进行仿真。其仿真结果如图7所示。

为了达到超带宽,160MHz~650MHz带通滤波器采用电容耦合的节点耦合滤波器进行设计,所设计的滤波器电路如图5所示。

对所设计的带通滤波器用PSPICE进行仿真,其幅频特性(V(R2))如图6所示。

图5

3 系统的连线与测试

在完成上述单元电路器件的选择和设计以后,用PROTEL对电路的PCB板图进行具体布局和布线。在布线的过程中要注意电源的供电、器件的接地和耦合器件间的屏蔽。最后所设计的超宽带雷达信号产生电路的信号产生结果进行仿真。其仿真结果如图7所示。

通过对系统的测试结果进行分析,电路最终终产生的结果达到了预期的信号形式和工作频率范围内的各项指标要求。

通过对系统的测试结果进行分析,电路最终终产生的结果达到了预期的信号形式和工作频率范围内的各项指标要求。

超宽带高稳定雷达信号产生电路对提高现有雷达的性能以及研制新一代高性能雷达都具有非常重要的意义。它不仅增强雷达的反干扰能力,有效地对付导弹辐射,而且由于其盯对带宽和绝对带宽都比较宽,在雷达成像、雷达目标识别、雷达低仰角跟踪等方面都有重要的应用;它是新一代雷达的关键技术,具有广泛的应用前景。

超宽带高稳定雷达信号产生电路对提高现有雷达的性能以及研制新一代高性能雷达都具有非常重要的意义。它不仅增强雷达的反干扰能力,有效地对付导弹辐射,而且由于其盯对带宽和绝对带宽都比较宽,在雷达成像、雷达目标识别、雷达低仰角跟踪等方面都有重要的应用;它是新一代雷达的关键技术,具有广泛的应用前景。

引用地址:超宽带雷达信号电路的设计与实现

图1

本文以产生160MHz~650MHz的超宽带信号为例,输入的较低频率由DDS产生,输出的较高频率由DDS+PLL+混频器产生,即用3.3MHz的DDS输出信号激励PLL,产生1160MHz~1650MHz信号。该信号与1000MHz本振混频即可产生160MHz~650MHz信号(其中N=32,M=360)。

2 单元电路的选择、设计与仿真

锁相环由Qualcomm公司新推出的高性能数字锁相环芯片Q3236、压控振荡器Q3500C-0916T和抑制滤波器组成,混频器采用HP公司的IAM-81008。放大器中的反馈放大器采用微波单片集成放大器,选用HP公司的INA-02186硅双极MMIC反馈放大器;而线性放大器选用MC10H115,是四个用于整形且通过长线传输不同信号的放大器。本地振荡器采用一个晶振倍频源,倍频至1000MHz,为降低倍频源的输出杂散分量,在输出端进行滤波,以得到频谱纯净的本振源信号。为了缩短频率合成器频率的转换时间,在锁相环路基础上外加快速捕获电路。快速捕获电路是采用频率数字变换辅助捕获方法获得捕获的。

图1

本文以产生160MHz~650MHz的超宽带信号为例,输入的较低频率由DDS产生,输出的较高频率由DDS+PLL+混频器产生,即用3.3MHz的DDS输出信号激励PLL,产生1160MHz~1650MHz信号。该信号与1000MHz本振混频即可产生160MHz~650MHz信号(其中N=32,M=360)。

2 单元电路的选择、设计与仿真

锁相环由Qualcomm公司新推出的高性能数字锁相环芯片Q3236、压控振荡器Q3500C-0916T和抑制滤波器组成,混频器采用HP公司的IAM-81008。放大器中的反馈放大器采用微波单片集成放大器,选用HP公司的INA-02186硅双极MMIC反馈放大器;而线性放大器选用MC10H115,是四个用于整形且通过长线传输不同信号的放大器。本地振荡器采用一个晶振倍频源,倍频至1000MHz,为降低倍频源的输出杂散分量,在输出端进行滤波,以得到频谱纯净的本振源信号。为了缩短频率合成器频率的转换时间,在锁相环路基础上外加快速捕获电路。快速捕获电路是采用频率数字变换辅助捕获方法获得捕获的。

图1中的环路滤波器采用带预积分的有源积分滤波器,如图2所示。

就阻带衰减的陡度而言,以椭圆函数滤波器最好,所以抑制滤波器选择椭圆函数滤波器。在本电路中,参考输入频率为10MHz,参考分频比为3,故鉴频鉴相器输出为3.33MHz。为降低整个频率综合器的杂散噪声和相位噪声,设计时考虑到从0~1.2MHz的范围内衰0.2dB,而3MHz以上的范围衰减大于60dB,最后设计的抑制滤波器如图3所示。其幅频特性如图4所示。

图1中的环路滤波器采用带预积分的有源积分滤波器,如图2所示。

就阻带衰减的陡度而言,以椭圆函数滤波器最好,所以抑制滤波器选择椭圆函数滤波器。在本电路中,参考输入频率为10MHz,参考分频比为3,故鉴频鉴相器输出为3.33MHz。为降低整个频率综合器的杂散噪声和相位噪声,设计时考虑到从0~1.2MHz的范围内衰0.2dB,而3MHz以上的范围衰减大于60dB,最后设计的抑制滤波器如图3所示。其幅频特性如图4所示。

为了达到超带宽,160MHz~650MHz带通滤波器采用电容耦合的节点耦合滤波器进行设计,所设计的滤波器电路如图5所示。

对所设计的带通滤波器用PSPICE进行仿真,其幅频特性(V(R2))如图6所示。

图5

3 系统的连线与测试

在完成上述单元电路器件的选择和设计以后,用PROTEL对电路的PCB板图进行具体布局和布线。在布线的过程中要注意电源的供电、器件的接地和耦合器件间的屏蔽。最后所设计的超宽带雷达信号产生电路的信号产生结果进行仿真。其仿真结果如图7所示。

为了达到超带宽,160MHz~650MHz带通滤波器采用电容耦合的节点耦合滤波器进行设计,所设计的滤波器电路如图5所示。

对所设计的带通滤波器用PSPICE进行仿真,其幅频特性(V(R2))如图6所示。

图5

3 系统的连线与测试

在完成上述单元电路器件的选择和设计以后,用PROTEL对电路的PCB板图进行具体布局和布线。在布线的过程中要注意电源的供电、器件的接地和耦合器件间的屏蔽。最后所设计的超宽带雷达信号产生电路的信号产生结果进行仿真。其仿真结果如图7所示。

通过对系统的测试结果进行分析,电路最终终产生的结果达到了预期的信号形式和工作频率范围内的各项指标要求。

通过对系统的测试结果进行分析,电路最终终产生的结果达到了预期的信号形式和工作频率范围内的各项指标要求。

超宽带高稳定雷达信号产生电路对提高现有雷达的性能以及研制新一代高性能雷达都具有非常重要的意义。它不仅增强雷达的反干扰能力,有效地对付导弹辐射,而且由于其盯对带宽和绝对带宽都比较宽,在雷达成像、雷达目标识别、雷达低仰角跟踪等方面都有重要的应用;它是新一代雷达的关键技术,具有广泛的应用前景。

超宽带高稳定雷达信号产生电路对提高现有雷达的性能以及研制新一代高性能雷达都具有非常重要的意义。它不仅增强雷达的反干扰能力,有效地对付导弹辐射,而且由于其盯对带宽和绝对带宽都比较宽,在雷达成像、雷达目标识别、雷达低仰角跟踪等方面都有重要的应用;它是新一代雷达的关键技术,具有广泛的应用前景。

上一篇:楼宇自动化控制网络数据通信协议BACnet

下一篇:VoIP语音卡在路由器中的应用及硬件设计

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新网络通信文章

- 应对 AI 时代的云工作负载,开发者正加速向 Arm 架构迁移

- NVIDIA 推出高性价比的生成式 AI 超级计算机

- Gartner发布2025年影响基础设施和运营的重要趋势

- 智谱清言英特尔酷睿Ultra专享版发布,离线模型玩转AIPC

- Quobly与意法半导体建立战略合作, 加快量子处理器制造进程,实现大型量子计算解决方

- RTI Connext Drive参展CES 2025,以领先通信框架加速SDV开发

- 黑莓 1.6 亿美元甩卖网络安全业务 Cylance,远低于其 14 亿美元的收购价

- eIQ® Time Series Studio简介:简化边缘 AI 开发

- 尺寸更小,性能更强:左蓝微电子发布两款PESAW双工器

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 MCP6054-E/STVAO

MCP6054-E/STVAO

京公网安备 11010802033920号

京公网安备 11010802033920号