摘要:ADV202是AD公司推出的JPEG2000编解码芯片。该芯片采用专利空间超效率回归滤波(SURF)技术,具有较低的功耗和成本。文中介绍了ADV202的主要特点及工作原理,并给出了ADV202的几种典型应用电路。

关键词:JPEG2000 ADV202 SURF 编解码器

ADV202是AD公司最新推出的一款单片JPEG2000(ISO/IEC15444-1图像压缩标准)编解码芯片,是当今市场上少有的具有实时压缩和解压缩标准(SD)视频信号和高清晰度(HDTV)视频信号功能的芯片。该芯片带有一个灵活接口,适用于多种视频和静止图像格式。

1 主要特点

%26;#183;视频和静止图像的完全单片JPEG2000压缩和解压解决方案;

%26;#183;专利的空间超效率回归滤波(SURF)技术使之具有低功耗和低成本的小波压缩;

%26;#183;支持最高6级的9/7和5/3小波变换;

%26;#183;可编程图块/图像尺寸,在3分量4:2:2隔行扫描中的宽度可达2048像素,单分量模式中的宽度可达4096像素;

%26;#183;最大图块/图像高度:4096像素;

%26;#183;视频接口可直接支持ITU.R-BT656、SMPTE125M PAL/NTSC、SMPTE274M、SMPTE293M(525p)、ITU.R-BT1358(625p),以及不可逆模式最大输入速度为65Msps、可逆模式最大输入速度为40Msps的任何视频格式;

%26;#183;两个或多个ADV202能组合满帧SMPTE274M HDTV(1080i)或SMPTE296M(720p);

%26;#183;灵活异步SRAM类型主机接口能无缝连接到大多数16/32位微控制器和ASIC;

%26;#183;速率为115MHz的产品采用12mm%26;#215;12mm121引脚CSPBGA封装,速率为150MHz产品采用13mm%26;#215;13mm 144引脚CSPBGA封装。

根据特殊的应用需求,ADV202可提供JPEG2000压缩所支持的不同标准,可提供原始的编码模块和特征数据输出,而JPEG2000编码流的产生和其它诸如位速率控制等的压缩过程则完全由主机软件来控制。另外,它也可以制作完整的、完全兼容的JPEG2000码流(j2c)以及jp2、jpx和mj2(运动JPEG2000)增强型格式的文件。

1 主要特点

%26;#183;视频和静止图像的完全单片JPEG2000压缩和解压解决方案;

%26;#183;专利的空间超效率回归滤波(SURF)技术使之具有低功耗和低成本的小波压缩;

%26;#183;支持最高6级的9/7和5/3小波变换;

%26;#183;可编程图块/图像尺寸,在3分量4:2:2隔行扫描中的宽度可达2048像素,单分量模式中的宽度可达4096像素;

%26;#183;最大图块/图像高度:4096像素;

%26;#183;视频接口可直接支持ITU.R-BT656、SMPTE125M PAL/NTSC、SMPTE274M、SMPTE293M(525p)、ITU.R-BT1358(625p),以及不可逆模式最大输入速度为65Msps、可逆模式最大输入速度为40Msps的任何视频格式;

%26;#183;两个或多个ADV202能组合满帧SMPTE274M HDTV(1080i)或SMPTE296M(720p);

%26;#183;灵活异步SRAM类型主机接口能无缝连接到大多数16/32位微控制器和ASIC;

%26;#183;速率为115MHz的产品采用12mm%26;#215;12mm121引脚CSPBGA封装,速率为150MHz产品采用13mm%26;#215;13mm 144引脚CSPBGA封装。

根据特殊的应用需求,ADV202可提供JPEG2000压缩所支持的不同标准,可提供原始的编码模块和特征数据输出,而JPEG2000编码流的产生和其它诸如位速率控制等的压缩过程则完全由主机软件来控制。另外,它也可以制作完整的、完全兼容的JPEG2000码流(j2c)以及jp2、jpx和mj2(运动JPEG2000)增强型格式的文件。

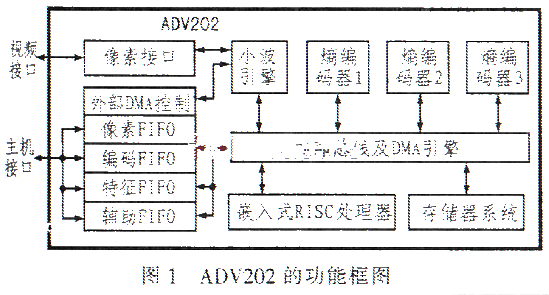

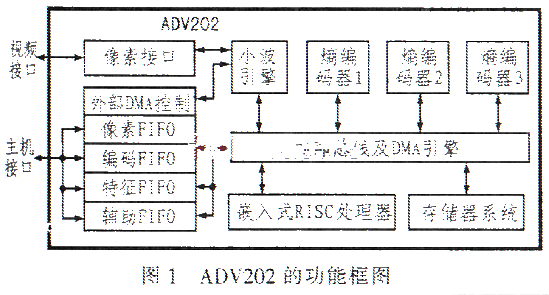

2 工作原理

ADV202的内部功能框图如图所示,该芯片主要由像素接口、小波变换引擎、熵编解码器、嵌入式处理器、存储器系统和内部DMA引擎等组成。输入图像和像素数据输入像素接口,采样值则经过隔行扫描传输到小波变换引擎中。在小波引擎中,每个图块或帧将通过5/3或9/7滤波器分解成许多子带。生成的小波系数写入内部寄存器中。熵编解码器将图像数据编码为符合JPEG2000标准的数据。内部DMA引擎提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输。

2.1 小波变换引擎

由于ADV202内含基于AD专利SURF技术的专用小波变换处理器。因此,它可以对一个图块进行高达6级的小波分解。在编码方式中,小波变换处理器将对未压缩的采样值进行小波变换和量化,然后将所有频率子带的小波系数写到内部存储器中。这些子带进一步分解成大小由用户定义的编码块,在将小波系数写入内部存储器时,通常由小波变换处理器来组织小波系数。在解码方式中,小波系数从内部存储器中读出,以用来重新生成未压缩时的采样值。

2.2 熵编解码器

熵编解码器用来对小波系数的编码块进行背景建模和算术编码,同时可在压缩过程中计算最佳速率和失真性能所必需的失真度。由于熵编码过程在JPEG2000压缩工程中对计算要求最高,因此,ADV202内部提供了三个专用的硬件熵编解码器。

2.3 嵌入式处理器

ADV202内嵌入了一个32位的RISC处理器,可用来配置、控制和管理其它专用硬件模块以及分解和产生JPEG2000视频流。RISC处理器具有每一个程序和数据存储器、中断控制器、标准总线接口及定时器计数器所对应的ROM和RAM。

2.4 存储器系统

存储器系统的主要功能是管理小波变换的系数数据、暂时存放编码块的特征数据以及给JPEG2000码流提供临时的存储空间。另外还可用作嵌入式处理器的程序和数据存储器。

图3

2.5 内部DMA引擎

内部DMA引擎可提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输。这对于码流的分解和高速率数据的产生万为重要。

2.6 可配置FIFO模块

内部FIFO用来给像素数据、编码流、特征数据或者其他辅助数据提供存储空间。它可以由主机接口在通常地址的读写周期中直接访问,也可以由外部主机DMA利用DREQ/DACK协议或专用硬件的握手机制来访问。每个FIFO都有一个可编程的门限值用来产生中断。

2.7 视频和主机接口

有多种模式可以用来配置ADV202的接口。设计人员可以同时使用VDATA总线和HDATA总线,也可以单独使用HDATA总线。

(1)视频接口(VDATA总线)

视频接口主要应用于未压缩像素数据和压缩数据分离的场合。例如用VDATA总线输入未压缩的数据,而通过HDATA总线输出压缩后的数据等。

视频接口支持8、10、12位单一或多元格式,也支持双通道8、10、12位格式的视频和静止图像数据,还支持单通道输入模式下YcrCb格式的数字视频和双通道输入模式下Y和CrCb格式的数字视频信号,但YcrCb数据必须是4:2:2格式。VDATA总线可支持多种格式视频数据的输入输出,表1所列是其可支持的视频输入输出格式。

表1 视频输入输出模式

视频模式

描 述

EAV/SAV模式

包含EAV/SAV编码的视频,YCrCb在单总线上隔行扫描

HVF模式

H,V,F独立的视频信号,YCrCb在单总线上的隔行扫描

双通道模式

包含EAV/SAV编码的视频,Y和YCrCb在独立的总线

原始视频模式

用于静止图征和非标准视频

HDTV模式

用于高于27MHz时钟信号的视频数据

(2)主机接口(HDATA总线)

ADV202可以通过异步SRAM方式、DMA访问方式或码流方式直接和大多数主机处理器及ASIC相连接。ADV202提供有16位和32位控制总线及8、16和32位数据传输总线。主机接口用于配置、控制制控制功能以及传输压缩后的数据流,在某些格式中还可用作未压缩数据流的传输。主机接口要吧由并发的四个数据流及控制和状态通信所共享。输入主机接口的像素数据支持8、10、12、14和16位原始像素数据。它既可用作静止图像的输入输出,也可用作压缩后视频数据的输出。

3 典型应用

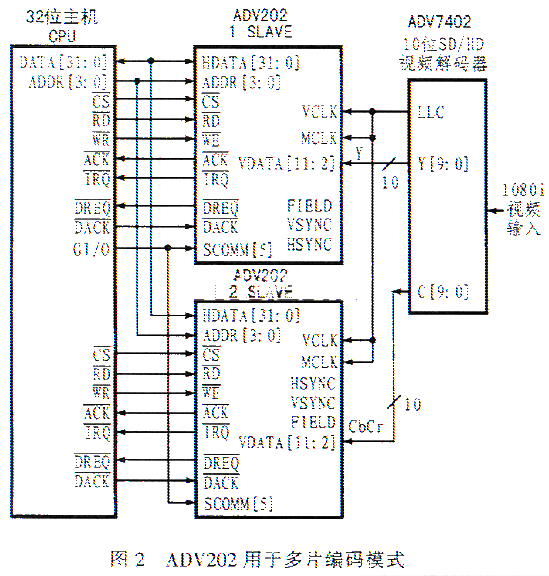

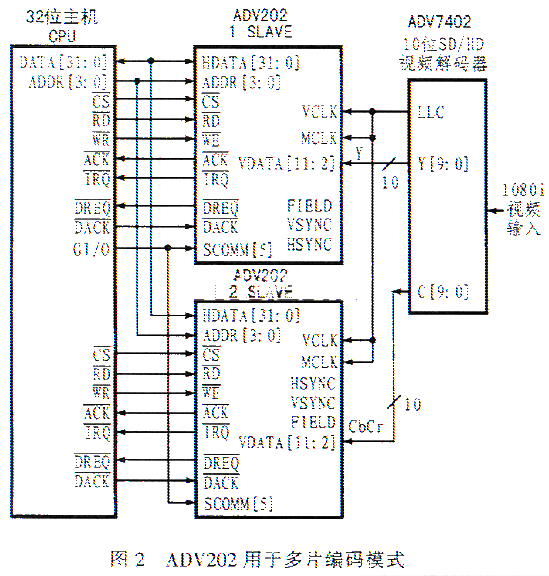

3.1 多片编码模式

由于输入数据速率的限制,一个1080i视频信号的应用系统至少需要两片ADV202,来对完全分辨率为1080i的视频信号进行编码或解码。图2所示为它的编码模式,Y数据和CbCr数据通过不同的总线输入到ADV202,其中AD202_1处理1080i视频信号的亮度数据,而ADV202_2则用于处理1080i视频信号的色度数据。为了对此应用模式下对应的输出数据进行同步,其输入数据必须是EAV/SAV编码格式。此模式通常应用于ADV202的视频输出直接连到需要亮度和色度数据同步的接收设备中。

多片模式也可以应用于主/从或从/从配置中的解码模式。而在编码模式中,ADV202通常用作从设备。为了使获取的1080i视频信号具有更好的特性(如无损压缩),建议选用三片或三片以上的ADV202来处理信号。

3.2 HPII(主机接口-像素接口)解码模式

ADV202允许通过HDATA总线来输入输出视频和静止图像,而不用VDATA总线提供的专用视频接口,这种模式称为HIPI模式。

图3所示为ADV202用于HIPI解码模式的电路连接,像素数据由HDATA1[31:1]输出。DMA通道1用来输入压缩数据,而DMA通道0则用于将像素数据写到像素FIFO中。DREQ0/DACK0用来控制通道0的读写过程,而DREQ1/DACK1用来控制通道1的读写过程。

2 工作原理

ADV202的内部功能框图如图所示,该芯片主要由像素接口、小波变换引擎、熵编解码器、嵌入式处理器、存储器系统和内部DMA引擎等组成。输入图像和像素数据输入像素接口,采样值则经过隔行扫描传输到小波变换引擎中。在小波引擎中,每个图块或帧将通过5/3或9/7滤波器分解成许多子带。生成的小波系数写入内部寄存器中。熵编解码器将图像数据编码为符合JPEG2000标准的数据。内部DMA引擎提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输。

2.1 小波变换引擎

由于ADV202内含基于AD专利SURF技术的专用小波变换处理器。因此,它可以对一个图块进行高达6级的小波分解。在编码方式中,小波变换处理器将对未压缩的采样值进行小波变换和量化,然后将所有频率子带的小波系数写到内部存储器中。这些子带进一步分解成大小由用户定义的编码块,在将小波系数写入内部存储器时,通常由小波变换处理器来组织小波系数。在解码方式中,小波系数从内部存储器中读出,以用来重新生成未压缩时的采样值。

2.2 熵编解码器

熵编解码器用来对小波系数的编码块进行背景建模和算术编码,同时可在压缩过程中计算最佳速率和失真性能所必需的失真度。由于熵编码过程在JPEG2000压缩工程中对计算要求最高,因此,ADV202内部提供了三个专用的硬件熵编解码器。

2.3 嵌入式处理器

ADV202内嵌入了一个32位的RISC处理器,可用来配置、控制和管理其它专用硬件模块以及分解和产生JPEG2000视频流。RISC处理器具有每一个程序和数据存储器、中断控制器、标准总线接口及定时器计数器所对应的ROM和RAM。

2.4 存储器系统

存储器系统的主要功能是管理小波变换的系数数据、暂时存放编码块的特征数据以及给JPEG2000码流提供临时的存储空间。另外还可用作嵌入式处理器的程序和数据存储器。

图3

2.5 内部DMA引擎

内部DMA引擎可提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输。这对于码流的分解和高速率数据的产生万为重要。

2.6 可配置FIFO模块

内部FIFO用来给像素数据、编码流、特征数据或者其他辅助数据提供存储空间。它可以由主机接口在通常地址的读写周期中直接访问,也可以由外部主机DMA利用DREQ/DACK协议或专用硬件的握手机制来访问。每个FIFO都有一个可编程的门限值用来产生中断。

2.7 视频和主机接口

有多种模式可以用来配置ADV202的接口。设计人员可以同时使用VDATA总线和HDATA总线,也可以单独使用HDATA总线。

(1)视频接口(VDATA总线)

视频接口主要应用于未压缩像素数据和压缩数据分离的场合。例如用VDATA总线输入未压缩的数据,而通过HDATA总线输出压缩后的数据等。

视频接口支持8、10、12位单一或多元格式,也支持双通道8、10、12位格式的视频和静止图像数据,还支持单通道输入模式下YcrCb格式的数字视频和双通道输入模式下Y和CrCb格式的数字视频信号,但YcrCb数据必须是4:2:2格式。VDATA总线可支持多种格式视频数据的输入输出,表1所列是其可支持的视频输入输出格式。

表1 视频输入输出模式

视频模式

描 述

EAV/SAV模式

包含EAV/SAV编码的视频,YCrCb在单总线上隔行扫描

HVF模式

H,V,F独立的视频信号,YCrCb在单总线上的隔行扫描

双通道模式

包含EAV/SAV编码的视频,Y和YCrCb在独立的总线

原始视频模式

用于静止图征和非标准视频

HDTV模式

用于高于27MHz时钟信号的视频数据

(2)主机接口(HDATA总线)

ADV202可以通过异步SRAM方式、DMA访问方式或码流方式直接和大多数主机处理器及ASIC相连接。ADV202提供有16位和32位控制总线及8、16和32位数据传输总线。主机接口用于配置、控制制控制功能以及传输压缩后的数据流,在某些格式中还可用作未压缩数据流的传输。主机接口要吧由并发的四个数据流及控制和状态通信所共享。输入主机接口的像素数据支持8、10、12、14和16位原始像素数据。它既可用作静止图像的输入输出,也可用作压缩后视频数据的输出。

3 典型应用

3.1 多片编码模式

由于输入数据速率的限制,一个1080i视频信号的应用系统至少需要两片ADV202,来对完全分辨率为1080i的视频信号进行编码或解码。图2所示为它的编码模式,Y数据和CbCr数据通过不同的总线输入到ADV202,其中AD202_1处理1080i视频信号的亮度数据,而ADV202_2则用于处理1080i视频信号的色度数据。为了对此应用模式下对应的输出数据进行同步,其输入数据必须是EAV/SAV编码格式。此模式通常应用于ADV202的视频输出直接连到需要亮度和色度数据同步的接收设备中。

多片模式也可以应用于主/从或从/从配置中的解码模式。而在编码模式中,ADV202通常用作从设备。为了使获取的1080i视频信号具有更好的特性(如无损压缩),建议选用三片或三片以上的ADV202来处理信号。

3.2 HPII(主机接口-像素接口)解码模式

ADV202允许通过HDATA总线来输入输出视频和静止图像,而不用VDATA总线提供的专用视频接口,这种模式称为HIPI模式。

图3所示为ADV202用于HIPI解码模式的电路连接,像素数据由HDATA1[31:1]输出。DMA通道1用来输入压缩数据,而DMA通道0则用于将像素数据写到像素FIFO中。DREQ0/DACK0用来控制通道0的读写过程,而DREQ1/DACK1用来控制通道1的读写过程。

引用地址:JPEG2000编解码芯片ADV202的原理及应用

1 主要特点

%26;#183;视频和静止图像的完全单片JPEG2000压缩和解压解决方案;

%26;#183;专利的空间超效率回归滤波(SURF)技术使之具有低功耗和低成本的小波压缩;

%26;#183;支持最高6级的9/7和5/3小波变换;

%26;#183;可编程图块/图像尺寸,在3分量4:2:2隔行扫描中的宽度可达2048像素,单分量模式中的宽度可达4096像素;

%26;#183;最大图块/图像高度:4096像素;

%26;#183;视频接口可直接支持ITU.R-BT656、SMPTE125M PAL/NTSC、SMPTE274M、SMPTE293M(525p)、ITU.R-BT1358(625p),以及不可逆模式最大输入速度为65Msps、可逆模式最大输入速度为40Msps的任何视频格式;

%26;#183;两个或多个ADV202能组合满帧SMPTE274M HDTV(1080i)或SMPTE296M(720p);

%26;#183;灵活异步SRAM类型主机接口能无缝连接到大多数16/32位微控制器和ASIC;

%26;#183;速率为115MHz的产品采用12mm%26;#215;12mm121引脚CSPBGA封装,速率为150MHz产品采用13mm%26;#215;13mm 144引脚CSPBGA封装。

根据特殊的应用需求,ADV202可提供JPEG2000压缩所支持的不同标准,可提供原始的编码模块和特征数据输出,而JPEG2000编码流的产生和其它诸如位速率控制等的压缩过程则完全由主机软件来控制。另外,它也可以制作完整的、完全兼容的JPEG2000码流(j2c)以及jp2、jpx和mj2(运动JPEG2000)增强型格式的文件。

1 主要特点

%26;#183;视频和静止图像的完全单片JPEG2000压缩和解压解决方案;

%26;#183;专利的空间超效率回归滤波(SURF)技术使之具有低功耗和低成本的小波压缩;

%26;#183;支持最高6级的9/7和5/3小波变换;

%26;#183;可编程图块/图像尺寸,在3分量4:2:2隔行扫描中的宽度可达2048像素,单分量模式中的宽度可达4096像素;

%26;#183;最大图块/图像高度:4096像素;

%26;#183;视频接口可直接支持ITU.R-BT656、SMPTE125M PAL/NTSC、SMPTE274M、SMPTE293M(525p)、ITU.R-BT1358(625p),以及不可逆模式最大输入速度为65Msps、可逆模式最大输入速度为40Msps的任何视频格式;

%26;#183;两个或多个ADV202能组合满帧SMPTE274M HDTV(1080i)或SMPTE296M(720p);

%26;#183;灵活异步SRAM类型主机接口能无缝连接到大多数16/32位微控制器和ASIC;

%26;#183;速率为115MHz的产品采用12mm%26;#215;12mm121引脚CSPBGA封装,速率为150MHz产品采用13mm%26;#215;13mm 144引脚CSPBGA封装。

根据特殊的应用需求,ADV202可提供JPEG2000压缩所支持的不同标准,可提供原始的编码模块和特征数据输出,而JPEG2000编码流的产生和其它诸如位速率控制等的压缩过程则完全由主机软件来控制。另外,它也可以制作完整的、完全兼容的JPEG2000码流(j2c)以及jp2、jpx和mj2(运动JPEG2000)增强型格式的文件。

2 工作原理

ADV202的内部功能框图如图所示,该芯片主要由像素接口、小波变换引擎、熵编解码器、嵌入式处理器、存储器系统和内部DMA引擎等组成。输入图像和像素数据输入像素接口,采样值则经过隔行扫描传输到小波变换引擎中。在小波引擎中,每个图块或帧将通过5/3或9/7滤波器分解成许多子带。生成的小波系数写入内部寄存器中。熵编解码器将图像数据编码为符合JPEG2000标准的数据。内部DMA引擎提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输。

2.1 小波变换引擎

由于ADV202内含基于AD专利SURF技术的专用小波变换处理器。因此,它可以对一个图块进行高达6级的小波分解。在编码方式中,小波变换处理器将对未压缩的采样值进行小波变换和量化,然后将所有频率子带的小波系数写到内部存储器中。这些子带进一步分解成大小由用户定义的编码块,在将小波系数写入内部存储器时,通常由小波变换处理器来组织小波系数。在解码方式中,小波系数从内部存储器中读出,以用来重新生成未压缩时的采样值。

2.2 熵编解码器

熵编解码器用来对小波系数的编码块进行背景建模和算术编码,同时可在压缩过程中计算最佳速率和失真性能所必需的失真度。由于熵编码过程在JPEG2000压缩工程中对计算要求最高,因此,ADV202内部提供了三个专用的硬件熵编解码器。

2.3 嵌入式处理器

ADV202内嵌入了一个32位的RISC处理器,可用来配置、控制和管理其它专用硬件模块以及分解和产生JPEG2000视频流。RISC处理器具有每一个程序和数据存储器、中断控制器、标准总线接口及定时器计数器所对应的ROM和RAM。

2.4 存储器系统

存储器系统的主要功能是管理小波变换的系数数据、暂时存放编码块的特征数据以及给JPEG2000码流提供临时的存储空间。另外还可用作嵌入式处理器的程序和数据存储器。

图3

2.5 内部DMA引擎

内部DMA引擎可提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输。这对于码流的分解和高速率数据的产生万为重要。

2.6 可配置FIFO模块

内部FIFO用来给像素数据、编码流、特征数据或者其他辅助数据提供存储空间。它可以由主机接口在通常地址的读写周期中直接访问,也可以由外部主机DMA利用DREQ/DACK协议或专用硬件的握手机制来访问。每个FIFO都有一个可编程的门限值用来产生中断。

2.7 视频和主机接口

有多种模式可以用来配置ADV202的接口。设计人员可以同时使用VDATA总线和HDATA总线,也可以单独使用HDATA总线。

(1)视频接口(VDATA总线)

视频接口主要应用于未压缩像素数据和压缩数据分离的场合。例如用VDATA总线输入未压缩的数据,而通过HDATA总线输出压缩后的数据等。

视频接口支持8、10、12位单一或多元格式,也支持双通道8、10、12位格式的视频和静止图像数据,还支持单通道输入模式下YcrCb格式的数字视频和双通道输入模式下Y和CrCb格式的数字视频信号,但YcrCb数据必须是4:2:2格式。VDATA总线可支持多种格式视频数据的输入输出,表1所列是其可支持的视频输入输出格式。

表1 视频输入输出模式

视频模式

描 述

EAV/SAV模式

包含EAV/SAV编码的视频,YCrCb在单总线上隔行扫描

HVF模式

H,V,F独立的视频信号,YCrCb在单总线上的隔行扫描

双通道模式

包含EAV/SAV编码的视频,Y和YCrCb在独立的总线

原始视频模式

用于静止图征和非标准视频

HDTV模式

用于高于27MHz时钟信号的视频数据

(2)主机接口(HDATA总线)

ADV202可以通过异步SRAM方式、DMA访问方式或码流方式直接和大多数主机处理器及ASIC相连接。ADV202提供有16位和32位控制总线及8、16和32位数据传输总线。主机接口用于配置、控制制控制功能以及传输压缩后的数据流,在某些格式中还可用作未压缩数据流的传输。主机接口要吧由并发的四个数据流及控制和状态通信所共享。输入主机接口的像素数据支持8、10、12、14和16位原始像素数据。它既可用作静止图像的输入输出,也可用作压缩后视频数据的输出。

3 典型应用

3.1 多片编码模式

由于输入数据速率的限制,一个1080i视频信号的应用系统至少需要两片ADV202,来对完全分辨率为1080i的视频信号进行编码或解码。图2所示为它的编码模式,Y数据和CbCr数据通过不同的总线输入到ADV202,其中AD202_1处理1080i视频信号的亮度数据,而ADV202_2则用于处理1080i视频信号的色度数据。为了对此应用模式下对应的输出数据进行同步,其输入数据必须是EAV/SAV编码格式。此模式通常应用于ADV202的视频输出直接连到需要亮度和色度数据同步的接收设备中。

多片模式也可以应用于主/从或从/从配置中的解码模式。而在编码模式中,ADV202通常用作从设备。为了使获取的1080i视频信号具有更好的特性(如无损压缩),建议选用三片或三片以上的ADV202来处理信号。

3.2 HPII(主机接口-像素接口)解码模式

ADV202允许通过HDATA总线来输入输出视频和静止图像,而不用VDATA总线提供的专用视频接口,这种模式称为HIPI模式。

图3所示为ADV202用于HIPI解码模式的电路连接,像素数据由HDATA1[31:1]输出。DMA通道1用来输入压缩数据,而DMA通道0则用于将像素数据写到像素FIFO中。DREQ0/DACK0用来控制通道0的读写过程,而DREQ1/DACK1用来控制通道1的读写过程。

2 工作原理

ADV202的内部功能框图如图所示,该芯片主要由像素接口、小波变换引擎、熵编解码器、嵌入式处理器、存储器系统和内部DMA引擎等组成。输入图像和像素数据输入像素接口,采样值则经过隔行扫描传输到小波变换引擎中。在小波引擎中,每个图块或帧将通过5/3或9/7滤波器分解成许多子带。生成的小波系数写入内部寄存器中。熵编解码器将图像数据编码为符合JPEG2000标准的数据。内部DMA引擎提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输。

2.1 小波变换引擎

由于ADV202内含基于AD专利SURF技术的专用小波变换处理器。因此,它可以对一个图块进行高达6级的小波分解。在编码方式中,小波变换处理器将对未压缩的采样值进行小波变换和量化,然后将所有频率子带的小波系数写到内部存储器中。这些子带进一步分解成大小由用户定义的编码块,在将小波系数写入内部存储器时,通常由小波变换处理器来组织小波系数。在解码方式中,小波系数从内部存储器中读出,以用来重新生成未压缩时的采样值。

2.2 熵编解码器

熵编解码器用来对小波系数的编码块进行背景建模和算术编码,同时可在压缩过程中计算最佳速率和失真性能所必需的失真度。由于熵编码过程在JPEG2000压缩工程中对计算要求最高,因此,ADV202内部提供了三个专用的硬件熵编解码器。

2.3 嵌入式处理器

ADV202内嵌入了一个32位的RISC处理器,可用来配置、控制和管理其它专用硬件模块以及分解和产生JPEG2000视频流。RISC处理器具有每一个程序和数据存储器、中断控制器、标准总线接口及定时器计数器所对应的ROM和RAM。

2.4 存储器系统

存储器系统的主要功能是管理小波变换的系数数据、暂时存放编码块的特征数据以及给JPEG2000码流提供临时的存储空间。另外还可用作嵌入式处理器的程序和数据存储器。

图3

2.5 内部DMA引擎

内部DMA引擎可提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输。这对于码流的分解和高速率数据的产生万为重要。

2.6 可配置FIFO模块

内部FIFO用来给像素数据、编码流、特征数据或者其他辅助数据提供存储空间。它可以由主机接口在通常地址的读写周期中直接访问,也可以由外部主机DMA利用DREQ/DACK协议或专用硬件的握手机制来访问。每个FIFO都有一个可编程的门限值用来产生中断。

2.7 视频和主机接口

有多种模式可以用来配置ADV202的接口。设计人员可以同时使用VDATA总线和HDATA总线,也可以单独使用HDATA总线。

(1)视频接口(VDATA总线)

视频接口主要应用于未压缩像素数据和压缩数据分离的场合。例如用VDATA总线输入未压缩的数据,而通过HDATA总线输出压缩后的数据等。

视频接口支持8、10、12位单一或多元格式,也支持双通道8、10、12位格式的视频和静止图像数据,还支持单通道输入模式下YcrCb格式的数字视频和双通道输入模式下Y和CrCb格式的数字视频信号,但YcrCb数据必须是4:2:2格式。VDATA总线可支持多种格式视频数据的输入输出,表1所列是其可支持的视频输入输出格式。

表1 视频输入输出模式

视频模式

描 述

EAV/SAV模式

包含EAV/SAV编码的视频,YCrCb在单总线上隔行扫描

HVF模式

H,V,F独立的视频信号,YCrCb在单总线上的隔行扫描

双通道模式

包含EAV/SAV编码的视频,Y和YCrCb在独立的总线

原始视频模式

用于静止图征和非标准视频

HDTV模式

用于高于27MHz时钟信号的视频数据

(2)主机接口(HDATA总线)

ADV202可以通过异步SRAM方式、DMA访问方式或码流方式直接和大多数主机处理器及ASIC相连接。ADV202提供有16位和32位控制总线及8、16和32位数据传输总线。主机接口用于配置、控制制控制功能以及传输压缩后的数据流,在某些格式中还可用作未压缩数据流的传输。主机接口要吧由并发的四个数据流及控制和状态通信所共享。输入主机接口的像素数据支持8、10、12、14和16位原始像素数据。它既可用作静止图像的输入输出,也可用作压缩后视频数据的输出。

3 典型应用

3.1 多片编码模式

由于输入数据速率的限制,一个1080i视频信号的应用系统至少需要两片ADV202,来对完全分辨率为1080i的视频信号进行编码或解码。图2所示为它的编码模式,Y数据和CbCr数据通过不同的总线输入到ADV202,其中AD202_1处理1080i视频信号的亮度数据,而ADV202_2则用于处理1080i视频信号的色度数据。为了对此应用模式下对应的输出数据进行同步,其输入数据必须是EAV/SAV编码格式。此模式通常应用于ADV202的视频输出直接连到需要亮度和色度数据同步的接收设备中。

多片模式也可以应用于主/从或从/从配置中的解码模式。而在编码模式中,ADV202通常用作从设备。为了使获取的1080i视频信号具有更好的特性(如无损压缩),建议选用三片或三片以上的ADV202来处理信号。

3.2 HPII(主机接口-像素接口)解码模式

ADV202允许通过HDATA总线来输入输出视频和静止图像,而不用VDATA总线提供的专用视频接口,这种模式称为HIPI模式。

图3所示为ADV202用于HIPI解码模式的电路连接,像素数据由HDATA1[31:1]输出。DMA通道1用来输入压缩数据,而DMA通道0则用于将像素数据写到像素FIFO中。DREQ0/DACK0用来控制通道0的读写过程,而DREQ1/DACK1用来控制通道1的读写过程。

上一篇:便携式设备中的无源元件对音频质量的影响

下一篇:便携式电子设备中的立体声

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新手机便携文章

- 古尔曼称苹果明年推出 AirTag 2 追踪器:升级 UWB 超宽带芯片,精确定位范围提升 3 倍

- 消息称苹果自研再下一城:蓝牙+Wi-Fi芯片 2025年iPhone 17系列首发

- 苹果从iPhone 18 Pro开始将弃用高通5G芯片

- 印尼投资部长确认:苹果计划在当地投资10亿美元建造零部件工厂

- 消息称苹果有望2026下半年推出折叠iPhone,并重振折叠屏手机市场

- 华为麒麟9020/9030/9040处理器曝光:小步快跑 四大方面升级

- 汇顶超声波指纹方案助力iQOO Neo10流畅解锁体验

- 曝苹果自研5G基带性能弱于高通:iPhone信号问题无解

- 消息称 AMD 将入局手机芯片领域,采用台积电 3nm 工艺

更多开源项目推荐

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TTLM4250CJ

TTLM4250CJ

京公网安备 11010802033920号

京公网安备 11010802033920号