摘要:介绍了CIRRUS LOGIC公司生产的音频解码芯片CS43L42与嵌入式处理器EP7212的接口实现方法,分析了基于嵌入式处理器EP7212/7312和CS43L42芯片的MP3文件播放系统,给出了由其组成的完整硬件连接图和有效的软件实现方法。

关键词:嵌入式处理器;数字音频接口DAI;CS43L42;MP3;EP7212

1 引言

目前存储声音信息的音频数据格式主要有PCM文件、VOC文件、MIDI文件、MP3文件等。对导航系统来说,要实现音频文件的播放,存储器容量是一个需要考虑的问题。由于导航系统的存储空间有限,所以要求存储的文件压缩率高。与其它文件格式相比,MP3音频文件具有较高的压缩率和不逊色于CD的音质,所以在导航系统中音频文件的存储选用MP3格式。

MP3的全称为MPEG1 Layer-3音频文件,MPEGMoving Picture Experts Group在汉语中译为活动图像专家组,特指活动影音压缩标准。MPEG音频文件是MPEG1标准中的声音部分,也叫MPEG音频层,它根据压缩质量和编码复杂程度划分为三层,即Layer1、Layer2、Layer3,分别对应MP1、MP2、MP3这三种声音文件,并根据不同的用途,使用不同层次的编码。MPEG音频编码的层次越高,编码器越复杂,压缩率也越高,MP1和MP2的压缩率分别为4:1和6:1~8:1,而MP3的压缩率则高达10:1~12:1,也就是说,一分钟CD音质的音乐,未经压缩需要10MB的存储空间,而经过MP3压缩编码后只有1MB左右。不过MP3对音频信号采用的是有损压缩方式,为了降低声音失真度,MP3采取了“感官编码技术”,即编码时先对音频文件进行频谱分析,然后再用过滤器滤掉噪音电平,接着通过量化的方式将剩下的每一位重新排列,最后形成具有较高压缩率的MP3文件,从而使压缩后的文件在回放时能够达到比较接近原音源的声音效果。

虽然MP3是一种有损压缩方式,但它以极小的声音失真换来较高的压缩比,因此在较多的场合得以应用。尤其是随着数字技术的发展,MP3压缩方式在便携式电子产品中得到了越来越广泛的应用,深受追求时尚、新潮的青年朋友的喜爱。

2 CS43L42播放芯片

CS43L42是CIRRUS LOGIC公司生产的音频解码芯片,

虽然MP3是一种有损压缩方式,但它以极小的声音失真换来较高的压缩比,因此在较多的场合得以应用。尤其是随着数字技术的发展,MP3压缩方式在便携式电子产品中得到了越来越广泛的应用,深受追求时尚、新潮的青年朋友的喜爱。

2 CS43L42播放芯片

CS43L42是CIRRUS LOGIC公司生产的音频解码芯片,

它可工作在1.8~3.3V,关掉线性放大器时功耗仅16mW非常适合于MP3、MD播放器等低功耗场合的应用。该芯片是一款完全意义上的数模转换器,它包括1bit D/A转换、模拟滤波、音量控制、线性电压输出以及耳机放大器。通过改变主频率,其允许的输入采样频率可从2k~100kHz变化。该器件具有数字重音、峰值限制和去加重等特性。此外,由于采用了POPGUARD技术,CS43L42还可有效防止加电、断电时产生的瞬间冲击。

CS43L42具有DAI接口,能够与嵌入式处理器EP7212/7312较好的配合。它具有三种模式:双线模式、SPI模式、STAND ALONE模式。通过引脚CP/SA和AD0/CS/DEM0置相应状态可以设置这三种模式。当CP/SA引脚为低电平时,芯片为STAND ALONE模式,当CP/SA为高电平时,只要检测到引脚AD0/CS/DEM0电平从低到高变化,则进入SPI模式,否则为双线模式。在STAND ALONE模式下,可用SCL/CCLK/DIF1和SDA/CDIN/DIF0引脚来设置数据、左/右时钟以及主时钟之间的关系。在双线模式和SPI模式下,则可以通过对寄存器进行操作来实现静音、声道衰减和音量控制等功能。图1是CS43L42的内部原理图,图2是该芯片的引脚排列示意图,各引脚的功能如下:

1脚(RST):复位信号,低有效。

2脚(LRCK):左/右帧同步。

3脚(SDATA):串行音频数据,数据随串行时钟引入。

4脚(AD0/CS/DEM0):在SPI模式下,用于使能控制端口。

5脚(SCLK/DEM1):位时钟,等于MCLK的1/2,每帧有128位。

6脚(VL):数字电源电压,典型值为1.8V~3.3V。

7脚(MCLK):2x过采样时钟,仅在从模式下输入。

图3

8脚(SCL/CCLK/DIF1):串行控制接口时钟。

9脚(SDA/CDIN/DIF0):串行控制数据输入输出。

10脚(N.C.):无连接,悬空。

11脚(CP/SA):控制模式和等待模式控制。

12脚(VQ_HP):耳机静态电压接口。

13脚(REF_GND):连接到模拟地。

14脚(FILT+):正向基准电压,用于内部采样电路。

15脚(VQ_LINE):线输出静态电压接口。

1621脚(HP_A,HP_B):耳机输出。

17脚(GND):连接到模拟地。

18脚(VA):模拟电源电压,典型值为1.8V~3.3V。

19脚(VA_LINE):线性扩音器电源端,典型值在1.8V~3.3V。

20脚(VA_HP):耳机放大电源端,典型值为0.9V~3.3V。

22,23脚(AOUTB AOUTA):模拟输出端。

24脚(MUTEC):静音控制。

它可工作在1.8~3.3V,关掉线性放大器时功耗仅16mW非常适合于MP3、MD播放器等低功耗场合的应用。该芯片是一款完全意义上的数模转换器,它包括1bit D/A转换、模拟滤波、音量控制、线性电压输出以及耳机放大器。通过改变主频率,其允许的输入采样频率可从2k~100kHz变化。该器件具有数字重音、峰值限制和去加重等特性。此外,由于采用了POPGUARD技术,CS43L42还可有效防止加电、断电时产生的瞬间冲击。

CS43L42具有DAI接口,能够与嵌入式处理器EP7212/7312较好的配合。它具有三种模式:双线模式、SPI模式、STAND ALONE模式。通过引脚CP/SA和AD0/CS/DEM0置相应状态可以设置这三种模式。当CP/SA引脚为低电平时,芯片为STAND ALONE模式,当CP/SA为高电平时,只要检测到引脚AD0/CS/DEM0电平从低到高变化,则进入SPI模式,否则为双线模式。在STAND ALONE模式下,可用SCL/CCLK/DIF1和SDA/CDIN/DIF0引脚来设置数据、左/右时钟以及主时钟之间的关系。在双线模式和SPI模式下,则可以通过对寄存器进行操作来实现静音、声道衰减和音量控制等功能。图1是CS43L42的内部原理图,图2是该芯片的引脚排列示意图,各引脚的功能如下:

1脚(RST):复位信号,低有效。

2脚(LRCK):左/右帧同步。

3脚(SDATA):串行音频数据,数据随串行时钟引入。

4脚(AD0/CS/DEM0):在SPI模式下,用于使能控制端口。

5脚(SCLK/DEM1):位时钟,等于MCLK的1/2,每帧有128位。

6脚(VL):数字电源电压,典型值为1.8V~3.3V。

7脚(MCLK):2x过采样时钟,仅在从模式下输入。

图3

8脚(SCL/CCLK/DIF1):串行控制接口时钟。

9脚(SDA/CDIN/DIF0):串行控制数据输入输出。

10脚(N.C.):无连接,悬空。

11脚(CP/SA):控制模式和等待模式控制。

12脚(VQ_HP):耳机静态电压接口。

13脚(REF_GND):连接到模拟地。

14脚(FILT+):正向基准电压,用于内部采样电路。

15脚(VQ_LINE):线输出静态电压接口。

1621脚(HP_A,HP_B):耳机输出。

17脚(GND):连接到模拟地。

18脚(VA):模拟电源电压,典型值为1.8V~3.3V。

19脚(VA_LINE):线性扩音器电源端,典型值在1.8V~3.3V。

20脚(VA_HP):耳机放大电源端,典型值为0.9V~3.3V。

22,23脚(AOUTB AOUTA):模拟输出端。

24脚(MUTEC):静音控制。

3 CS43L42的硬件连接电路

如系统中芯片工作在STAND_ALONE模式,则将DIF1、DIF0分别设置为低、高电平表示接收左起有效的24位数据。图3是CS43L42的典型外围连接电路。图中的电容C由下式给出:

C=(RL+560)/[4π Fs(RL%26;#183;560)]

4 MP3播放软件设计

MP3文件播放的软件设计任务如下:

(1)初始化EP7212 的DAI接口。

(2)将MP3文件解码成PCM文件并存放于开辟的两个缓冲区(左、右两个声道)。

(3)在FIQ(快速中断请求)中将PCM格式的数据写到DAI接口,同时播放声音(未有数据时播放静音)。

4.1 EP7212的DAI接口介绍和初始化

a. DAI接口

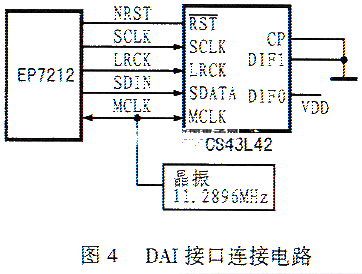

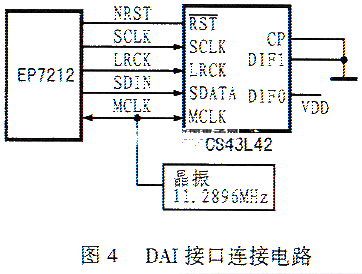

EP7212/7312的数字音频接口(DAI)主要用于支持高质量立体声的音频处理。图4是CS43L42与嵌入式微处理器EP7212的DAI接口电路。该接口主要由以下五个信号组成:

(1)LRCK,左/右帧同步。

(2)SCLK,位时钟,等于MCLK的1/2,每帧有128位。

(3)MCLK,2x过采样时钟,仅在从模式下输入。

(4)SDOUT,数字音频数据输出。

(5)SDIN,数字音频数据输入。

用MSB/Left数据调整格式意味着数据在帧同步信号(LRCK)电位改变后立即被计时。MSB在第一位时是左调整,这与I2S格式相比有些不同,I2S格式的数据在改变电位后要延迟一个时钟。数据帧每帧是128位长,这样每个声道64位长。帧的大小和LRCK的运行周期在EP7212/7312中不能被设置。SCLK可从MCLK中得到,频率等于1/2 MCLK。缺省模式中,DAI处于主模式。该模式下自己产生的MCLK时钟等于9.216MHz。这样,SCLK等于4.608MHz。对于需要SCLK有不同速率的应用,DAI可以被设置成从模式。在从模式下,外部源通过MCLK引脚给MCLK提供主时钟,然后分成两半生成SCLK。不管DAI模式如何设置,SCLK和LRCK通常都设置成输出。数据一般在SCLK的上升沿锁入,在下降沿释放。

DAI接口是一种高质量的数字音频接口,可以连接与DAI接口兼容的音频设备。EP7212 的DAI接口通过位时钟和帧同步时钟产生128bit帧数据。数字音频数据的接收和发送均采用全双工方式,对应于12采样深度的接收FIFO和8采样深度的发送FIFO。在DAI 接口信号中,MCLK是主时钟,它是音频采样频率的256倍,SCLK为音频采样频率的128倍,LRCK固定为采样频率。由于本系统中的MCLK连接外部时钟发生器,频率为11.2896MHz所以采样频率为44.1KHz。其DAI接口时序图如图5所示。

图5

DAI的帧长128bit其中包括一个音频采样数据,在这128bit中,仅有32bit为实际的音频数据,其余输出均为零。左/右时钟作为帧同步信号,左/右时钟从高到低表示右声道的16bit数据,从低到高表示左声道的16bit数据。

b. DAI接口初始化

DAI初始化程序中首先应设置控制寄存器, 接着选择外部时钟有效以及在左发送FIFO数据少于一半时产生中断。然后清除状态寄存器上溢、下溢位,之后使DAI接口、发送FIFO和接收FIFO有效。最后打开DAI中断。

4.2 MP3文件的解码

ARM公司提供有基于ARM处理器音频文件解码库,它能够有效地解码MP3格式的歌曲,而输出16bit立体声PCM数据。

a. 解码库所定义的结构

%26;#183;tSampleRate定义了解码数据PCM的采样率

typedef enum tagSampleRate

{

SR 11 025kHz

SR 12kHz

SR 44 1kHz

SR 48kHz

SR 32kHz

SR Reserved

} tSampleRate

%26;#183;tMPEGStatus 给出了MP3函数返回状态值。

typedef enum tagMPEGStatus

{

eNoErr

eNoSyncword

eCRCError

eBrokenFrame

eEndOfBitstream

eDataOverflow

} tMPEGStatus

%26;#183;tMPEGBitstream给出MPEG比特流的指针,bufptr定义为比特流的字指针,bitidx定义为字中的索引(0-31)。

typedef struct tagMPEGBitstream

{

unsigned int * bufptr

unsigned int bitidx

} tMPEGBitstream

%26;#183;tMPEGHeader包括MPEG音频报头信息,sam-ple_rate为PCM采样频率,samplesperchannel为每个声道的采样数,numchans为声道数,packed info为报头信息,bits required为下一次调用函数需要bit数,free format是指比特流的格式。

typedef struct tagMPEGHeader

{

tSampleRate sample rate

unsigned int samplesperchannel

unsigned int numchans

unsigned int packed info

unsigned int bits required

unsigned int free format

} tMPEGHeader

3 CS43L42的硬件连接电路

如系统中芯片工作在STAND_ALONE模式,则将DIF1、DIF0分别设置为低、高电平表示接收左起有效的24位数据。图3是CS43L42的典型外围连接电路。图中的电容C由下式给出:

C=(RL+560)/[4π Fs(RL%26;#183;560)]

4 MP3播放软件设计

MP3文件播放的软件设计任务如下:

(1)初始化EP7212 的DAI接口。

(2)将MP3文件解码成PCM文件并存放于开辟的两个缓冲区(左、右两个声道)。

(3)在FIQ(快速中断请求)中将PCM格式的数据写到DAI接口,同时播放声音(未有数据时播放静音)。

4.1 EP7212的DAI接口介绍和初始化

a. DAI接口

EP7212/7312的数字音频接口(DAI)主要用于支持高质量立体声的音频处理。图4是CS43L42与嵌入式微处理器EP7212的DAI接口电路。该接口主要由以下五个信号组成:

(1)LRCK,左/右帧同步。

(2)SCLK,位时钟,等于MCLK的1/2,每帧有128位。

(3)MCLK,2x过采样时钟,仅在从模式下输入。

(4)SDOUT,数字音频数据输出。

(5)SDIN,数字音频数据输入。

用MSB/Left数据调整格式意味着数据在帧同步信号(LRCK)电位改变后立即被计时。MSB在第一位时是左调整,这与I2S格式相比有些不同,I2S格式的数据在改变电位后要延迟一个时钟。数据帧每帧是128位长,这样每个声道64位长。帧的大小和LRCK的运行周期在EP7212/7312中不能被设置。SCLK可从MCLK中得到,频率等于1/2 MCLK。缺省模式中,DAI处于主模式。该模式下自己产生的MCLK时钟等于9.216MHz。这样,SCLK等于4.608MHz。对于需要SCLK有不同速率的应用,DAI可以被设置成从模式。在从模式下,外部源通过MCLK引脚给MCLK提供主时钟,然后分成两半生成SCLK。不管DAI模式如何设置,SCLK和LRCK通常都设置成输出。数据一般在SCLK的上升沿锁入,在下降沿释放。

DAI接口是一种高质量的数字音频接口,可以连接与DAI接口兼容的音频设备。EP7212 的DAI接口通过位时钟和帧同步时钟产生128bit帧数据。数字音频数据的接收和发送均采用全双工方式,对应于12采样深度的接收FIFO和8采样深度的发送FIFO。在DAI 接口信号中,MCLK是主时钟,它是音频采样频率的256倍,SCLK为音频采样频率的128倍,LRCK固定为采样频率。由于本系统中的MCLK连接外部时钟发生器,频率为11.2896MHz所以采样频率为44.1KHz。其DAI接口时序图如图5所示。

图5

DAI的帧长128bit其中包括一个音频采样数据,在这128bit中,仅有32bit为实际的音频数据,其余输出均为零。左/右时钟作为帧同步信号,左/右时钟从高到低表示右声道的16bit数据,从低到高表示左声道的16bit数据。

b. DAI接口初始化

DAI初始化程序中首先应设置控制寄存器, 接着选择外部时钟有效以及在左发送FIFO数据少于一半时产生中断。然后清除状态寄存器上溢、下溢位,之后使DAI接口、发送FIFO和接收FIFO有效。最后打开DAI中断。

4.2 MP3文件的解码

ARM公司提供有基于ARM处理器音频文件解码库,它能够有效地解码MP3格式的歌曲,而输出16bit立体声PCM数据。

a. 解码库所定义的结构

%26;#183;tSampleRate定义了解码数据PCM的采样率

typedef enum tagSampleRate

{

SR 11 025kHz

SR 12kHz

SR 44 1kHz

SR 48kHz

SR 32kHz

SR Reserved

} tSampleRate

%26;#183;tMPEGStatus 给出了MP3函数返回状态值。

typedef enum tagMPEGStatus

{

eNoErr

eNoSyncword

eCRCError

eBrokenFrame

eEndOfBitstream

eDataOverflow

} tMPEGStatus

%26;#183;tMPEGBitstream给出MPEG比特流的指针,bufptr定义为比特流的字指针,bitidx定义为字中的索引(0-31)。

typedef struct tagMPEGBitstream

{

unsigned int * bufptr

unsigned int bitidx

} tMPEGBitstream

%26;#183;tMPEGHeader包括MPEG音频报头信息,sam-ple_rate为PCM采样频率,samplesperchannel为每个声道的采样数,numchans为声道数,packed info为报头信息,bits required为下一次调用函数需要bit数,free format是指比特流的格式。

typedef struct tagMPEGHeader

{

tSampleRate sample rate

unsigned int samplesperchannel

unsigned int numchans

unsigned int packed info

unsigned int bits required

unsigned int free format

} tMPEGHeader

b. MP3解码库所提供的函数

%26;#183;InitMP3AudiotMPEGInstance *inst

功能:初始化解码器解码指针。

%26;#183;MP3SearchForSyncwordtMPEGInstance *insttM-PEGBitstream *bslength

功能:查找MPEG数据中的同步字。

%26;#183;MP3DecodeInfotMPEGInstance * insttMPEGBit-stream * bstMPEGHeader * pmpeg hdr

功能:从MPEG帧中获得报头的信息。

%26;#183;MP3DecodeDatatMPEGInstance *inst short *leftshort * right tMPEGBitstream * bs

功能:从MP3数据解码成PCM数据,并将其存到left、right指向的缓冲区中。

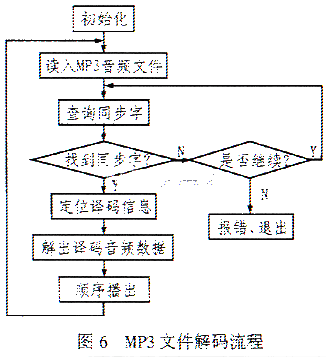

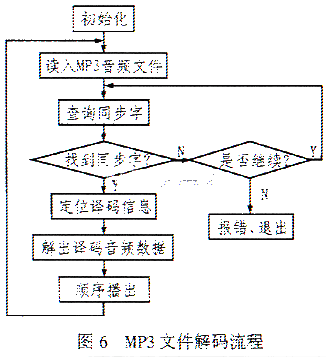

c. MP3程序解码流程及在FIQ中断中的实现

图6所示是该系统中MP3文件的解码流程。该文件可在FIQ中断中实现播放。由于DAI FIFO对应于FIQ中断,因此,它可以通过控制寄存器来设置FIFO的中断方式,并可在程序中将产生中断的位置设置在左发送FIFO中少于四个采样数据时。由于在FIQ中断中保存有MP3解码缓冲区的地址,因此,若在进入FIQ后各写四个采样数据到左右FIFO中,那么,对于44.1kHz文件来说,FIQ发生的速率将为11kHz。为了保证左右FIFO的正确填充,一般需要交替写两个FIFO。此时如果MP3缓冲区无数据,则可写0(静音)到两个FIFO中,这样,程序就可以跳出FIFO中断接着处理数据。需要说明的是:无论程序是否需要录音,都要从接收缓冲区读四个数据,这样可确保DAI FIFO处于同步状态而不会产生失真。另外,在FIQ处理程序的最后,还要清除溢出状态位,这样可以防止FIQ始终中断。

b. MP3解码库所提供的函数

%26;#183;InitMP3AudiotMPEGInstance *inst

功能:初始化解码器解码指针。

%26;#183;MP3SearchForSyncwordtMPEGInstance *insttM-PEGBitstream *bslength

功能:查找MPEG数据中的同步字。

%26;#183;MP3DecodeInfotMPEGInstance * insttMPEGBit-stream * bstMPEGHeader * pmpeg hdr

功能:从MPEG帧中获得报头的信息。

%26;#183;MP3DecodeDatatMPEGInstance *inst short *leftshort * right tMPEGBitstream * bs

功能:从MP3数据解码成PCM数据,并将其存到left、right指向的缓冲区中。

c. MP3程序解码流程及在FIQ中断中的实现

图6所示是该系统中MP3文件的解码流程。该文件可在FIQ中断中实现播放。由于DAI FIFO对应于FIQ中断,因此,它可以通过控制寄存器来设置FIFO的中断方式,并可在程序中将产生中断的位置设置在左发送FIFO中少于四个采样数据时。由于在FIQ中断中保存有MP3解码缓冲区的地址,因此,若在进入FIQ后各写四个采样数据到左右FIFO中,那么,对于44.1kHz文件来说,FIQ发生的速率将为11kHz。为了保证左右FIFO的正确填充,一般需要交替写两个FIFO。此时如果MP3缓冲区无数据,则可写0(静音)到两个FIFO中,这样,程序就可以跳出FIFO中断接着处理数据。需要说明的是:无论程序是否需要录音,都要从接收缓冲区读四个数据,这样可确保DAI FIFO处于同步状态而不会产生失真。另外,在FIQ处理程序的最后,还要清除溢出状态位,这样可以防止FIQ始终中断。

引用地址:用CS43L42音频解码器和EP7212嵌入式处理器设计的MP3文件播放系统

虽然MP3是一种有损压缩方式,但它以极小的声音失真换来较高的压缩比,因此在较多的场合得以应用。尤其是随着数字技术的发展,MP3压缩方式在便携式电子产品中得到了越来越广泛的应用,深受追求时尚、新潮的青年朋友的喜爱。

2 CS43L42播放芯片

CS43L42是CIRRUS LOGIC公司生产的音频解码芯片,

虽然MP3是一种有损压缩方式,但它以极小的声音失真换来较高的压缩比,因此在较多的场合得以应用。尤其是随着数字技术的发展,MP3压缩方式在便携式电子产品中得到了越来越广泛的应用,深受追求时尚、新潮的青年朋友的喜爱。

2 CS43L42播放芯片

CS43L42是CIRRUS LOGIC公司生产的音频解码芯片,

它可工作在1.8~3.3V,关掉线性放大器时功耗仅16mW非常适合于MP3、MD播放器等低功耗场合的应用。该芯片是一款完全意义上的数模转换器,它包括1bit D/A转换、模拟滤波、音量控制、线性电压输出以及耳机放大器。通过改变主频率,其允许的输入采样频率可从2k~100kHz变化。该器件具有数字重音、峰值限制和去加重等特性。此外,由于采用了POPGUARD技术,CS43L42还可有效防止加电、断电时产生的瞬间冲击。

CS43L42具有DAI接口,能够与嵌入式处理器EP7212/7312较好的配合。它具有三种模式:双线模式、SPI模式、STAND ALONE模式。通过引脚CP/SA和AD0/CS/DEM0置相应状态可以设置这三种模式。当CP/SA引脚为低电平时,芯片为STAND ALONE模式,当CP/SA为高电平时,只要检测到引脚AD0/CS/DEM0电平从低到高变化,则进入SPI模式,否则为双线模式。在STAND ALONE模式下,可用SCL/CCLK/DIF1和SDA/CDIN/DIF0引脚来设置数据、左/右时钟以及主时钟之间的关系。在双线模式和SPI模式下,则可以通过对寄存器进行操作来实现静音、声道衰减和音量控制等功能。图1是CS43L42的内部原理图,图2是该芯片的引脚排列示意图,各引脚的功能如下:

1脚(RST):复位信号,低有效。

2脚(LRCK):左/右帧同步。

3脚(SDATA):串行音频数据,数据随串行时钟引入。

4脚(AD0/CS/DEM0):在SPI模式下,用于使能控制端口。

5脚(SCLK/DEM1):位时钟,等于MCLK的1/2,每帧有128位。

6脚(VL):数字电源电压,典型值为1.8V~3.3V。

7脚(MCLK):2x过采样时钟,仅在从模式下输入。

图3

8脚(SCL/CCLK/DIF1):串行控制接口时钟。

9脚(SDA/CDIN/DIF0):串行控制数据输入输出。

10脚(N.C.):无连接,悬空。

11脚(CP/SA):控制模式和等待模式控制。

12脚(VQ_HP):耳机静态电压接口。

13脚(REF_GND):连接到模拟地。

14脚(FILT+):正向基准电压,用于内部采样电路。

15脚(VQ_LINE):线输出静态电压接口。

1621脚(HP_A,HP_B):耳机输出。

17脚(GND):连接到模拟地。

18脚(VA):模拟电源电压,典型值为1.8V~3.3V。

19脚(VA_LINE):线性扩音器电源端,典型值在1.8V~3.3V。

20脚(VA_HP):耳机放大电源端,典型值为0.9V~3.3V。

22,23脚(AOUTB AOUTA):模拟输出端。

24脚(MUTEC):静音控制。

它可工作在1.8~3.3V,关掉线性放大器时功耗仅16mW非常适合于MP3、MD播放器等低功耗场合的应用。该芯片是一款完全意义上的数模转换器,它包括1bit D/A转换、模拟滤波、音量控制、线性电压输出以及耳机放大器。通过改变主频率,其允许的输入采样频率可从2k~100kHz变化。该器件具有数字重音、峰值限制和去加重等特性。此外,由于采用了POPGUARD技术,CS43L42还可有效防止加电、断电时产生的瞬间冲击。

CS43L42具有DAI接口,能够与嵌入式处理器EP7212/7312较好的配合。它具有三种模式:双线模式、SPI模式、STAND ALONE模式。通过引脚CP/SA和AD0/CS/DEM0置相应状态可以设置这三种模式。当CP/SA引脚为低电平时,芯片为STAND ALONE模式,当CP/SA为高电平时,只要检测到引脚AD0/CS/DEM0电平从低到高变化,则进入SPI模式,否则为双线模式。在STAND ALONE模式下,可用SCL/CCLK/DIF1和SDA/CDIN/DIF0引脚来设置数据、左/右时钟以及主时钟之间的关系。在双线模式和SPI模式下,则可以通过对寄存器进行操作来实现静音、声道衰减和音量控制等功能。图1是CS43L42的内部原理图,图2是该芯片的引脚排列示意图,各引脚的功能如下:

1脚(RST):复位信号,低有效。

2脚(LRCK):左/右帧同步。

3脚(SDATA):串行音频数据,数据随串行时钟引入。

4脚(AD0/CS/DEM0):在SPI模式下,用于使能控制端口。

5脚(SCLK/DEM1):位时钟,等于MCLK的1/2,每帧有128位。

6脚(VL):数字电源电压,典型值为1.8V~3.3V。

7脚(MCLK):2x过采样时钟,仅在从模式下输入。

图3

8脚(SCL/CCLK/DIF1):串行控制接口时钟。

9脚(SDA/CDIN/DIF0):串行控制数据输入输出。

10脚(N.C.):无连接,悬空。

11脚(CP/SA):控制模式和等待模式控制。

12脚(VQ_HP):耳机静态电压接口。

13脚(REF_GND):连接到模拟地。

14脚(FILT+):正向基准电压,用于内部采样电路。

15脚(VQ_LINE):线输出静态电压接口。

1621脚(HP_A,HP_B):耳机输出。

17脚(GND):连接到模拟地。

18脚(VA):模拟电源电压,典型值为1.8V~3.3V。

19脚(VA_LINE):线性扩音器电源端,典型值在1.8V~3.3V。

20脚(VA_HP):耳机放大电源端,典型值为0.9V~3.3V。

22,23脚(AOUTB AOUTA):模拟输出端。

24脚(MUTEC):静音控制。

3 CS43L42的硬件连接电路

如系统中芯片工作在STAND_ALONE模式,则将DIF1、DIF0分别设置为低、高电平表示接收左起有效的24位数据。图3是CS43L42的典型外围连接电路。图中的电容C由下式给出:

C=(RL+560)/[4π Fs(RL%26;#183;560)]

4 MP3播放软件设计

MP3文件播放的软件设计任务如下:

(1)初始化EP7212 的DAI接口。

(2)将MP3文件解码成PCM文件并存放于开辟的两个缓冲区(左、右两个声道)。

(3)在FIQ(快速中断请求)中将PCM格式的数据写到DAI接口,同时播放声音(未有数据时播放静音)。

4.1 EP7212的DAI接口介绍和初始化

a. DAI接口

EP7212/7312的数字音频接口(DAI)主要用于支持高质量立体声的音频处理。图4是CS43L42与嵌入式微处理器EP7212的DAI接口电路。该接口主要由以下五个信号组成:

(1)LRCK,左/右帧同步。

(2)SCLK,位时钟,等于MCLK的1/2,每帧有128位。

(3)MCLK,2x过采样时钟,仅在从模式下输入。

(4)SDOUT,数字音频数据输出。

(5)SDIN,数字音频数据输入。

用MSB/Left数据调整格式意味着数据在帧同步信号(LRCK)电位改变后立即被计时。MSB在第一位时是左调整,这与I2S格式相比有些不同,I2S格式的数据在改变电位后要延迟一个时钟。数据帧每帧是128位长,这样每个声道64位长。帧的大小和LRCK的运行周期在EP7212/7312中不能被设置。SCLK可从MCLK中得到,频率等于1/2 MCLK。缺省模式中,DAI处于主模式。该模式下自己产生的MCLK时钟等于9.216MHz。这样,SCLK等于4.608MHz。对于需要SCLK有不同速率的应用,DAI可以被设置成从模式。在从模式下,外部源通过MCLK引脚给MCLK提供主时钟,然后分成两半生成SCLK。不管DAI模式如何设置,SCLK和LRCK通常都设置成输出。数据一般在SCLK的上升沿锁入,在下降沿释放。

DAI接口是一种高质量的数字音频接口,可以连接与DAI接口兼容的音频设备。EP7212 的DAI接口通过位时钟和帧同步时钟产生128bit帧数据。数字音频数据的接收和发送均采用全双工方式,对应于12采样深度的接收FIFO和8采样深度的发送FIFO。在DAI 接口信号中,MCLK是主时钟,它是音频采样频率的256倍,SCLK为音频采样频率的128倍,LRCK固定为采样频率。由于本系统中的MCLK连接外部时钟发生器,频率为11.2896MHz所以采样频率为44.1KHz。其DAI接口时序图如图5所示。

图5

DAI的帧长128bit其中包括一个音频采样数据,在这128bit中,仅有32bit为实际的音频数据,其余输出均为零。左/右时钟作为帧同步信号,左/右时钟从高到低表示右声道的16bit数据,从低到高表示左声道的16bit数据。

b. DAI接口初始化

DAI初始化程序中首先应设置控制寄存器, 接着选择外部时钟有效以及在左发送FIFO数据少于一半时产生中断。然后清除状态寄存器上溢、下溢位,之后使DAI接口、发送FIFO和接收FIFO有效。最后打开DAI中断。

4.2 MP3文件的解码

ARM公司提供有基于ARM处理器音频文件解码库,它能够有效地解码MP3格式的歌曲,而输出16bit立体声PCM数据。

a. 解码库所定义的结构

%26;#183;tSampleRate定义了解码数据PCM的采样率

typedef enum tagSampleRate

{

SR 11 025kHz

SR 12kHz

SR 44 1kHz

SR 48kHz

SR 32kHz

SR Reserved

} tSampleRate

%26;#183;tMPEGStatus 给出了MP3函数返回状态值。

typedef enum tagMPEGStatus

{

eNoErr

eNoSyncword

eCRCError

eBrokenFrame

eEndOfBitstream

eDataOverflow

} tMPEGStatus

%26;#183;tMPEGBitstream给出MPEG比特流的指针,bufptr定义为比特流的字指针,bitidx定义为字中的索引(0-31)。

typedef struct tagMPEGBitstream

{

unsigned int * bufptr

unsigned int bitidx

} tMPEGBitstream

%26;#183;tMPEGHeader包括MPEG音频报头信息,sam-ple_rate为PCM采样频率,samplesperchannel为每个声道的采样数,numchans为声道数,packed info为报头信息,bits required为下一次调用函数需要bit数,free format是指比特流的格式。

typedef struct tagMPEGHeader

{

tSampleRate sample rate

unsigned int samplesperchannel

unsigned int numchans

unsigned int packed info

unsigned int bits required

unsigned int free format

} tMPEGHeader

3 CS43L42的硬件连接电路

如系统中芯片工作在STAND_ALONE模式,则将DIF1、DIF0分别设置为低、高电平表示接收左起有效的24位数据。图3是CS43L42的典型外围连接电路。图中的电容C由下式给出:

C=(RL+560)/[4π Fs(RL%26;#183;560)]

4 MP3播放软件设计

MP3文件播放的软件设计任务如下:

(1)初始化EP7212 的DAI接口。

(2)将MP3文件解码成PCM文件并存放于开辟的两个缓冲区(左、右两个声道)。

(3)在FIQ(快速中断请求)中将PCM格式的数据写到DAI接口,同时播放声音(未有数据时播放静音)。

4.1 EP7212的DAI接口介绍和初始化

a. DAI接口

EP7212/7312的数字音频接口(DAI)主要用于支持高质量立体声的音频处理。图4是CS43L42与嵌入式微处理器EP7212的DAI接口电路。该接口主要由以下五个信号组成:

(1)LRCK,左/右帧同步。

(2)SCLK,位时钟,等于MCLK的1/2,每帧有128位。

(3)MCLK,2x过采样时钟,仅在从模式下输入。

(4)SDOUT,数字音频数据输出。

(5)SDIN,数字音频数据输入。

用MSB/Left数据调整格式意味着数据在帧同步信号(LRCK)电位改变后立即被计时。MSB在第一位时是左调整,这与I2S格式相比有些不同,I2S格式的数据在改变电位后要延迟一个时钟。数据帧每帧是128位长,这样每个声道64位长。帧的大小和LRCK的运行周期在EP7212/7312中不能被设置。SCLK可从MCLK中得到,频率等于1/2 MCLK。缺省模式中,DAI处于主模式。该模式下自己产生的MCLK时钟等于9.216MHz。这样,SCLK等于4.608MHz。对于需要SCLK有不同速率的应用,DAI可以被设置成从模式。在从模式下,外部源通过MCLK引脚给MCLK提供主时钟,然后分成两半生成SCLK。不管DAI模式如何设置,SCLK和LRCK通常都设置成输出。数据一般在SCLK的上升沿锁入,在下降沿释放。

DAI接口是一种高质量的数字音频接口,可以连接与DAI接口兼容的音频设备。EP7212 的DAI接口通过位时钟和帧同步时钟产生128bit帧数据。数字音频数据的接收和发送均采用全双工方式,对应于12采样深度的接收FIFO和8采样深度的发送FIFO。在DAI 接口信号中,MCLK是主时钟,它是音频采样频率的256倍,SCLK为音频采样频率的128倍,LRCK固定为采样频率。由于本系统中的MCLK连接外部时钟发生器,频率为11.2896MHz所以采样频率为44.1KHz。其DAI接口时序图如图5所示。

图5

DAI的帧长128bit其中包括一个音频采样数据,在这128bit中,仅有32bit为实际的音频数据,其余输出均为零。左/右时钟作为帧同步信号,左/右时钟从高到低表示右声道的16bit数据,从低到高表示左声道的16bit数据。

b. DAI接口初始化

DAI初始化程序中首先应设置控制寄存器, 接着选择外部时钟有效以及在左发送FIFO数据少于一半时产生中断。然后清除状态寄存器上溢、下溢位,之后使DAI接口、发送FIFO和接收FIFO有效。最后打开DAI中断。

4.2 MP3文件的解码

ARM公司提供有基于ARM处理器音频文件解码库,它能够有效地解码MP3格式的歌曲,而输出16bit立体声PCM数据。

a. 解码库所定义的结构

%26;#183;tSampleRate定义了解码数据PCM的采样率

typedef enum tagSampleRate

{

SR 11 025kHz

SR 12kHz

SR 44 1kHz

SR 48kHz

SR 32kHz

SR Reserved

} tSampleRate

%26;#183;tMPEGStatus 给出了MP3函数返回状态值。

typedef enum tagMPEGStatus

{

eNoErr

eNoSyncword

eCRCError

eBrokenFrame

eEndOfBitstream

eDataOverflow

} tMPEGStatus

%26;#183;tMPEGBitstream给出MPEG比特流的指针,bufptr定义为比特流的字指针,bitidx定义为字中的索引(0-31)。

typedef struct tagMPEGBitstream

{

unsigned int * bufptr

unsigned int bitidx

} tMPEGBitstream

%26;#183;tMPEGHeader包括MPEG音频报头信息,sam-ple_rate为PCM采样频率,samplesperchannel为每个声道的采样数,numchans为声道数,packed info为报头信息,bits required为下一次调用函数需要bit数,free format是指比特流的格式。

typedef struct tagMPEGHeader

{

tSampleRate sample rate

unsigned int samplesperchannel

unsigned int numchans

unsigned int packed info

unsigned int bits required

unsigned int free format

} tMPEGHeader

b. MP3解码库所提供的函数

%26;#183;InitMP3AudiotMPEGInstance *inst

功能:初始化解码器解码指针。

%26;#183;MP3SearchForSyncwordtMPEGInstance *insttM-PEGBitstream *bslength

功能:查找MPEG数据中的同步字。

%26;#183;MP3DecodeInfotMPEGInstance * insttMPEGBit-stream * bstMPEGHeader * pmpeg hdr

功能:从MPEG帧中获得报头的信息。

%26;#183;MP3DecodeDatatMPEGInstance *inst short *leftshort * right tMPEGBitstream * bs

功能:从MP3数据解码成PCM数据,并将其存到left、right指向的缓冲区中。

c. MP3程序解码流程及在FIQ中断中的实现

图6所示是该系统中MP3文件的解码流程。该文件可在FIQ中断中实现播放。由于DAI FIFO对应于FIQ中断,因此,它可以通过控制寄存器来设置FIFO的中断方式,并可在程序中将产生中断的位置设置在左发送FIFO中少于四个采样数据时。由于在FIQ中断中保存有MP3解码缓冲区的地址,因此,若在进入FIQ后各写四个采样数据到左右FIFO中,那么,对于44.1kHz文件来说,FIQ发生的速率将为11kHz。为了保证左右FIFO的正确填充,一般需要交替写两个FIFO。此时如果MP3缓冲区无数据,则可写0(静音)到两个FIFO中,这样,程序就可以跳出FIFO中断接着处理数据。需要说明的是:无论程序是否需要录音,都要从接收缓冲区读四个数据,这样可确保DAI FIFO处于同步状态而不会产生失真。另外,在FIQ处理程序的最后,还要清除溢出状态位,这样可以防止FIQ始终中断。

b. MP3解码库所提供的函数

%26;#183;InitMP3AudiotMPEGInstance *inst

功能:初始化解码器解码指针。

%26;#183;MP3SearchForSyncwordtMPEGInstance *insttM-PEGBitstream *bslength

功能:查找MPEG数据中的同步字。

%26;#183;MP3DecodeInfotMPEGInstance * insttMPEGBit-stream * bstMPEGHeader * pmpeg hdr

功能:从MPEG帧中获得报头的信息。

%26;#183;MP3DecodeDatatMPEGInstance *inst short *leftshort * right tMPEGBitstream * bs

功能:从MP3数据解码成PCM数据,并将其存到left、right指向的缓冲区中。

c. MP3程序解码流程及在FIQ中断中的实现

图6所示是该系统中MP3文件的解码流程。该文件可在FIQ中断中实现播放。由于DAI FIFO对应于FIQ中断,因此,它可以通过控制寄存器来设置FIFO的中断方式,并可在程序中将产生中断的位置设置在左发送FIFO中少于四个采样数据时。由于在FIQ中断中保存有MP3解码缓冲区的地址,因此,若在进入FIQ后各写四个采样数据到左右FIFO中,那么,对于44.1kHz文件来说,FIQ发生的速率将为11kHz。为了保证左右FIFO的正确填充,一般需要交替写两个FIFO。此时如果MP3缓冲区无数据,则可写0(静音)到两个FIFO中,这样,程序就可以跳出FIFO中断接着处理数据。需要说明的是:无论程序是否需要录音,都要从接收缓冲区读四个数据,这样可确保DAI FIFO处于同步状态而不会产生失真。另外,在FIQ处理程序的最后,还要清除溢出状态位,这样可以防止FIQ始终中断。

上一篇:利用代间差分遗传算法优化分形图像编码速度

下一篇:如何降低音频功率放大器瞬时杂音

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新手机便携文章

- 苹果遭4000万英国iCloud用户集体诉讼,面临276亿元索赔

- 消息称苹果、三星超薄高密度电池均开发失败,iPhone 17 Air、Galaxy S25 Slim手机“变厚”

- 美光亮相2024年进博会,持续深耕中国市场,引领可持续发展

- Qorvo:创新技术引领下一代移动产业

- BOE独供努比亚和红魔旗舰新品 全新一代屏下显示技术引领行业迈入真全面屏时代

- OPPO与香港理工大学续约合作 升级创新研究中心,拓展AI影像新边界

- 古尔曼:Vision Pro 将升级芯片,苹果还考虑推出与 iPhone 连接的眼镜

- 汇顶助力,一加13新十年首款旗舰全方位实现“样样超Pro”

- 汇顶科技助力iQOO 13打造电竞性能旗舰新体验

更多精选电路图

更多热门文章

更多每日新闻

- Allegro MicroSystems 在 2024 年德国慕尼黑电子展上推出先进的磁性和电感式位置感测解决方案

- 左手车钥匙,右手活体检测雷达,UWB上车势在必行!

- 狂飙十年,国产CIS挤上牌桌

- 神盾短刀电池+雷神EM-i超级电混,吉利新能源甩出了两张“王炸”

- 浅谈功能安全之故障(fault),错误(error),失效(failure)

- 智能汽车2.0周期,这几大核心产业链迎来重大机会!

- 美日研发新型电池,宁德时代面临挑战?中国新能源电池产业如何应对?

- Rambus推出业界首款HBM 4控制器IP:背后有哪些技术细节?

- 村田推出高精度汽车用6轴惯性传感器

- 福特获得预充电报警专利 有助于节约成本和应对紧急情况

更多往期活动

11月16日历史上的今天

厂商技术中心

LM111MW8

LM111MW8

京公网安备 11010802033920号

京公网安备 11010802033920号