摘要:简要介绍了MOTOROLA公司的24位定点数字信号处理器DSP56362的并行引导过程和特点。并结合实际,提出了一种双引导模式,给出了具体的实现方法。通过这种双引导模式,巧妙地达到了系统的要求。另外,介绍了采用DSP软件编程来实现FLASH擦除和读写方法。

关键词:DSP56362;Bootstrap;双引导模式;命令字序列

1 引言

在脱机运行的DSP系统中,用户代码往往都需要在上电后自动装载运行。目前,大多数的DSP内部都有固化的引导装载(Bootload)程序,它能在系统加电时,自动将一段存储在外部非易失性存储器中的程序代码移植到内部的高速存储器单元中去执行。采用这种方式,既可利用外部的存储单元来扩展DSP本身有限的ROM资源,又充分发挥了DSP内部资源的效能。

因为用户代码在一段时间内是相对固定的,所以可以将其固化在非易失性存贮器中。而如果将代码掩膜到DSP内部ROM中去一方面要受到容量以及价格的限制,另一方面,系统代码升级也不是很灵活方便。FLASH是一种高密度、非易失性的电可擦写存储器,其单位存储比特的价格比传统的EPROM要低,十分适合低功耗、小尺寸和高性能的脱机系统。此外,除了可以采用专用的硬件编程器把程序代码烧入FLASH中之外,

因为用户代码在一段时间内是相对固定的,所以可以将其固化在非易失性存贮器中。而如果将代码掩膜到DSP内部ROM中去一方面要受到容量以及价格的限制,另一方面,系统代码升级也不是很灵活方便。FLASH是一种高密度、非易失性的电可擦写存储器,其单位存储比特的价格比传统的EPROM要低,十分适合低功耗、小尺寸和高性能的脱机系统。此外,除了可以采用专用的硬件编程器把程序代码烧入FLASH中之外,

也可以直接利用DSP通过软件编程来实现。本文论述的正是如何通过DSP软件编程来实现对FLASH的读写操作,同时介绍了系统双引导装载方案的实现方法。

2 系统描述

本系统是基于MOTOROLA公司DSP56362芯片构建的数字音效处理系统中的一部分,整个数字音效处理系统的系统框图如图1所示。

DSP56362是一款24位通用定点数字信号处理器。它采用高性能单时钟指令周期的DSP56300内核和Motorola Symphony DSP的音频处理性能相结合的方法来实现具有运算速度快(100MIPS)精度高(24bit),外设接口丰富(具有增强型串行音频接口ESAI、并行主机接口HI08、串行主机接口SHI、数字音频接口DAX等),价格低廉等诸多优点,特别适用于音频处理。其24位的处理精度配合20位的A/D(PCM1800)和24位的D/APCM1744使得整个系统具有很高的动态范围(96dB以上)。它高达100MIPS的运算速度保证了算法处理的实时性。其增强型串行音频接口ESAI可以很方便地与音频A/D、D/A直接通过I2S协议进行连接。通过8bit的并行主机接口HI08可以方便地与负责键盘控制和LED显示的单片机89C51进行通信。

FLASH选用SST公司的39LV010其存储容量为128k%26;#215;8bit,采用3.3V供电,读写周期为70ns,支持块擦除与字节编程,是一款高性价比存储芯片。

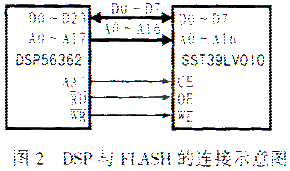

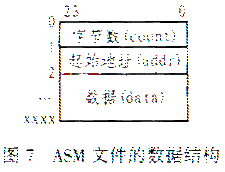

DSP与外部FLASH的连接示意图如图2所示。图中,DSP的AA1脚和FLASH的片选信号脚CE相连。

DSP56362的4个地址属性寄存器AAR[3~0]是24位读写寄存器,它们的值可用于控制DSP芯片的AA[3~0]引脚的状态,当某个AAR寄存器中的基址与外部访问指令存取范围相匹配时,由这个AAR定义的相应地址空间(X数据、Y数据或程序)将被相应的AA线选通。在本系统中,正是把DSP的AA1作为FLASH的片选线。AA1脚相应的AAR1寄存器的值设为0xD00811H,当访问地址的高8位为11010000时,外部FLASH被选通。

也可以直接利用DSP通过软件编程来实现。本文论述的正是如何通过DSP软件编程来实现对FLASH的读写操作,同时介绍了系统双引导装载方案的实现方法。

2 系统描述

本系统是基于MOTOROLA公司DSP56362芯片构建的数字音效处理系统中的一部分,整个数字音效处理系统的系统框图如图1所示。

DSP56362是一款24位通用定点数字信号处理器。它采用高性能单时钟指令周期的DSP56300内核和Motorola Symphony DSP的音频处理性能相结合的方法来实现具有运算速度快(100MIPS)精度高(24bit),外设接口丰富(具有增强型串行音频接口ESAI、并行主机接口HI08、串行主机接口SHI、数字音频接口DAX等),价格低廉等诸多优点,特别适用于音频处理。其24位的处理精度配合20位的A/D(PCM1800)和24位的D/APCM1744使得整个系统具有很高的动态范围(96dB以上)。它高达100MIPS的运算速度保证了算法处理的实时性。其增强型串行音频接口ESAI可以很方便地与音频A/D、D/A直接通过I2S协议进行连接。通过8bit的并行主机接口HI08可以方便地与负责键盘控制和LED显示的单片机89C51进行通信。

FLASH选用SST公司的39LV010其存储容量为128k%26;#215;8bit,采用3.3V供电,读写周期为70ns,支持块擦除与字节编程,是一款高性价比存储芯片。

DSP与外部FLASH的连接示意图如图2所示。图中,DSP的AA1脚和FLASH的片选信号脚CE相连。

DSP56362的4个地址属性寄存器AAR[3~0]是24位读写寄存器,它们的值可用于控制DSP芯片的AA[3~0]引脚的状态,当某个AAR寄存器中的基址与外部访问指令存取范围相匹配时,由这个AAR定义的相应地址空间(X数据、Y数据或程序)将被相应的AA线选通。在本系统中,正是把DSP的AA1作为FLASH的片选线。AA1脚相应的AAR1寄存器的值设为0xD00811H,当访问地址的高8位为11010000时,外部FLASH被选通。

通过设置DSP的总线控制寄存器BCR,可以设置访问外部存储器时插入的等待状态的个数。在本系统中,FLASH的存取周期为70ns,为了保证FLASH的正确读写,一般要插入32个等待状态。

3 DSP56362的引导过程

在DSP56362内部的0xFF0000H-0xFF00BFH地址范围内有Motorola定制的24位192字的Bootstrap ROM。该ROM内的Bootstrap引导程序可以通过用户设置的DSP引导模式信号线,将用户程序从外部的8位EPROM、EEPROM、FLASH、 SHI接口或者HDI接口引导到DSP内部的高速RAM中全速运行。

当DSP56362硬件复位后,它将首先采样外部的MODA、MODB、MODC和MODD信号线,并将它们的状态写入工作模式寄存器OMROperating Mode Reg-ister的MA、MB、MC和MD位,然后使程序指针指向0xFF0000H去执行Bootstrap引导程序,Bootstrap引导程序通过对OMR的MA、MB、MC和MD位进行判断来决定选择哪种引导模式。主要的引导模式如表1所列。

表1 DSP56362 Bootstrap的引导模式

MODD

MODC

MODB

MODA

描 述

0

0

0

1

从字节存储器引导

0

0

1

0

跳转到程序ROM起始地址

0

1

0

1

从串行主机接口SHI引导(SPI从模式)

0

1

1

0

从串行主机接口SHI引导(I2C从模式,时钟静止使能)

0

1

1

1

从串行主机接口SHI引导(I2C从模式,时钟静止关闭)

1

0

0

1

内部测试保留

1

1

0

0

从并行主机接口HDI08引导(ISA模式)

1

1

0

1

从并行主机接口HDI08引导(HC11非复用模式)

1

1

1

0

从并行主机接口HDI08引导(8051复用总线模式)

1

1

1

1

从并行主机接口HDI08引导(68302总线模式)

在本系统中,由于程序保存在外部的FLASH里,所以采用的引导模式为第一种即从字节存储器引导。在这种模式下Bootstrap程序将从地址0xD00000H处开始加载外部数据,并采用以下数据格式从外部接口下载用户的系统程序:

(1) 最开始的3个字节用于定义系统程序的总字数(24位)。

通过设置DSP的总线控制寄存器BCR,可以设置访问外部存储器时插入的等待状态的个数。在本系统中,FLASH的存取周期为70ns,为了保证FLASH的正确读写,一般要插入32个等待状态。

3 DSP56362的引导过程

在DSP56362内部的0xFF0000H-0xFF00BFH地址范围内有Motorola定制的24位192字的Bootstrap ROM。该ROM内的Bootstrap引导程序可以通过用户设置的DSP引导模式信号线,将用户程序从外部的8位EPROM、EEPROM、FLASH、 SHI接口或者HDI接口引导到DSP内部的高速RAM中全速运行。

当DSP56362硬件复位后,它将首先采样外部的MODA、MODB、MODC和MODD信号线,并将它们的状态写入工作模式寄存器OMROperating Mode Reg-ister的MA、MB、MC和MD位,然后使程序指针指向0xFF0000H去执行Bootstrap引导程序,Bootstrap引导程序通过对OMR的MA、MB、MC和MD位进行判断来决定选择哪种引导模式。主要的引导模式如表1所列。

表1 DSP56362 Bootstrap的引导模式

MODD

MODC

MODB

MODA

描 述

0

0

0

1

从字节存储器引导

0

0

1

0

跳转到程序ROM起始地址

0

1

0

1

从串行主机接口SHI引导(SPI从模式)

0

1

1

0

从串行主机接口SHI引导(I2C从模式,时钟静止使能)

0

1

1

1

从串行主机接口SHI引导(I2C从模式,时钟静止关闭)

1

0

0

1

内部测试保留

1

1

0

0

从并行主机接口HDI08引导(ISA模式)

1

1

0

1

从并行主机接口HDI08引导(HC11非复用模式)

1

1

1

0

从并行主机接口HDI08引导(8051复用总线模式)

1

1

1

1

从并行主机接口HDI08引导(68302总线模式)

在本系统中,由于程序保存在外部的FLASH里,所以采用的引导模式为第一种即从字节存储器引导。在这种模式下Bootstrap程序将从地址0xD00000H处开始加载外部数据,并采用以下数据格式从外部接口下载用户的系统程序:

(1) 最开始的3个字节用于定义系统程序的总字数(24位)。

(2) 接着的3个字节用于定义系统程序下载到DSP56362程序存储器的目的地址。

(3) 其余是用户的系统程序(每个24位的字由三个字节组成),这些程序将存储在DSP程序存储器内连续的地址空间里。

Bootstrap引导程序要求系统程序在外部FLASH中以地位字节(LSB)在前的顺序排列每个24位字的3个字节。DSP的引导程序一旦完成数据的下载,将马上跳转到内部程序存储器的起始目的地址开始运行用户的系统程序。

4 双引导装载方法

4.1 DSP56362的片内内存分配

DSP56362采用增强型哈佛结构,片内空间可分为程序空间、X数据空间、Y数据空间,每个空间都有一套独立的24位地址总线和数据总线。在缺省情况下,DSP片内的RAM分配情况为:3kB程序RAM、5.5kB X数据RAM和5.5kB Y数据RAM。通过设置内存切换模式(MS=1)可以将2kB的Y数据RAM映射到程序RAM中,此时的片内RAM分配为:5kB程序RAM、5.5kB X数据RAM和3.5kB Y数据RAM。考虑到本系统对程序空间的需求量较大,而数据RAM相对较多,且系统对内部数据RAM的需求并不是很大,因此,将DSP设置成内存切换模式比较好。DSP56362在内存切换模式下(MS=1)的内存映像图如图3所示。

4.2 直接使用Bootstrap引导程序的问题

DSP的内存切换模式需要通过软件指令对OMR寄存器进行设置来实现。由于只有在该指令执行后才能生效,这样就产生了一个矛盾。因为若在系统程序开始时将DSP设置为内存切换模式,那么,往往希望DSP能装载5kB的程序指令,但是,DSP的Bootstrap引导程序是在系统复位后立即执行的,此时DSP处于缺省(MS=0)状态,程序RAM只有3kB,如果此时外部的指令代码的大小超过了这个限制,引导程序就不能把它们加载进去,而当这条设置指令生效时,虽然DSP的程序空间又增加了2kB,但是引导程序已经结束,因而这2kB的程序空间实际上没有被利用。

(2) 接着的3个字节用于定义系统程序下载到DSP56362程序存储器的目的地址。

(3) 其余是用户的系统程序(每个24位的字由三个字节组成),这些程序将存储在DSP程序存储器内连续的地址空间里。

Bootstrap引导程序要求系统程序在外部FLASH中以地位字节(LSB)在前的顺序排列每个24位字的3个字节。DSP的引导程序一旦完成数据的下载,将马上跳转到内部程序存储器的起始目的地址开始运行用户的系统程序。

4 双引导装载方法

4.1 DSP56362的片内内存分配

DSP56362采用增强型哈佛结构,片内空间可分为程序空间、X数据空间、Y数据空间,每个空间都有一套独立的24位地址总线和数据总线。在缺省情况下,DSP片内的RAM分配情况为:3kB程序RAM、5.5kB X数据RAM和5.5kB Y数据RAM。通过设置内存切换模式(MS=1)可以将2kB的Y数据RAM映射到程序RAM中,此时的片内RAM分配为:5kB程序RAM、5.5kB X数据RAM和3.5kB Y数据RAM。考虑到本系统对程序空间的需求量较大,而数据RAM相对较多,且系统对内部数据RAM的需求并不是很大,因此,将DSP设置成内存切换模式比较好。DSP56362在内存切换模式下(MS=1)的内存映像图如图3所示。

4.2 直接使用Bootstrap引导程序的问题

DSP的内存切换模式需要通过软件指令对OMR寄存器进行设置来实现。由于只有在该指令执行后才能生效,这样就产生了一个矛盾。因为若在系统程序开始时将DSP设置为内存切换模式,那么,往往希望DSP能装载5kB的程序指令,但是,DSP的Bootstrap引导程序是在系统复位后立即执行的,此时DSP处于缺省(MS=0)状态,程序RAM只有3kB,如果此时外部的指令代码的大小超过了这个限制,引导程序就不能把它们加载进去,而当这条设置指令生效时,虽然DSP的程序空间又增加了2kB,但是引导程序已经结束,因而这2kB的程序空间实际上没有被利用。

另外,从DSP的Bootstrap程序流程可以看出,这个引导程序只能将系统的程序代码数据加载到DSP内部的程序RAM,而不能将数据加载到DSP内部的X数据RAM、Y数据RAM,这样,那些需要在数据区内定义常数的程序将无法正常运行。

4.3 双引导模式

为了解决以上问题,本文提出了一种双引导模式。具体思路是:在系统程序的开始处,设计一个用户自己的引导模块,用这个模块先对DSP内部的OMR寄存器进行相应的内存切换设置,以使DSP内部的程序RAM扩大为5kB。然后参照DSP的Boot-strap引导程序分别对系统的X、Y及P区的数据进行加载。同时在将程序烧录到FLASH时采用地址隔离的方式将引导模块与系统程序分开存放,引导模块作为一段独立的程序放在首地址为0xD00000H的存储区。于是,对于DSP的Bootstrap引导程序来说,它需要引导的不是整个系统程序,而仅仅是这个引导模块,另外加载完这个模块后就立即跳转到内部程序RAM中执行,此时引导模块已获得CPU控制权,它在完成内存切换后将继续引导系统程序的其他部分。采用这种两次引导的方法,不但使X、Y区的数据可以按照程序的要求进行初始化,而且DSP的程序指令空间可以预先设置成5kB,从而非常巧妙地达到了系统的要求。该双引导模式的引导模块程序流程如图4所示。

5 FALSH的擦除和读写

为了使系统能够脱机运行,应当把系统程序烧录到外部FLASH中去。除了可以用专用的编程器把代码烧入FLASH中外,还可以用软件编程的方法由DSP来实现同样的功能。本系统正是采用这种软件编程的方法实现对FLASH的擦除和读写。

5.1 地址映射

利用DSP擦除和读写FLASH必然会牵涉到FLASH中的地址在DSP中的映射方式。DSP56362的内存映像图已在图3中给出。本系统采用的是128kB的FLASH,其地址范围为:0x000000H~0x1FFFFH。假设FLASH的起始地址0x0000H和DSP的起始地址0x000000H重合,那么FLASH中只有对应于DSP外部空间的那部分地址空间才是DSP可见的。为了使DSP能够访问全部的外部FLASH空间,设计时必须进行地址重映射。

本系统实际用到的FLASH的存储容量不足64kB,也就是说,当访问外部FLASH时,真正起作用的地址线是A0~A15,而高位地址线A23~A16可以为任意值。因此,可以考虑给访问地址加一个偏移量0xD00000H,以将FLASH的地址空间映射到DSP内部X数据RAM中,映射后的地址范围是:0xD00000H~0xD0FFFFH。重映射后的FLASH地址空间落在X数据RAM的外部保留区内,这在DSP中是可见的。

5.2 擦除和读写过程

在DSP将数据写入FLASH之前,先要删除数据所在块,然后才能重新写入。在擦除和写操作之前都要执行相应的命令字序列,即在指定的FLASH地址处写入指定的指令代码,而读操作则可以直接进行。FLASH的擦除和写入流程图分别如图5、图6所示。在本系统中,由于采用了双引导模式,所以首先要将引导程序写入FLASH,然后再分别将用户程序的P区数据、X区数据、Y区数据写入FLASH。

在利用DSP软件编程进行烧录时,可以从目标文件中提取出将要写入FLASH的数据,然后将这些数据打包成一个asm文件,再在烧录程序中将这个asm文件包含进来。接着对烧录程序进行编译、链接,以产生一个目标文件。最后,通过JTAG口将目标文件下载到DSP中运行,这样,DSP就会通过其外部数据线将打包好的asm文件中的数据写入FLASH。在本系统中,引导程序和用户程序将分4次烧入FLASH为此要分别将引导程序、用户程序P区数据、用户程序X区数据、用户程序Y区数据打包成asm文件。打包一个asm文件的具体步骤如下:

(1)调用MOTOROLA公司提供的ASM56300和DSPLNK程序对源文件进行编译、链接,以产生一个cld格式的目标文件。

(2)调用MOTOROLA公司提供的SREC程序将cld格式的目标文件转换成MOTOROLA公司的S-RECORD文件格式,可将目标文件中的P区数据、X区数据、Y区数据提取出来并生成3个文件,其后缀分别为p、x、y。

另外,从DSP的Bootstrap程序流程可以看出,这个引导程序只能将系统的程序代码数据加载到DSP内部的程序RAM,而不能将数据加载到DSP内部的X数据RAM、Y数据RAM,这样,那些需要在数据区内定义常数的程序将无法正常运行。

4.3 双引导模式

为了解决以上问题,本文提出了一种双引导模式。具体思路是:在系统程序的开始处,设计一个用户自己的引导模块,用这个模块先对DSP内部的OMR寄存器进行相应的内存切换设置,以使DSP内部的程序RAM扩大为5kB。然后参照DSP的Boot-strap引导程序分别对系统的X、Y及P区的数据进行加载。同时在将程序烧录到FLASH时采用地址隔离的方式将引导模块与系统程序分开存放,引导模块作为一段独立的程序放在首地址为0xD00000H的存储区。于是,对于DSP的Bootstrap引导程序来说,它需要引导的不是整个系统程序,而仅仅是这个引导模块,另外加载完这个模块后就立即跳转到内部程序RAM中执行,此时引导模块已获得CPU控制权,它在完成内存切换后将继续引导系统程序的其他部分。采用这种两次引导的方法,不但使X、Y区的数据可以按照程序的要求进行初始化,而且DSP的程序指令空间可以预先设置成5kB,从而非常巧妙地达到了系统的要求。该双引导模式的引导模块程序流程如图4所示。

5 FALSH的擦除和读写

为了使系统能够脱机运行,应当把系统程序烧录到外部FLASH中去。除了可以用专用的编程器把代码烧入FLASH中外,还可以用软件编程的方法由DSP来实现同样的功能。本系统正是采用这种软件编程的方法实现对FLASH的擦除和读写。

5.1 地址映射

利用DSP擦除和读写FLASH必然会牵涉到FLASH中的地址在DSP中的映射方式。DSP56362的内存映像图已在图3中给出。本系统采用的是128kB的FLASH,其地址范围为:0x000000H~0x1FFFFH。假设FLASH的起始地址0x0000H和DSP的起始地址0x000000H重合,那么FLASH中只有对应于DSP外部空间的那部分地址空间才是DSP可见的。为了使DSP能够访问全部的外部FLASH空间,设计时必须进行地址重映射。

本系统实际用到的FLASH的存储容量不足64kB,也就是说,当访问外部FLASH时,真正起作用的地址线是A0~A15,而高位地址线A23~A16可以为任意值。因此,可以考虑给访问地址加一个偏移量0xD00000H,以将FLASH的地址空间映射到DSP内部X数据RAM中,映射后的地址范围是:0xD00000H~0xD0FFFFH。重映射后的FLASH地址空间落在X数据RAM的外部保留区内,这在DSP中是可见的。

5.2 擦除和读写过程

在DSP将数据写入FLASH之前,先要删除数据所在块,然后才能重新写入。在擦除和写操作之前都要执行相应的命令字序列,即在指定的FLASH地址处写入指定的指令代码,而读操作则可以直接进行。FLASH的擦除和写入流程图分别如图5、图6所示。在本系统中,由于采用了双引导模式,所以首先要将引导程序写入FLASH,然后再分别将用户程序的P区数据、X区数据、Y区数据写入FLASH。

在利用DSP软件编程进行烧录时,可以从目标文件中提取出将要写入FLASH的数据,然后将这些数据打包成一个asm文件,再在烧录程序中将这个asm文件包含进来。接着对烧录程序进行编译、链接,以产生一个目标文件。最后,通过JTAG口将目标文件下载到DSP中运行,这样,DSP就会通过其外部数据线将打包好的asm文件中的数据写入FLASH。在本系统中,引导程序和用户程序将分4次烧入FLASH为此要分别将引导程序、用户程序P区数据、用户程序X区数据、用户程序Y区数据打包成asm文件。打包一个asm文件的具体步骤如下:

(1)调用MOTOROLA公司提供的ASM56300和DSPLNK程序对源文件进行编译、链接,以产生一个cld格式的目标文件。

(2)调用MOTOROLA公司提供的SREC程序将cld格式的目标文件转换成MOTOROLA公司的S-RECORD文件格式,可将目标文件中的P区数据、X区数据、Y区数据提取出来并生成3个文件,其后缀分别为p、x、y。

(3)调用Srec2bin程序将S-RECORD格式的文件转换成BINARY格式的文件。

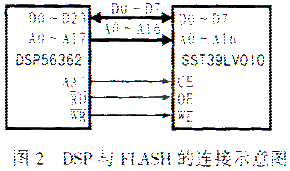

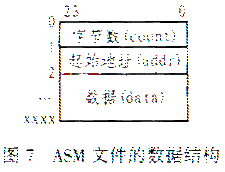

(4)调用Bin2asm程序将BINARY格式的文件转换成asm文件。这个asm文件由一系列的数据定义指令组成,定义的数据依次为系统程序总字节数、系统程序起始地址、系统程序对应的十六进制操作码,其数据结构如图7所示。

为了验证上面方法是否能将引导程序和用户程序的各部分代码成功写入到FLASH中,笔者编写了一个测试程序作为用户程序,该测试程序的功能是将AD输入的音频信号不经任何处理直接输出。实验证明:系统脱机运行时能够正确地运行测试程序,从而说明了系统引导装载和FLASH烧录的成功。

6 结束语

采用双引导装载方式可以克服Bootstrap引导程序不能加载X区数据和Y区数据的缺点,还可以在系统程序运行前将DSP设置为内存切换模式,同时,采用软件编程方法可以在没有专用编程器的条件下,方便、可靠地实现对FLASH的擦除和读写。该方案具有一定的实用性和参考价值,也能够用于其它DSP系统。

(3)调用Srec2bin程序将S-RECORD格式的文件转换成BINARY格式的文件。

(4)调用Bin2asm程序将BINARY格式的文件转换成asm文件。这个asm文件由一系列的数据定义指令组成,定义的数据依次为系统程序总字节数、系统程序起始地址、系统程序对应的十六进制操作码,其数据结构如图7所示。

为了验证上面方法是否能将引导程序和用户程序的各部分代码成功写入到FLASH中,笔者编写了一个测试程序作为用户程序,该测试程序的功能是将AD输入的音频信号不经任何处理直接输出。实验证明:系统脱机运行时能够正确地运行测试程序,从而说明了系统引导装载和FLASH烧录的成功。

6 结束语

采用双引导装载方式可以克服Bootstrap引导程序不能加载X区数据和Y区数据的缺点,还可以在系统程序运行前将DSP设置为内存切换模式,同时,采用软件编程方法可以在没有专用编程器的条件下,方便、可靠地实现对FLASH的擦除和读写。该方案具有一定的实用性和参考价值,也能够用于其它DSP系统。

引用地址:DSP56362的双引导装载方法研究与实现

因为用户代码在一段时间内是相对固定的,所以可以将其固化在非易失性存贮器中。而如果将代码掩膜到DSP内部ROM中去一方面要受到容量以及价格的限制,另一方面,系统代码升级也不是很灵活方便。FLASH是一种高密度、非易失性的电可擦写存储器,其单位存储比特的价格比传统的EPROM要低,十分适合低功耗、小尺寸和高性能的脱机系统。此外,除了可以采用专用的硬件编程器把程序代码烧入FLASH中之外,

因为用户代码在一段时间内是相对固定的,所以可以将其固化在非易失性存贮器中。而如果将代码掩膜到DSP内部ROM中去一方面要受到容量以及价格的限制,另一方面,系统代码升级也不是很灵活方便。FLASH是一种高密度、非易失性的电可擦写存储器,其单位存储比特的价格比传统的EPROM要低,十分适合低功耗、小尺寸和高性能的脱机系统。此外,除了可以采用专用的硬件编程器把程序代码烧入FLASH中之外,

也可以直接利用DSP通过软件编程来实现。本文论述的正是如何通过DSP软件编程来实现对FLASH的读写操作,同时介绍了系统双引导装载方案的实现方法。

2 系统描述

本系统是基于MOTOROLA公司DSP56362芯片构建的数字音效处理系统中的一部分,整个数字音效处理系统的系统框图如图1所示。

DSP56362是一款24位通用定点数字信号处理器。它采用高性能单时钟指令周期的DSP56300内核和Motorola Symphony DSP的音频处理性能相结合的方法来实现具有运算速度快(100MIPS)精度高(24bit),外设接口丰富(具有增强型串行音频接口ESAI、并行主机接口HI08、串行主机接口SHI、数字音频接口DAX等),价格低廉等诸多优点,特别适用于音频处理。其24位的处理精度配合20位的A/D(PCM1800)和24位的D/APCM1744使得整个系统具有很高的动态范围(96dB以上)。它高达100MIPS的运算速度保证了算法处理的实时性。其增强型串行音频接口ESAI可以很方便地与音频A/D、D/A直接通过I2S协议进行连接。通过8bit的并行主机接口HI08可以方便地与负责键盘控制和LED显示的单片机89C51进行通信。

FLASH选用SST公司的39LV010其存储容量为128k%26;#215;8bit,采用3.3V供电,读写周期为70ns,支持块擦除与字节编程,是一款高性价比存储芯片。

DSP与外部FLASH的连接示意图如图2所示。图中,DSP的AA1脚和FLASH的片选信号脚CE相连。

DSP56362的4个地址属性寄存器AAR[3~0]是24位读写寄存器,它们的值可用于控制DSP芯片的AA[3~0]引脚的状态,当某个AAR寄存器中的基址与外部访问指令存取范围相匹配时,由这个AAR定义的相应地址空间(X数据、Y数据或程序)将被相应的AA线选通。在本系统中,正是把DSP的AA1作为FLASH的片选线。AA1脚相应的AAR1寄存器的值设为0xD00811H,当访问地址的高8位为11010000时,外部FLASH被选通。

也可以直接利用DSP通过软件编程来实现。本文论述的正是如何通过DSP软件编程来实现对FLASH的读写操作,同时介绍了系统双引导装载方案的实现方法。

2 系统描述

本系统是基于MOTOROLA公司DSP56362芯片构建的数字音效处理系统中的一部分,整个数字音效处理系统的系统框图如图1所示。

DSP56362是一款24位通用定点数字信号处理器。它采用高性能单时钟指令周期的DSP56300内核和Motorola Symphony DSP的音频处理性能相结合的方法来实现具有运算速度快(100MIPS)精度高(24bit),外设接口丰富(具有增强型串行音频接口ESAI、并行主机接口HI08、串行主机接口SHI、数字音频接口DAX等),价格低廉等诸多优点,特别适用于音频处理。其24位的处理精度配合20位的A/D(PCM1800)和24位的D/APCM1744使得整个系统具有很高的动态范围(96dB以上)。它高达100MIPS的运算速度保证了算法处理的实时性。其增强型串行音频接口ESAI可以很方便地与音频A/D、D/A直接通过I2S协议进行连接。通过8bit的并行主机接口HI08可以方便地与负责键盘控制和LED显示的单片机89C51进行通信。

FLASH选用SST公司的39LV010其存储容量为128k%26;#215;8bit,采用3.3V供电,读写周期为70ns,支持块擦除与字节编程,是一款高性价比存储芯片。

DSP与外部FLASH的连接示意图如图2所示。图中,DSP的AA1脚和FLASH的片选信号脚CE相连。

DSP56362的4个地址属性寄存器AAR[3~0]是24位读写寄存器,它们的值可用于控制DSP芯片的AA[3~0]引脚的状态,当某个AAR寄存器中的基址与外部访问指令存取范围相匹配时,由这个AAR定义的相应地址空间(X数据、Y数据或程序)将被相应的AA线选通。在本系统中,正是把DSP的AA1作为FLASH的片选线。AA1脚相应的AAR1寄存器的值设为0xD00811H,当访问地址的高8位为11010000时,外部FLASH被选通。

通过设置DSP的总线控制寄存器BCR,可以设置访问外部存储器时插入的等待状态的个数。在本系统中,FLASH的存取周期为70ns,为了保证FLASH的正确读写,一般要插入32个等待状态。

3 DSP56362的引导过程

在DSP56362内部的0xFF0000H-0xFF00BFH地址范围内有Motorola定制的24位192字的Bootstrap ROM。该ROM内的Bootstrap引导程序可以通过用户设置的DSP引导模式信号线,将用户程序从外部的8位EPROM、EEPROM、FLASH、 SHI接口或者HDI接口引导到DSP内部的高速RAM中全速运行。

当DSP56362硬件复位后,它将首先采样外部的MODA、MODB、MODC和MODD信号线,并将它们的状态写入工作模式寄存器OMROperating Mode Reg-ister的MA、MB、MC和MD位,然后使程序指针指向0xFF0000H去执行Bootstrap引导程序,Bootstrap引导程序通过对OMR的MA、MB、MC和MD位进行判断来决定选择哪种引导模式。主要的引导模式如表1所列。

表1 DSP56362 Bootstrap的引导模式

MODD

MODC

MODB

MODA

描 述

0

0

0

1

从字节存储器引导

0

0

1

0

跳转到程序ROM起始地址

0

1

0

1

从串行主机接口SHI引导(SPI从模式)

0

1

1

0

从串行主机接口SHI引导(I2C从模式,时钟静止使能)

0

1

1

1

从串行主机接口SHI引导(I2C从模式,时钟静止关闭)

1

0

0

1

内部测试保留

1

1

0

0

从并行主机接口HDI08引导(ISA模式)

1

1

0

1

从并行主机接口HDI08引导(HC11非复用模式)

1

1

1

0

从并行主机接口HDI08引导(8051复用总线模式)

1

1

1

1

从并行主机接口HDI08引导(68302总线模式)

在本系统中,由于程序保存在外部的FLASH里,所以采用的引导模式为第一种即从字节存储器引导。在这种模式下Bootstrap程序将从地址0xD00000H处开始加载外部数据,并采用以下数据格式从外部接口下载用户的系统程序:

(1) 最开始的3个字节用于定义系统程序的总字数(24位)。

通过设置DSP的总线控制寄存器BCR,可以设置访问外部存储器时插入的等待状态的个数。在本系统中,FLASH的存取周期为70ns,为了保证FLASH的正确读写,一般要插入32个等待状态。

3 DSP56362的引导过程

在DSP56362内部的0xFF0000H-0xFF00BFH地址范围内有Motorola定制的24位192字的Bootstrap ROM。该ROM内的Bootstrap引导程序可以通过用户设置的DSP引导模式信号线,将用户程序从外部的8位EPROM、EEPROM、FLASH、 SHI接口或者HDI接口引导到DSP内部的高速RAM中全速运行。

当DSP56362硬件复位后,它将首先采样外部的MODA、MODB、MODC和MODD信号线,并将它们的状态写入工作模式寄存器OMROperating Mode Reg-ister的MA、MB、MC和MD位,然后使程序指针指向0xFF0000H去执行Bootstrap引导程序,Bootstrap引导程序通过对OMR的MA、MB、MC和MD位进行判断来决定选择哪种引导模式。主要的引导模式如表1所列。

表1 DSP56362 Bootstrap的引导模式

MODD

MODC

MODB

MODA

描 述

0

0

0

1

从字节存储器引导

0

0

1

0

跳转到程序ROM起始地址

0

1

0

1

从串行主机接口SHI引导(SPI从模式)

0

1

1

0

从串行主机接口SHI引导(I2C从模式,时钟静止使能)

0

1

1

1

从串行主机接口SHI引导(I2C从模式,时钟静止关闭)

1

0

0

1

内部测试保留

1

1

0

0

从并行主机接口HDI08引导(ISA模式)

1

1

0

1

从并行主机接口HDI08引导(HC11非复用模式)

1

1

1

0

从并行主机接口HDI08引导(8051复用总线模式)

1

1

1

1

从并行主机接口HDI08引导(68302总线模式)

在本系统中,由于程序保存在外部的FLASH里,所以采用的引导模式为第一种即从字节存储器引导。在这种模式下Bootstrap程序将从地址0xD00000H处开始加载外部数据,并采用以下数据格式从外部接口下载用户的系统程序:

(1) 最开始的3个字节用于定义系统程序的总字数(24位)。

(2) 接着的3个字节用于定义系统程序下载到DSP56362程序存储器的目的地址。

(3) 其余是用户的系统程序(每个24位的字由三个字节组成),这些程序将存储在DSP程序存储器内连续的地址空间里。

Bootstrap引导程序要求系统程序在外部FLASH中以地位字节(LSB)在前的顺序排列每个24位字的3个字节。DSP的引导程序一旦完成数据的下载,将马上跳转到内部程序存储器的起始目的地址开始运行用户的系统程序。

4 双引导装载方法

4.1 DSP56362的片内内存分配

DSP56362采用增强型哈佛结构,片内空间可分为程序空间、X数据空间、Y数据空间,每个空间都有一套独立的24位地址总线和数据总线。在缺省情况下,DSP片内的RAM分配情况为:3kB程序RAM、5.5kB X数据RAM和5.5kB Y数据RAM。通过设置内存切换模式(MS=1)可以将2kB的Y数据RAM映射到程序RAM中,此时的片内RAM分配为:5kB程序RAM、5.5kB X数据RAM和3.5kB Y数据RAM。考虑到本系统对程序空间的需求量较大,而数据RAM相对较多,且系统对内部数据RAM的需求并不是很大,因此,将DSP设置成内存切换模式比较好。DSP56362在内存切换模式下(MS=1)的内存映像图如图3所示。

4.2 直接使用Bootstrap引导程序的问题

DSP的内存切换模式需要通过软件指令对OMR寄存器进行设置来实现。由于只有在该指令执行后才能生效,这样就产生了一个矛盾。因为若在系统程序开始时将DSP设置为内存切换模式,那么,往往希望DSP能装载5kB的程序指令,但是,DSP的Bootstrap引导程序是在系统复位后立即执行的,此时DSP处于缺省(MS=0)状态,程序RAM只有3kB,如果此时外部的指令代码的大小超过了这个限制,引导程序就不能把它们加载进去,而当这条设置指令生效时,虽然DSP的程序空间又增加了2kB,但是引导程序已经结束,因而这2kB的程序空间实际上没有被利用。

(2) 接着的3个字节用于定义系统程序下载到DSP56362程序存储器的目的地址。

(3) 其余是用户的系统程序(每个24位的字由三个字节组成),这些程序将存储在DSP程序存储器内连续的地址空间里。

Bootstrap引导程序要求系统程序在外部FLASH中以地位字节(LSB)在前的顺序排列每个24位字的3个字节。DSP的引导程序一旦完成数据的下载,将马上跳转到内部程序存储器的起始目的地址开始运行用户的系统程序。

4 双引导装载方法

4.1 DSP56362的片内内存分配

DSP56362采用增强型哈佛结构,片内空间可分为程序空间、X数据空间、Y数据空间,每个空间都有一套独立的24位地址总线和数据总线。在缺省情况下,DSP片内的RAM分配情况为:3kB程序RAM、5.5kB X数据RAM和5.5kB Y数据RAM。通过设置内存切换模式(MS=1)可以将2kB的Y数据RAM映射到程序RAM中,此时的片内RAM分配为:5kB程序RAM、5.5kB X数据RAM和3.5kB Y数据RAM。考虑到本系统对程序空间的需求量较大,而数据RAM相对较多,且系统对内部数据RAM的需求并不是很大,因此,将DSP设置成内存切换模式比较好。DSP56362在内存切换模式下(MS=1)的内存映像图如图3所示。

4.2 直接使用Bootstrap引导程序的问题

DSP的内存切换模式需要通过软件指令对OMR寄存器进行设置来实现。由于只有在该指令执行后才能生效,这样就产生了一个矛盾。因为若在系统程序开始时将DSP设置为内存切换模式,那么,往往希望DSP能装载5kB的程序指令,但是,DSP的Bootstrap引导程序是在系统复位后立即执行的,此时DSP处于缺省(MS=0)状态,程序RAM只有3kB,如果此时外部的指令代码的大小超过了这个限制,引导程序就不能把它们加载进去,而当这条设置指令生效时,虽然DSP的程序空间又增加了2kB,但是引导程序已经结束,因而这2kB的程序空间实际上没有被利用。

另外,从DSP的Bootstrap程序流程可以看出,这个引导程序只能将系统的程序代码数据加载到DSP内部的程序RAM,而不能将数据加载到DSP内部的X数据RAM、Y数据RAM,这样,那些需要在数据区内定义常数的程序将无法正常运行。

4.3 双引导模式

为了解决以上问题,本文提出了一种双引导模式。具体思路是:在系统程序的开始处,设计一个用户自己的引导模块,用这个模块先对DSP内部的OMR寄存器进行相应的内存切换设置,以使DSP内部的程序RAM扩大为5kB。然后参照DSP的Boot-strap引导程序分别对系统的X、Y及P区的数据进行加载。同时在将程序烧录到FLASH时采用地址隔离的方式将引导模块与系统程序分开存放,引导模块作为一段独立的程序放在首地址为0xD00000H的存储区。于是,对于DSP的Bootstrap引导程序来说,它需要引导的不是整个系统程序,而仅仅是这个引导模块,另外加载完这个模块后就立即跳转到内部程序RAM中执行,此时引导模块已获得CPU控制权,它在完成内存切换后将继续引导系统程序的其他部分。采用这种两次引导的方法,不但使X、Y区的数据可以按照程序的要求进行初始化,而且DSP的程序指令空间可以预先设置成5kB,从而非常巧妙地达到了系统的要求。该双引导模式的引导模块程序流程如图4所示。

5 FALSH的擦除和读写

为了使系统能够脱机运行,应当把系统程序烧录到外部FLASH中去。除了可以用专用的编程器把代码烧入FLASH中外,还可以用软件编程的方法由DSP来实现同样的功能。本系统正是采用这种软件编程的方法实现对FLASH的擦除和读写。

5.1 地址映射

利用DSP擦除和读写FLASH必然会牵涉到FLASH中的地址在DSP中的映射方式。DSP56362的内存映像图已在图3中给出。本系统采用的是128kB的FLASH,其地址范围为:0x000000H~0x1FFFFH。假设FLASH的起始地址0x0000H和DSP的起始地址0x000000H重合,那么FLASH中只有对应于DSP外部空间的那部分地址空间才是DSP可见的。为了使DSP能够访问全部的外部FLASH空间,设计时必须进行地址重映射。

本系统实际用到的FLASH的存储容量不足64kB,也就是说,当访问外部FLASH时,真正起作用的地址线是A0~A15,而高位地址线A23~A16可以为任意值。因此,可以考虑给访问地址加一个偏移量0xD00000H,以将FLASH的地址空间映射到DSP内部X数据RAM中,映射后的地址范围是:0xD00000H~0xD0FFFFH。重映射后的FLASH地址空间落在X数据RAM的外部保留区内,这在DSP中是可见的。

5.2 擦除和读写过程

在DSP将数据写入FLASH之前,先要删除数据所在块,然后才能重新写入。在擦除和写操作之前都要执行相应的命令字序列,即在指定的FLASH地址处写入指定的指令代码,而读操作则可以直接进行。FLASH的擦除和写入流程图分别如图5、图6所示。在本系统中,由于采用了双引导模式,所以首先要将引导程序写入FLASH,然后再分别将用户程序的P区数据、X区数据、Y区数据写入FLASH。

在利用DSP软件编程进行烧录时,可以从目标文件中提取出将要写入FLASH的数据,然后将这些数据打包成一个asm文件,再在烧录程序中将这个asm文件包含进来。接着对烧录程序进行编译、链接,以产生一个目标文件。最后,通过JTAG口将目标文件下载到DSP中运行,这样,DSP就会通过其外部数据线将打包好的asm文件中的数据写入FLASH。在本系统中,引导程序和用户程序将分4次烧入FLASH为此要分别将引导程序、用户程序P区数据、用户程序X区数据、用户程序Y区数据打包成asm文件。打包一个asm文件的具体步骤如下:

(1)调用MOTOROLA公司提供的ASM56300和DSPLNK程序对源文件进行编译、链接,以产生一个cld格式的目标文件。

(2)调用MOTOROLA公司提供的SREC程序将cld格式的目标文件转换成MOTOROLA公司的S-RECORD文件格式,可将目标文件中的P区数据、X区数据、Y区数据提取出来并生成3个文件,其后缀分别为p、x、y。

另外,从DSP的Bootstrap程序流程可以看出,这个引导程序只能将系统的程序代码数据加载到DSP内部的程序RAM,而不能将数据加载到DSP内部的X数据RAM、Y数据RAM,这样,那些需要在数据区内定义常数的程序将无法正常运行。

4.3 双引导模式

为了解决以上问题,本文提出了一种双引导模式。具体思路是:在系统程序的开始处,设计一个用户自己的引导模块,用这个模块先对DSP内部的OMR寄存器进行相应的内存切换设置,以使DSP内部的程序RAM扩大为5kB。然后参照DSP的Boot-strap引导程序分别对系统的X、Y及P区的数据进行加载。同时在将程序烧录到FLASH时采用地址隔离的方式将引导模块与系统程序分开存放,引导模块作为一段独立的程序放在首地址为0xD00000H的存储区。于是,对于DSP的Bootstrap引导程序来说,它需要引导的不是整个系统程序,而仅仅是这个引导模块,另外加载完这个模块后就立即跳转到内部程序RAM中执行,此时引导模块已获得CPU控制权,它在完成内存切换后将继续引导系统程序的其他部分。采用这种两次引导的方法,不但使X、Y区的数据可以按照程序的要求进行初始化,而且DSP的程序指令空间可以预先设置成5kB,从而非常巧妙地达到了系统的要求。该双引导模式的引导模块程序流程如图4所示。

5 FALSH的擦除和读写

为了使系统能够脱机运行,应当把系统程序烧录到外部FLASH中去。除了可以用专用的编程器把代码烧入FLASH中外,还可以用软件编程的方法由DSP来实现同样的功能。本系统正是采用这种软件编程的方法实现对FLASH的擦除和读写。

5.1 地址映射

利用DSP擦除和读写FLASH必然会牵涉到FLASH中的地址在DSP中的映射方式。DSP56362的内存映像图已在图3中给出。本系统采用的是128kB的FLASH,其地址范围为:0x000000H~0x1FFFFH。假设FLASH的起始地址0x0000H和DSP的起始地址0x000000H重合,那么FLASH中只有对应于DSP外部空间的那部分地址空间才是DSP可见的。为了使DSP能够访问全部的外部FLASH空间,设计时必须进行地址重映射。

本系统实际用到的FLASH的存储容量不足64kB,也就是说,当访问外部FLASH时,真正起作用的地址线是A0~A15,而高位地址线A23~A16可以为任意值。因此,可以考虑给访问地址加一个偏移量0xD00000H,以将FLASH的地址空间映射到DSP内部X数据RAM中,映射后的地址范围是:0xD00000H~0xD0FFFFH。重映射后的FLASH地址空间落在X数据RAM的外部保留区内,这在DSP中是可见的。

5.2 擦除和读写过程

在DSP将数据写入FLASH之前,先要删除数据所在块,然后才能重新写入。在擦除和写操作之前都要执行相应的命令字序列,即在指定的FLASH地址处写入指定的指令代码,而读操作则可以直接进行。FLASH的擦除和写入流程图分别如图5、图6所示。在本系统中,由于采用了双引导模式,所以首先要将引导程序写入FLASH,然后再分别将用户程序的P区数据、X区数据、Y区数据写入FLASH。

在利用DSP软件编程进行烧录时,可以从目标文件中提取出将要写入FLASH的数据,然后将这些数据打包成一个asm文件,再在烧录程序中将这个asm文件包含进来。接着对烧录程序进行编译、链接,以产生一个目标文件。最后,通过JTAG口将目标文件下载到DSP中运行,这样,DSP就会通过其外部数据线将打包好的asm文件中的数据写入FLASH。在本系统中,引导程序和用户程序将分4次烧入FLASH为此要分别将引导程序、用户程序P区数据、用户程序X区数据、用户程序Y区数据打包成asm文件。打包一个asm文件的具体步骤如下:

(1)调用MOTOROLA公司提供的ASM56300和DSPLNK程序对源文件进行编译、链接,以产生一个cld格式的目标文件。

(2)调用MOTOROLA公司提供的SREC程序将cld格式的目标文件转换成MOTOROLA公司的S-RECORD文件格式,可将目标文件中的P区数据、X区数据、Y区数据提取出来并生成3个文件,其后缀分别为p、x、y。

(3)调用Srec2bin程序将S-RECORD格式的文件转换成BINARY格式的文件。

(4)调用Bin2asm程序将BINARY格式的文件转换成asm文件。这个asm文件由一系列的数据定义指令组成,定义的数据依次为系统程序总字节数、系统程序起始地址、系统程序对应的十六进制操作码,其数据结构如图7所示。

为了验证上面方法是否能将引导程序和用户程序的各部分代码成功写入到FLASH中,笔者编写了一个测试程序作为用户程序,该测试程序的功能是将AD输入的音频信号不经任何处理直接输出。实验证明:系统脱机运行时能够正确地运行测试程序,从而说明了系统引导装载和FLASH烧录的成功。

6 结束语

采用双引导装载方式可以克服Bootstrap引导程序不能加载X区数据和Y区数据的缺点,还可以在系统程序运行前将DSP设置为内存切换模式,同时,采用软件编程方法可以在没有专用编程器的条件下,方便、可靠地实现对FLASH的擦除和读写。该方案具有一定的实用性和参考价值,也能够用于其它DSP系统。

(3)调用Srec2bin程序将S-RECORD格式的文件转换成BINARY格式的文件。

(4)调用Bin2asm程序将BINARY格式的文件转换成asm文件。这个asm文件由一系列的数据定义指令组成,定义的数据依次为系统程序总字节数、系统程序起始地址、系统程序对应的十六进制操作码,其数据结构如图7所示。

为了验证上面方法是否能将引导程序和用户程序的各部分代码成功写入到FLASH中,笔者编写了一个测试程序作为用户程序,该测试程序的功能是将AD输入的音频信号不经任何处理直接输出。实验证明:系统脱机运行时能够正确地运行测试程序,从而说明了系统引导装载和FLASH烧录的成功。

6 结束语

采用双引导装载方式可以克服Bootstrap引导程序不能加载X区数据和Y区数据的缺点,还可以在系统程序运行前将DSP设置为内存切换模式,同时,采用软件编程方法可以在没有专用编程器的条件下,方便、可靠地实现对FLASH的擦除和读写。该方案具有一定的实用性和参考价值,也能够用于其它DSP系统。

上一篇:ADSP TigerSHARC中利用查找表快速计算三角函数

下一篇:基于DSP的纸币号码识别系统

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新嵌入式文章

更多精选电路图

更多热门文章

更多每日新闻

- 本田严厉警告日产:若与鸿海合作,那么本田与日产的合作将终止

- Microchip推出新款交钥匙电容式触摸控制器产品 MTCH2120

- Matter对AIoT的意义:连接AIoT设备开发人员指南

- 我国科学家建立生成式模型为医学AI训练提供技术支持

- Diodes 推出符合车用标准的电流分流监测器,通过高精度电压感测快速检测系统故障

- Power Integrations面向800V汽车应用推出新型宽爬电距离开关IC

- 打破台积电垄断!联电夺下高通先进封装订单

- Ampere 年度展望:2025年重塑IT格局的四大关键趋势

- 存储巨头铠侠正式挂牌上市:首日股价上涨超10%

- Vishay 推出新款精密薄膜MELF电阻,可减少系统元器件数量,节省空间,简化设计并降低成本

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 OPA2682U

OPA2682U

京公网安备 11010802033920号

京公网安备 11010802033920号