1、引言

阿尔法磁谱仪(Alpha Magnetic Spectrometer,AMS)实验室是丁肇中博士领导的由美、俄、德、法、中等16个国家和地区共300多名科学家参加的大型国际合作项目。它是国际空间站上唯一大型物理实验,是人类第一次在太空中精密地测量高能量带电原子核粒子的实验。其目的是为寻找反物质所组成的宇宙和暗物质的来源以及测量宇宙线的来源。

但是对于AMS实验的空间电子系统,同样会受到高能粒子的袭击,导致存储器的内容发生变化,改写半导体存储器件的逻辑状态,导致存储单元在逻辑‘0’与‘1’之间发生翻转,使存储的关键数据出错,控制程序跑飞等。这对于AMS实验系统来说,是一个不容忽视的问题。因此,我们采用二元BCH(31,16)码,能纠正三位随机错误,这种纠错码信息不需要储存,不需要反馈,实时性好。

2、编译码原理

对于空间电子系统可能出现的问题,我们进行检错与纠错,其基本思想是在信息码组中以一定规则加入不同方式的冗余码,以便在信息读出的时候依靠多余的监督码或校验码来发现或自动纠正错误。

2.1 编码

编码比较简单,二元BCH(31,16)是GF(25)域上的线性分组码,其中二进制最高位m=5,总信息长n=2m-1=31,校验位数k=15,可纠错位数t=3,生成多项式g(x)为:

2.2 译码

译码过程比较复杂,包括1)求伴随多项式,2)系数计算电路,3)错误位置计算电路,其中最关键的是第三步,如图1。这里假设接收到的数据错了三位,第28、20、17位发生了0/1偏转,即

(1)求伴随多项式

根据生成多项式与ai的最小多项式之间的关系,用φi(x)去除接收多项式R(x)而得到伴随式分量,即,

(2)系数计算电路

令错误位置多项式

[page]

[page]

(3)错误位置计算

由上一步我们得出错误图样为:

因此原码多项式为:

3、仿真与下载

对于上述编译码算法,采用Verilog HDL可综合语言来描述,整个程序分为顶层模块和底层模块,顶层模块很简单,主要完成底层模块的调用和数据的复位,编码算法主要由底层模块完成。其中包括编译码算法主程序,拨码开关控制程序,液晶显示程序,系统函数PLL(锁相环)程序。系统利用两个拨码开关sw1,sw2来控制编码结果或译码结果的下载与显示。

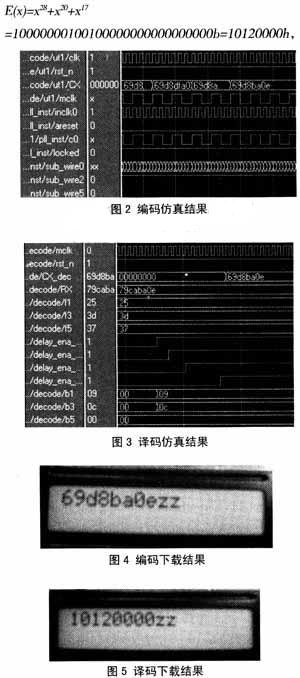

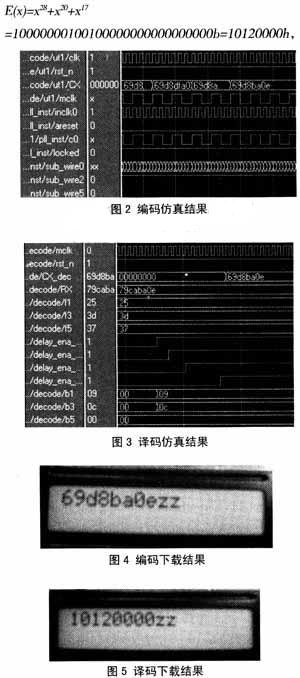

图2和图3是编码和译码的仿真图,仿真工具用的是modelsim 6.0,编码结果CX=0x69d8ba0e,译码过程中,根据接收多项式RX=0x79caba0e以及最小多项式f1=0x25,f3=0x3d,f5=0x37,译码后得出错误多项式EX=0x10120000,最后RX与EX相与得出CX_dec=0x69d8ba0e,与原码一致。图4和图5是下载后显示到液晶屏的结果CX=0x69d8ba0e,EX=0x10120000,所用编译工具是quartusⅡ5.0,FPGA芯片采用的是Altera Cyclone EP1C6,用到1个PLL,引脚数15个,芯片资源耗用不超过5万门。

4、结束语

BcH(31,16)编译码算法,可以纠正3位错误,用VerilogHDL可综合语言描述以上的编码纠错过程,软件仿真和硬件下载都证明了算法的正确性和可行性。整套试验系统是模拟空间存储器受到高能粒子的干扰而发生错误,这对于我们AMS实验也是很关键的一步,现阶段我们用到的防护措施是三倍冗余编码纠错,但它占用的硬件资源比较多,而本文中所研究的循环BCH码能够节省资源,纠错效果也很明显,所以它将会在AMS项目中得到实际的应用。

关键字:FPGA 空间存储器 纠错

引用地址:

基于FPGA的空间存储器纠错系统的设计研究

推荐阅读最新更新时间:2024-05-02 20:57

赛灵思 FPGA 应用于亚马逊 EC2 F1 Instance

赛灵思(Xilinx)近日宣布其高效能 Xilinx Virtex UltraScale+系列 FPGA,现已应用在 Amazon Elastic Compute Cloud (Amazon EC2) F1 Instance 实例。 除了利用 FPGA 提供可编程的硬件加速机制外,还让用户能优化他们的运算资源来满足 其作业负载的特殊需求。 当亚马逊云端网络服务,在云端上提供安全且可调整的运算规模时,F1 实例, 让用户透过使用 FPGA 对关键作业负载,能轻易地部署硬件加速机制。 由于 FPGA 具备可编程能力,用户不须重新设计任何硬件,即可拥有充分的弹性来升级与最 佳化其硬件加速功能,进而缩短评测与开发的时间。 F1 实例将用来

[半导体设计/制造]

设计工程师五步实现FlexRay稳健网络拓朴

FlexRay已开始在单通道高速动力传动、驾驶辅助和提高舒适程度的汽车电子应用中大展身手。在新款BMW X5汽车中,FlexRay用于悬架控制之中,这样就可以在利用双通信信道和总线监控把这种具有容错功能的确定性协议运用在安全驾驶功能中之前,让工程师和开发人员有一个逐渐适应的学习过程,降低了相关风险。

在FlexRay应用的开发过程中,设计工程师可以通过五个基本步骤来构建一个稳健的网络拓朴。

步骤1:首先必须定义车辆底盘上节点的数量及其假定位置,然后才能确定实现无stub(一种被称为“菊花链”的拓朴结构)无源总线所需的线缆长度,该总线终端即是线缆终端处,如图1所示。如果线缆长度小于10米,则拓朴完成,其被认为可用于系列生产。

[嵌入式]

基于FPGA的电容在线测试系统设计

PCB在焊接完成后,需要对其元器件进行测试,传统的方法是将其焊离PCB板后测试,但该方法不仅麻烦、效率低,并且容易损伤电路板而极不实用;另一方法就是人工结合机器进行测试,但这需要测试人员有一定的经验,也给测试带来了一定的不确定性,使得测试结果的精准度无法达到现代电路板的可靠性要求。所以,本文研究了一种可行的、简单实用及高精度的电容在线测试电路。另外,随着EDA技术的快速发展,FPGA以其高集成度、高可靠性及灵活性等特点正在快速成为数字系统开发平台,在多种领域都有非常广阔的应用前景。本设计结合上述两特点,设计了一种基于向FPGA内植入Nios II嵌入式软核作为控制器的电容在线测试电路。 1.测试原理 在线测试的基本思想是应用电气隔

[电源管理]

基于FPGA的误码测试仪

摘 要: 本文提出了一种基于 FPGA 的误码测试方案,并在 FPGA 上实现了其功能。该方案不仅纳入了“同步保护”的思想,同时对误码率量级的判断也提出了一种简化而又可行的方法。 在数字通信系统中,为了检测系统的性能,通常使用误码分析仪对其误码性能进行测量。误码分析仪给工程实际应用带来了极大的便利,比如它有丰富的测试接口和测试内容,并能将结果直观、准确的显示出来。但是它的价格昂贵,并且通常需要另加外部辅助长线驱动电路才能与某些系统接口适配。这些都严重的制约了通用误码仪在实际中的应用。 基于工程的需要和实际应用中的困难性,本文提出一个基于 FPGA 的多功能误码测试方案。芯片采用

[模拟电子]

英特尔FPGA 支持阿里云的加速即服务

今天,英特尔®宣布英特尔现场可编程门阵列 (FPGA) 为阿里巴巴集团的云计算部门—阿里云的加速即服务(Acceleration-as-a-Service)提供支持。加速服务可通过阿里云网站提供,支持客户在云中开发与部署加速器解决方案,以便应用到人工智能推理、视频流分析、数据库加速和需要密集型计算的其他领域。 英特尔 FPGA 支持的加速即服务也被称作阿里云 F1 实例,支持用户通过即购即用的模式获得云加速服务,从而节省前期的硬件投资。 “对于运行业务应用和苛刻的数据和科学工作负载的客户而言,他们可以借助英特尔FPGA 以更经济高效的方式加速提升基于云的应用性能。”阿里云副总裁李津表示。“FPGA 的另一项关键价值在于它能

[嵌入式]

基于嵌入式Linux和FPGA的千兆网数据传输的实现

引言

中国散裂中子源实验的简图如图1所示,其原理是把中子束打在被测样品(例如新药品或机翼材料)上,探测被反射的中子位置就能计算出样品的内部结构图像,其特点如下: A/D采集通道多,每个通道的数据带宽高,且需要把现场采集的数据传到远程服务器上。因此,要求数据传输模块既要成本低、微型化、具备网络功能,也要数据带宽高。

图1 中国散裂中子源实验简图

单片机或ARM具有微型化、低成本的特点,但数据带宽和灵活性不满足本项目;工控计算机数据处理能力强,有网络接口,但是体积过大,成本高;传统高能物理实验采用的VME系统也因体积大、数据带宽有限而不适合用在中国散裂中子源实验上。

FPGA有很高的性能,而且内部还

[嵌入式]

EL7564C的双电压FPGA电源解决方案

概述 Xilinx公司的FPGA(现场可编程门阵列)芯片正向高密度化发展,FPGA的内核在提供低成本和高性能的同时还林求低功耗。当今选进的亚微米IC工艺正趋于采用低电压供电,同时这将导致对大电流的不断需求。工程线路板的设计必需满足这类电源供电的需要。 现在FPGA的内核和I/O的电源需要双电源供电。通常来说,I/O部分的供电电压是由设备中其它元器件所决定的,而FPGA的内核则依赖于产品本身的设计,其内核的供电电源分别为2.5V,1.8V或1.5V。电源的跟踪(Tracking)/顺序(Sequencing)的功能可以用来满足这一系列的电压要求。 Elantec公司的Monopower系统DC/DC转换器提供了一套理想的

[电源管理]

在莱迪思FPGA中实现DC-SCM

在莱迪思FPGA中实现DC-SCM 莱迪思半导体白皮书 2022年4月 目录 第一节 摘要 第二节 DC-SCM是什么? 第三节 为什么要使用DC-SCM? 第四节 DC-SCM架构 第五节 DC-SCM LTPI 第六节 莱迪思LTPI 第七节 莱迪思DC-SCM的安全实现 第八节 莱迪思DC-SCM的控制实现 第九节 莱迪思产品革新:一种方案三种关键特性 第十节 支持DC-SCM的莱迪思产品 第十一节 使用莱迪思SupplyGuard™实现端到端的保护 第十二节 结论 第十三节 参考文献 摘要 DC-SCM是OCP硬件管理项目的一个子项目。DC-SCM实施模块化服务器管

[嵌入式]

[page]

[page]

![]()

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页

京公网安备 11010802033920号

京公网安备 11010802033920号