摘要:基于DDS和VHDL硬件描述技术,采用大规模可编程门阵列FPGA,实现了FSK和PSK数字调制。介绍了m伪随机基带码元发生器、跳变检测器和DDS信号发生等模块。系统参数易修改、可移植性强、性能稳定。

关键词:FSK/PSK;DDS;m伪随机序列;FPGA

在通信领域,经常需要将基带信号进行某种调制,使其适合于信道传输。FSK、PSK即为常用的两种数字调制方式。传统模拟调制系统中大量采用分立元件,体积较大,电路复杂。由于模拟元件自身参数的离散性和受环境温度、湿度等因素影响,导致系统稳定性较差。本文提出了一种基于DDS技术的FSK/PSK调制的数字实现方法,提高了系统的稳定性,克服了模拟调制的弊端。

1 FSK/PSK调制原理

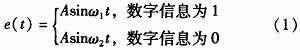

频移键控(Frequency Shift Keying,FSK),是利用载波的频率参量来携带数字信息的调制方式。常用的是二进制频率键控信号,即2FSK,用载频w1表示数字信息“1”,用载频w2表示数字信息“0”,而w1和w2之间的变化是瞬间完成的。

相移键控(Phase Shift Keying,PSK),它是受键控的载波相位按数字基带脉冲的规律而改变的一种数字调制方式。这种以载波的不同相位直接表示相应数字信息的相位键控,通常被称为绝对移相方式。当基带信号为二进制数字脉冲序列时,所得到的相位键控信号为二进制相位键控,即2PSK,它的表达式为

![]()

式中,φ(t)由数字信息“0”“1”控制。在绝对移相中,因为φ(t)选用的参考相位基准就是未调制的载波,所以φ(t)就是载波的绝对值。一般说来,数字信息为“1”时,φ(t)=0,数字信息为“0”时,φ(t)=π。即

![]()

FSK、PSK的调制示意图如图1所示。

2 FSK/PSK调制逻辑设计与仿真

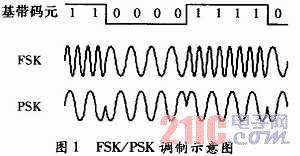

FSK/PSK调制逻辑共分为3个部分:分频器、m序列产生器和FSK/PSK调制器。分频器用于产生FSK/PSK调制器和m序列的基准时钟信号f1,f2和f3,m伪随机序列器产生基带码元。FSK/PSK调制器根据输入的基带码元和基准时钟产生相应的FSK或PSK信号,调制模式由mode模式选择。当mode为低电平时,表示选择FSK调制,当mode为高电平时,表示选择PSK调制。FSK/PSK调制器输出的数字调制信号经DAC转换成模拟信号输出。逻辑模块框图,如图2所示。

2.1 分频器

分频器对频率为f0的时钟输入信号clk分别以分频系数D1,D2和D3产生FSK/PSK调制器和m序列的基准时钟信号f1,f2和f3。其关系如式(1)所示。

![]()

f1和f2决定了FSK调制信号的两个载波频率,f2决定了PSK调制信号的载波频率,f3决定了基带码元速率。为了保证每个基带码元的宽度T是载波周期的整数倍,在选择分频系数时应满足式(2)。

![]()

式中,M为D1和D2的最小公倍数。

2.2 m序列产生器

m序列是由多级移位寄存器或其他延迟元件通过线性反馈产生的最长的码序列。m序列的最大长度取决于移位寄存器的级数,而码的结构取决于反馈抽头的位置和数量。其特点是:随机特性、预先可确定性、循环特性。

本设计利用带有两个反馈抽头的3级反馈移位寄存器得到一串7位循环序列“1110010”,并采取措施防止进入全“0”状态。通过更换时钟频率,可以方便地改变输入码元的速率。这一系列的循环序列码作为基带信号码元。其电路结构如图3所示。

2.3 FSK/PSK调制器

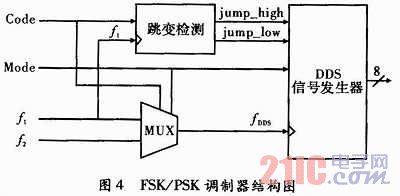

FSK/PSK调制器由时钟选择模块、跳变检测模块和DDS信号发生模块3部分组成。原理如图4所示。

[page]

2.3.1 时钟选择模块

载波频率选择模块的两个输入端分别接时钟信号f1和f2,其输出信号fDDS作为DDS信号发生模块基准时钟信号。该模块的输出真值表,如表1所示。

2.3.2 跳变检测模块

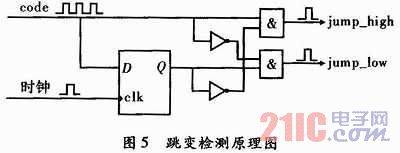

跳变检测模块用于检测基带码元的变化情况。当基带码元上升或下降沿到来时,其对应的输出端产生与时钟周期等宽的高脉冲信号jump_high或jump_low。该信号提供给下一级DDS的相位累加器,来控制累加器的相位偏移。跳变检测原理图如图5所示。

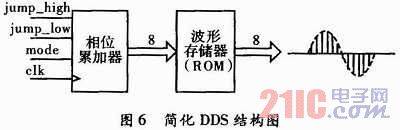

2.3.3 DDS信号发生模块

DDS是一种应用数字技术产生信号波形的方法。由于模块中只需产生两种频率和相位的波形,因此对DDS的设计中省略了频率控制字和相位控制字等部分。频率改变通过时钟选择模块选择不同的基准时钟来实现。简化后的DDS主要由相位累加器和波形ROM组成,如图6所示。

相位累加器在频率为fc的时钟信号clk控制下,以步长K作累加,输出的N位二进制作为波形存储器ROM的地址,以该地址对ROM进行寻址。则DDS输出波形的频率f0的表达式,如式(3)所示

![]()

本设计中,取K=1,N=8,波形存储深度为100个采样点,则可得f0=fc/100。jump_high、jump_low、mode和clk通过控制相位累加器的输出来实现:FSK/PSK波形合成输出。当mode为低电平时,即FSK调制模式时,jump_high和jump_low中任一信号出现高脉冲时,累加器清零,然后根据clk进行循环累加。当mode为高电平时,即PSK调制模式时,累加器的工作方式如表2所示。

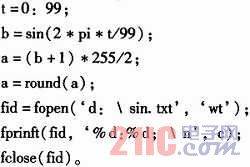

ROM表是对选取的采样点进行量化、编码,通过相位累加器的地址值查找ROM表中的内容,以得到可合成正弦波的正弦点的值。其原理是:在横轴上取100个采样点,将纵轴的正弦值[-1,+1]总体提升一个单位,即将正弦值的取值区间变为[0,2],并将其均匀地分成255个量化区间,再对这255个量化间隔在00000000~11111111进行编码,即将所取的采样点的幅度值对应到各个量化间隔。

具体实现方法,可通过用Matlab产生一个mif文件。Matlab源程序如下:

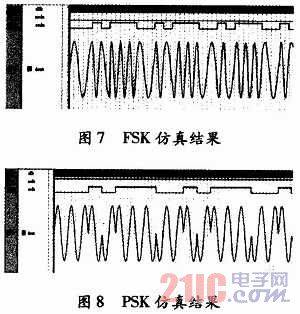

3 系统仿真结果

Altera公司的QuanusⅡ集合了综合和仿真的功能。本设计在Quartus II中完成了VHDL的代码编写和综合布线,并对整个设计系统进行了时序仿真,仿真结果如图7~图8所示。其中,clk为外接输入100 MHz时钟;mode为模式控制键;code为由m序列产生的伪随机码,用做基带码元;dout为输出的调制结果。

图7中,mode的值为“0”,说明是FSK调制方式。从图中可以看出,当基带码元code为“0”时,dout输出低频调制波。当基带码元code为“1”时,dout输出高频调制波。实现了用不同的频率变化传递数字信息,完成了FSK调制。

图8中,mode的值为“1”,说明是PSK调制方式。从图中可以看出,dout的输出波形频率是单一的,当基带码元由“1”向“0”跳变时,波形出现倒π现象,实现了通过相位变化传递信息,完成了PSK调制。

4 结束语

介绍了一种基于DDS技术的FSK/PSK调制方式的FPGA实现方法。整个系统采用VHDL硬件描述语言进行软件编写,参数修改方便,并具有较强的可移植性。其原理简单,易于实现。相比传统模拟调制方式,这种数字调制方式具有较好的稳定性和抗干扰能力,在通信领域中具有较强的实用性。

上一篇:基于麦克风阵列声源定位系统的FPGA实现

下一篇:DSP和FPGA在图像传输系统中的应用和实现

推荐阅读最新更新时间:2024-05-02 21:24

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号