对于自主机器人导航和其它机器视觉应用来说,实时深度感知是很关键的。目前通过立体图像来计算深度的算法计算量很大,例如差异测绘,要占用CPU大量的时间,或者需要用昂贵的器件进行实时操作。

针对立体摄像的深度感知,FPGA解决方案能使处理器的时间得到缓解,减少或除去器件的成本,例如MPU、DSP、激光器和昂贵的镜头。通过提供给机器人其环境中的差异测绘,FPGA使机器人中的CPU专注于重要的高层任务,例如建图和定位。

差异测绘

加深度感知到机器人的常用技术是用两个水平放置的独立摄像机,互相之间平行分开放置。用差异测绘算法对两个摄像机进行比较,见图1。

图1 差异测绘计算

简单来说,差异是指右面和左面图像之间的差别。物体越接近摄像机,两个图像之间的差异越大。

你可以自己来做一个实验,对着你的脸水平地向上握住一支笔,不停地眨你的左眼和右眼。移动的笔越接近你的脸,你眨眼时觉得移动越多。做更多的移动时,物体越接近你的眼睛,图像中的差异越大。

如图1所示,从两个图像之间物体的位置算出差异:d=x1-x2。为了计算点M的实际坐标,可通过左面和右面的摄像机来进行计算:

X=Bx1/d

Y=By1/d

Z=fB/d

相关的问题

计算差异测绘依赖于相关的图像,以及左面图像和右面图像的匹配性质。逐点计算相关的像素的计算量是很大的,因此用其它算法来简化这个问题。有一种方法称为图像点相关,仔细检查左面图像的像素块,称为点,然后在右面图像中寻找相同的点。其它的方法包括边沿检测和匹配。一旦定位了相应的图像,就可进行差异计算。

失真与曝光问题

如果使用高质量的摄像机,可以忽略镜头失真。为了省钱,使用便宜的CMOS 或者CCD摄像机,或者低成本广角镜头。这些较低质量的产品会引入失真或曝光问题。

镜头会引起比例和定位失真,例如白点效应,靠近图像外面的物体出现弯曲状,使用众所周知的图像处理算法可以进行补偿。针对移动或者其它几何算法,纠正白点的一种方法是使用坐标的查找表重测图像中的像素。

在非常明亮和非常暗的环境中,其它的算法需要可靠地捕获图像中的详细特征。例如,针对不同的区域确定最佳的曝光设置,使用区域的合成图像可以补偿缺少背景亮度。

用含有嵌入式DSP的FPGA的解决方案

本文中阐述的深度感知算法计算复杂,以实时的视频速率来实现。系统设计者必须评估CPU/软件、ASIC, ASSP(例如DSP处理器)和FPGA解决方案,确定哪个是最佳的,以及FPGA价格。

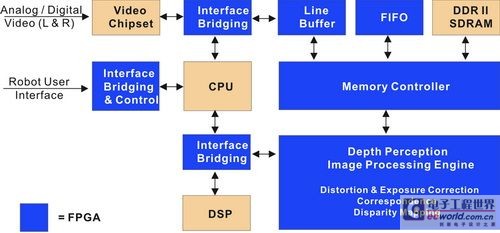

图2展示了提出的FPGA协处理器解决方案,解决失真、曝光、通信和针对深度感知差异测绘算法。这个方法使CPU腾出时间,允许DSP处理器处理更多的串行任务。

图2 FPGA支持计算量大的差异测绘算法

通常选择FPGA时,需要评估三个电路方面的需求:

●针对利用并行特性的协处理功能,DSP的功能和性能。

●DDR(双数据速率)和LVDS(低电压差分信号)支持接口至片外SDRAM缓冲存储器,直接连接到来自摄像机的图像数据。

●安全方案以保护知识产权。

对于图像处理算法,传统的DSP处理器的并行功能有限,每个DSP芯片只有1到4个乘法器,见图3中的左面。因此DSP用很高的时钟速率来进行补偿,时钟速率高达1GHz或更高,以达到高的吞吐量。需要很快完成的复杂串行任务的DSP算法应该用DSP处理器实现。

然而,许多深度感知图像处理功能需要大量的并行处理,例如线性插值技术,媒体滤波器和几何估计。与DSP芯片比较,FPGA可以用并行来执行串行功能,以加速系统性能,见图3的右面所示。例如图像对应是很简单的算法,比较大量的像素值,或者两个图像之间的像素点。为了得到有效均方差的和(SSD),图像对应算法必须对图像中的像素进行百万次计算,对串行执行功能的DSP芯片来说这是一个挑战性的任务。

具有DSP功能的FPGA包含几个乘法器块,但是一些FPGA还有嵌入式加法器、减法器和大大增加处理性能的累加器。尽管低成本FPGA以低于300MHz系统时钟频率工作,但用片内多个DSP块以并行方式实现多个DSP功能可以达到高的DSP吞吐量(3,000 MMAC)。

存储器和DDR

由于有多个乘法器,利用FPGA并行的灵活性有益于存储器的访问。能够容易地并行访问各种存储器。片内分布式存储器可以用来建立小的高性能便笺,针对去除白点使用坐标的查找表,对于在图像中再测绘像素是很有用的。片内较大的嵌入式存储器块能构建较大的高性能存储器,用于FIFO和线缓冲器。

片外存储器DDR II SDRAM可以提供大的高性能存储器。针对常用于图像处理,存储整个帧的DDR SDRAM,FPGA可以为DDR SDRAM提供存储器控制和接口。

较低的时钟速度(100MHz以下),DDR存储器控制器接口是容易做的,可用FPGA中的通用I/O和逻辑实现。然而在较高的频率,拥有专门电路的FPGA要求稳健的DDR存储器接口。不是所有FPGA器件都有这些专门电路的,实现高速DDR存储器接口的成本和复杂性差别很大,取决于特殊的FPGA。

LVDS

针对摄像机和通过LVDS接口的视频芯片集的深度感知,例如摄像机链接, FPGA接口图像处理引擎。LVDS是低噪声、低功耗,小摆幅差分信号用于通过铜线传送高速(每秒吉比特)数据。

作为一个用于视频接口的例子是7:1 LVDS接口,有多个LVDS信号对用于数据传送,一个信号对用于时钟。对一些FPGA来说,这是本身的I/O接口。视频数据通过3个LVDS对进入FPGA,I/O结构对这个包进行解串,然后把FPGA中并行的数据送到逻辑阵列。

安全性

因为自主的机器人有时用于军事应用,在配置期间FPGA不应对系统引入额外的脆弱性。对于基于SRAM的FPGA,配置数据来自外部的非易失存储器。有些FPGA拥有内置的128位AES解密引擎,防止黑客通过逆向工程来获取FPGA中的功能。

只要密钥是未知的,AES配置位流加密提供了保护措施。然而,非易失FPGA完全去除了这种安全性的风险。一些非易失FPGA在同一芯片上组合了Flash和SRAM。上电后SRAM获得工作配置。这种技术提供了高配置安全性,同时又利用了SRAM无限次重构的优点。

结语

支持DSP、差分信号LVDS和DDR II存储器接口的FPGA使得机器人的实时感知成为可能。

对于机器人的立体视觉应用,针对实时图像处理实现,CPU、DSP处理器和FPGA协处理器的组合能够对性能和价格做出最佳的平衡。FPGA能够处理高度并行差异测绘和深度感知算法。DSP进行较少并行处理、高速和简单代码的更加复杂的功能。CPU做需要灵活性和高层软件实行的那些部分。

基于Flash,非易失LatticeXP2 FPGA支持许多需求,包括LVDS、内置DDRII存储器和完整特性的DSP块,以及大量的可编程逻辑和存储器块支持接口和其它的定制功能。许多DSP知识产权核和MATLAB SIMULINK使设计更加便利。Lattice还有基于7:1 LVDS视频接口的参考设计和平台。免费参考设计IP提供的一些功能是色深度转换、亮度、对比度和视频覆盖。

- EE牵手TI上传有礼、积分双倍

- 有奖直播:赋能移动电源,贝能推出1800W全数字双向电源方案

- 跟着电源达人一起动手做“高效率双向DC-DC变换器”

- TI 嵌入式处理主题直播月|报名观看直播赢好礼【低功耗WiFi MCU、Sitara AM57X平台、机器学习】

- ADI & 世健 新基建系列第三期——5G 仪器仪表和测试 答题赢好礼!

- 下资料赢京东卡|泰克“软硬”兼施 打造超值示波器

- Nexperia有奖直播|电动汽车中车规功率MOSFET和氮化镓器件的介绍及应用

- 拆招有礼:洞悉电子产品中的大数据,招招解决测量难题!Keysight DAQ970系列活动

- 邀你参加DIY,大家一起“搞事情”!

- 学视频,晒WEBENCH® 设计方案,免费获得TI样片!

深度学习核心技术与实践 (猿辅导研究团队)

深度学习核心技术与实践 (猿辅导研究团队) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号