台湾工业技术研究院提出一种能够显著提升客制化FPGA原型板验证效率的创新方法,自动化现有的电路仿真(in-circuit emulation)侦错功能,并提供更高的FPGA能见度。这个以FPGA为基础的SoC验证平台对工研院而言是前景看好的崭新领域。

案例研究:高效能的多媒体SoC平台

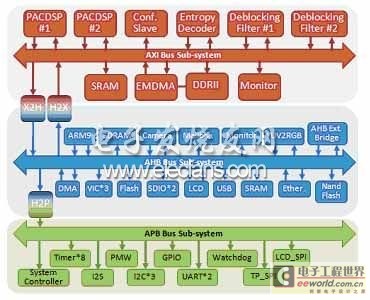

这款SoC设计是高效能的Android兼容多媒体SoC平台。配置了AXI、AHB与APB总线,供通讯使用;由工研院(PACDSPs、EMDMA 与 DDR2控制器)设计的高效能客制化IP组件连结至AXI 总线,加速H.264视讯编译码器(video codec)等多媒体应用软件的执行。包括ARM、SDRAM、DMA、SRAM、Ethernet与LCD在内的标准IP组件连结至AHB总线,适合于一般应用。最后,UART、Timer、I2S、I2C与Watchdog等低频率的IP区块(block)则连结至APB总线。

下列案例研究说明了工研院与思源科技工程师如何合作,使用思源科技ProtoLink Probe Visualizer,克服工研院SoC设计中出现的验证挑战。这个与音效功能相关的问题是:在 FPGA原型板未激活OS的状况下,功能正常运作 (可录音与播放);但如果在原型板上启用Linux,功能就无法正常运作。在FPGA原型环境中,要使用传统的侦错方法排除这类问题是相当困难的。FPGA的能见度仅局限在少数的讯号与时脉周期内,无法提供足够的信息找出错误所在。而因为激活OS(例如 Linux)耗费的时间相当长,想透过缓存器转换阶层(RTL) 仿真来解决问题也行不通。由于问题的成因可能在于软件、硬件或驱动程序,因此要确实找出问题的根本原因是一项考验。

与众不同的作法

要简化侦错作业,就需要更高效率的验证方法。ProtoLink Probe Visualizer是新的原型验证环境,采用以软件为基础的方法,可以从RTL设计阶段开始到最终的设计实现阶段,都提供高水平的设计能见度,可全面加速侦错作业的进行。

工研院起初担心其客制化原型板可能无法符合思源科技ProtoLink Probe Visualizer的接口需求,而思源科技工程师在进行几项快速测试之后,证明工研院客制化原型板上的标准 J连接器可顺利地与执行Probe Visualizer软件的工作站连结。只需在原型板上新增锁相回路(PLL),提供所需的取样时脉(sampling clock)即可。FPGA的设置流程相当简单,可轻松整合至现有的程序(script) 中,自动选取大约100个探测讯号(probed signal),就能见度来说,已比过去的方法提升6倍之多。此外,所有的探测资料都可储存在外接的2GB探测讯号内存中而不占用FPGA资源,真正额外需要的探测逻辑(probe logic)也仅占用FPGA的2%,可说相当的少。外接内存的资料容量可储存充足长度的时脉周期,让工程师能够确实掌握软件、硬件与驱动程序间的关系。

工研院团队透过思源科技Verdi自动侦错系统的进阶观察、追踪与分析功能,来使用储存的探测资料进行侦错作业。在经过多次重复侦错之后,发现了两个问题:1) USB中断 (USB interrupt)长时间锁住ARM,因此I2S内的FIFO是空的,因而造成问题; 2)定时中断(Timer interrupt)的优先级高于DMA中断,因此再一次造成I2S内的FIFO是空的。工研院工程师使用思源科技软件的侦错功能,进一步分析设计行为,仅管表现出来是共通的错误征兆,工程师还是能够迅速发现这些错误的根本成因是源于两种不同的情况。

此外,观察额外的关键讯号是侦错时必需的,但这些讯号多半不在原始探测清单中。工研院工程师透过Probe Visualizer迅速的探测ECO流程,在10分钟内就可新增10个新讯号,而且不用重新编译整个设计。相对传统的侦错方法需要在RTL拖曳新讯号,并且针对这个特定的设计重新执行合成(synthesis )以及布局与绕线作业,约需花上2至3个小时,因此这方面的革新省下了大量的时间。

工程师能够轻松地将所需额外的RTL探测讯号由Verdi侦错环境拖曳至ProbeVisualizer。这套系统会自动建立RTL至逻辑闸层(RTL-to-gate level)的讯号对应关系,所以可直接在 FPGA 布局与绕线档案上迅速执行部份绕线作业来看到新增的探测讯号,大幅缩短侦错作业时间,所以能在短时间内处理多重侦错工作阶段 (debug session)。而对设计中使用的“黑盒子”IP区块,也只需EDIF名称,就可以进行探测ECO流程。

评估结果

工研院工程师在修正问题并成功试产设计之后,检讨了项目实际耗费的时间,并评估了这个新的FPGA SoC原型验证方法的成果。

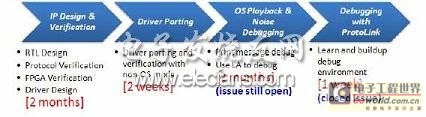

进行RTL设计、仿真、通讯协议验证与FPGA设计实现的时间约为2个月。在驱动程序移植(driver porting )上所花费的时间则短了许多,大约只有2个星期。工程师随后又花了2个月的时间进行验证作业,试图透过硬件逻辑分析器检查 FPGA 内部讯号解决音效问题,同时也在音效驱动程序中增加观察点,以连结并企图找出问题。这种传统的FPGA侦错方法,需要的时间和设计研发的时间一样长,然而对工研院团队而言,相当令人沮丧的是结果仍然一无所获。不过,在经过思源科技提供的应用软件教育训练/支持课程及一星期的实作经验后,工研院工程师使用ProtoLink Probe Visualizer,在短短一星期的时间内就厘清了两大问题!

对工研院而言,ProtoLink Probe Visualizer是一种相当有效的FPGA原型板侦错方法。工程师再也不必局限在传统的侦错方法,而且在实时应用软件中增加观察点也可能会造成其它问题。透过维持原有软件并监测更多FPGA讯号在数百万时脉周期内的实时RTL行为,使用者可以获得所需的能见度,更完美的掌握、更轻松地侦错设计的问题。

总合来说,思源科技Probe Visualizer透过以软件为基础的创新方法,改变了原型板验证的方法,实现丰富、实时的设计能见度,并且让原型板能使用Verdi的侦错威力,使原型板侦错时间比传统的方法大幅缩短一半。

上一篇:莱迪思举办电源及平台管理研讨会

下一篇:基于DSP和FPGA的电视观瞄系统设计

- 芯启源(上海)将持续发力,“做深做精”EDA及IP产品

- 本田严厉警告日产:若与鸿海合作,那么本田与日产的合作将终止

- Microchip推出新款交钥匙电容式触摸控制器产品 MTCH2120

- Matter对AIoT的意义:连接AIoT设备开发人员指南

- 我国科学家建立生成式模型为医学AI训练提供技术支持

- Diodes 推出符合车用标准的电流分流监测器,通过高精度电压感测快速检测系统故障

- Power Integrations面向800V汽车应用推出新型宽爬电距离开关IC

- 打破台积电垄断!联电夺下高通先进封装订单

- Ampere 年度展望:2025年重塑IT格局的四大关键趋势

- 存储巨头铠侠正式挂牌上市:首日股价上涨超10%

SOC设计方法与实现 第二版 郭炜

SOC设计方法与实现 第二版 郭炜 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号