摘要:利用国际空间数据系统咨询委员会 (CCSDS)高级在轨系统(AOS)建议,提出了两级复用的方案,设计了一种具有载荷数据存储功能的高速实时/回放分级复接器。该方案采用FPGA技术,对星上载荷输出的数据使用了两级全异步复用的策略进行数据存储和虚拟信道调度。试验结果表明该复接器较好地实现了载荷数据的存储和复接功能的集成,并且功能灵活,硬件资源利用率小。

1.引言

随着卫星通信系统的迅速发展,空间链路能提供的数据传输速率越来越高,允许各类卫星平台上能够应用产生大量高速实时数据的有效载荷。由于各载荷的工作模式,数据量,数据格式、速率和实时性要求各异,空地之间数据传输交互时间短且容易中断,星载数据处理系统应当具有大容量存储和高速处理能力,能够在数据下行至地面之前对其进行存储、复接和其他准备工作。

高速复接器在空间数据传输中负责将有效载荷产生的各种数据复接下行,新的数据传输需求也对高速复接器的性能和灵活性提出了新的要求。传统的星载数据处理系统通常将载荷数据的复接和大容量存储分开处理,但是对于一些小型卫星,需要存储的数据量(如科学实验数据,图像观测数据等)并不是特别大,对实时性要求也不高。如果采用传统的处理方法将会占用比较多的星载资源,高速复接器和大容量存储器的设计、实现和协作也较为复杂。针对这种需求,本文提出了两级复用的理念,为高速复接器加入了数据存储的功能,参照 CCSDS AOS建议,提出将数据的实时传送和非实时回放统一起来处理的两级复用方案,基于 FPGA技术设计和探讨了小型、灵活的高速实时 /回放分级复接器的硬件实现和技术方案,以实现星上有效载荷数据的复接、存储和回放功能的集成化。

2.AOS高速实时/回放分级复接的研究

2.1 高级在轨系统( AOS)及虚拟信道复接为了应对新的空间需求,国际空间数据系统咨询委员会(CCSDS)于 1986年提出了AOS建议书,提供比常规建议书更为多样、灵活的数据处理业务,以应对高级在轨系统、国际空间站等复杂系统的需要。CCSDS协议提供给AOS空间链路子网的一个关键特性是虚拟信道的概念。将一个物理信道划分成多个逻辑信道,每个逻辑信道被单独识别并传输一种数据流,各数据流可以使用不同的业务,一个逻辑信道就是一个虚拟信道。虚拟信道使得一个物理空间信道被多个高层数据流以时分复用的方式共享,多种不同类型的数据在一个物理信道上传输成为可能,从而奠定了复接的理论基础。

2.2 两级复用方式的提出

虚拟信道时分复用物理信道,对物理信道按照一定的复用方法进行动态管理。由于高速实时/回放分级复接器需要完成存储和复接两方面的任务,单纯使用一级异步复用很难完全实现其需求。因此,本文对CCSDS高级在轨协议进行了合理剪裁,提出了两级复用的构想。在原有的虚拟信道复接之前增加一级存储的过程,两级虚拟信道复用均采用全异步复用方式。第 1级复用,根据信道优先级生成AOS传输帧,将有效的数据帧存入存储单元成为历史数据。第 2级复用,再次采用异步复用方式,根据信道优先级选择信道,将各路实时数据和一路历史数据按照一定的信道调度算法按照AOS传输帧的格式混合复接下行。

3.高速实时/回放分级复接器的技术方案

3.1 FPGA芯片选择

本设计选用90nm工艺技术的150万门XILINX SPARTAN-XC3S1500芯片。由于复接器需要的数据输入输出速率较高,因此对于FPGA芯片的 I/O速度要求较高。SPARTAN-XC3S1500芯片每个I/O口支持 622Mb/s的数据传输率,能满足设计的要求。其算术处理功能也能满足相对复杂的计算要求。这款芯片既能满足较为复杂的时序功能,又能解决速度快、功耗小、集成度高、设计灵活等技术要求。

3.2 系统总体技术方案

为了节省星上资源,提高载荷数据处理的灵活性,本文应用提出两级复用的理念,基于FPGA技术设计了工作于空间数据链路层的 AOS高速实时/回放分级复接器,整体功能框图如图 1所示。

图 1 CCSDS AOS高速实时 /回放分级复接器功能框图[page]

3.3 存储和调度算法设计

AOS高速实时 /回放分级复接器的设计重点在于虚拟信道调度的算法。高速率、高信道利用率的虚拟信道调度策略的设计是分级复接器设计的关键技术之一。调度策略算法的合理设计将保证AOS高速实时 /回放分级复接器能够高效、有序地完成存储和复接传输的功能任务。本设计的虚拟信道调度算法框图如图 2所示。

在各级工作状态下,首先由信源速率确定各虚拟信道的优先级。然后复接器根据各数据源缓存区和存储单元的存储空满状况确定接入的虚拟信道。

在第一级复用状态下,被选择接入的虚拟信道业务数据单元将以CCSDS AOS的标准帧格式存入存储单元,存储单元的写使能仅在接入有效数据帧时打开,保证只有有效的数据帧才能进入存储单元,以节省存储空间。进入在第二级复用状态以后,存储单元中的历史数据与其他路实时数据一起复接下行,各路异步数据缓存根据现有存储状况向虚拟信道调度模块发出传输请求,虚拟信道调度模块根据优先级策略选择接入的异步信道。如果没有有效的异步数据,则根据填充机制发送填充数据。

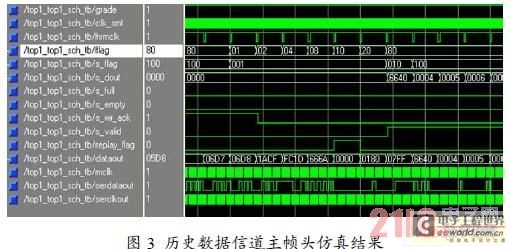

对于AOS高速实时/回放分级复接器而言,传输帧主帧头中的虚拟信道标识、虚拟信道帧计数和回放标志的设计是存储和虚拟信道调度的关键标识。虚拟信道标识区分了接入信道的各路数据,回放标志区分了实时数据和历史数据,而虚拟信道帧计数记录了每一路信道各帧数据的先后顺序。为了保证地面接收到载荷数据以后可以完整、无误、便捷地还原历史数据,两级复接成帧时使用了统一的虚拟信道帧计数和虚拟信道标识。这样在发送端经过两次复接之后下行的数据,在地面接收端只要进行一次解帧就可以还原。因此使用这种灵活的设计,不必改变现有的地面接收设备,使AOS高速实时/回放分级复接器具有很强的可移植性。两级复接后历史数据信道主帧头的仿真结果如图 3所示。

3.4 硬件验证演示系统及测试结果

搭建如图4所示的验证演示系统,对AOS高速实时 /回放分级复接器的功能进行验证。在演示系统的发送端,图像数据转换为码流,和科学实验数据一起作为高速分级复接器的信号源,进入复接器为信号源准备的缓存区中。经高速分级复接器复接下行后,成为一路串行输出。接收端将接收到的串行码流经过帧同步后送到接收与分路处理设备进行虚拟信道分路,并提取各虚拟信道的业务数据单元,最后送到计算机终端,在计算机终端可以分别看到恢复完整的科学实验数据和图像数据。

测试结果表明, AOS高速实时/回放分级复接器可以较好地进行存储和复接任务,各虚拟信道数据保持流畅,无丢失现象,串行输出速率为50Mbps。

4.结束语

本文介绍了 CCSDS协议高级在轨系统的复用方式和AOS传输帧结构,提出了两级复用的构想,探讨了AOS实时/回放分级复接器的硬件实现和技术方案。由于采用FPGA大规模逻辑器件,同时对AOS协议进行了合理的剪裁,使设计体积小、性能灵活且易于移植。本课题的研究将为航天应用工程中数据处理关键设备的集成提供思路,对进一步研制轻小灵活、高效适用的星载数据管理设备具有指导意义。

本文作者创新点:第一,提出了两级复用的理念,充分利用全异步复用灵活及高效的特点,通过对CCSDS AOS协议进行合理的剪裁,使两级复用相互配合,完成兼顾存储、复接和回放的任务。第二,给出了基于FPGA的AOS实时/回放分级复接器的完整设计方案,设计思想灵活,在发送端经过两次复接之后下行的数据,在地面接收端只要进行一次解帧就可以还原,不必改变原有的地面接收设备,具有很强的可移植性。

上一篇:基于FPGA的高精度时间数字转换电路设计

下一篇:一种应用于OFDM系统中的符号精确定时算法的FPGA实现

推荐阅读最新更新时间:2024-05-02 22:18

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号