1 背景

信号源作为现代电子产品中的重要一员,必须满足高精度、高速度、高分辨率等要求。作为检查高精度雷达设备的动态信号源更需要满足这些要求。雷达测量设备在日常维护保养中,由于没有也不可能用跟踪动态目标来完成设备性能的检查,所以都是用信号源产生信号进行检查,而信号源无法模拟实际动态信号,因此在多数情况下无法准确地检查设备的动态性能。本文研究并实现了基于FPGA(Field Programmable Gate Array)的智能动态信号源,采用了DDS(Direct Digital Synthesis)技术。FPGA与DDS相结合的方案显示出很多突出的优点:高频率分辨率;超宽的频率范围;能实现各种调制波和任意波形的产生;关键部分易于实现全数字化。

2 DDS原理及理论分析

2.1 DDS原理

DDS即"直接数字频率合成",是一种较新颖的频率合成技术,经过几年的发展,现在已经成熟,应用非常广泛。这种技术的基本原理是使用高稳定的参考时钟源来量化抽样时间间隔,直接对要产生信号进行抽样、量化和信号映射,然后经过D/A转换和低通滤波,输出需要的模拟信号。其原理如图1所示。

|

通常情况下累加器的位数一般都比较高,以获取高的频率和相位分辨率,但考虑到如下两个原因,一般函数发生器只用N位累加器中的高M位,而舍去其低位:一是函数发生器(波形存储器)的RAM的存储容量有限;二是由于数/模转换的精度限制和外界干扰的影响,随着位数的增加,其输出的幅度值的分辨率无法随之无限制地增加。

2.2理论分析

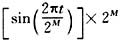

2.2.1 DDS输出频率表达式 360°/2M (1) 2.2.2 系统的频率分辨率 2.2.3 系统可输出的最高频率 3.1动态信号产生流程 3.2关键参数设计 3.2.1 参考时钟选择 3.2.2 累加器位数选择 取NCO相位累加器的位数为N=40。 3.3主要芯片选择 3.3.1 FPGA芯片的选择 Altera公司的Stratix芯片可以满足需要。该芯片的核心电压为1.5 V,采用O.13 μm,全铜技术制造,最大寄存器容看锏? Mb。 3.3.2 数字模拟转换芯片的选择 3.4算法设计 3.4.1 频控码算法 k=(fo×2N)/fc 3.4.2波形数据算法 其中,M为函数发生器数据宽度,在此为14,t为时间单位,在此为整数,取值范围为:0,1,…,2M-1,实际上t就是函数发生的输入地址值。 4 产生信号波形图 从图3中可以看出,输出为5 MHz数字信号,该信号是在固定频控码增量条件下产生的。经过多次采样和波形比对,其频率是变化的。由于一个周期只有5个采样点,所以信号波形看起来不是很光滑。通过8566A频谱分析仪观察频谱,产生的5 MHz信号的频谱特性非常好,杂波抑制在70 dB以上,谐波抑制在45 dB以上。 5 结语

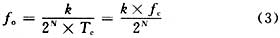

fc为参考时钟频率,Tc=1/fc;fo为输出频率,To=1/fo;k为频率控制字,即相位增量。

设累加器的长度为N位,函数发生器产生一个周期正弦波输出是M位(N位中的最高M位,M

同样,N位中的LSB相当于2π/2N弧度。该360°/2N弧度就是最小的相位增量。于是,k值对应的相位增量就是k*2π/2N弧度。这样,完成一个周期的正弦波输出需要经过2π/(K*2π/2N)个参考时钟周期,即2N/K个周期。因此,可以得到输出频率的周期为:

可见,输出频率fo与频率控制字k成正比。如果已知输出频率fo,即可算出频率控制字k。

当k=1时,对应输出频率为可输出的最低频率值,也就是频率分辨率:

fo=fc/2N (4)

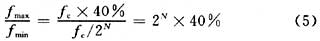

理论上,输出的最高频率主要受奈奎斯特频率的限制。根据采样定理,当k=2N-1时,系统输出达到理论输出的最高频率:fo=fc/2。但在实际设计的DDS系统中,由于以下几个原因,设计的最大输出频率必须小于fc/2:一是输出滤波器的非理想性,一般输出信号的最大频率为参考时钟频率fc的40%左右;二是如果产生的是正弦信号,且输出的频率为采样时钟的一半,同时采样点正好处于零点,则无法产生需要的信号。但是从以上几点分析,DDS系统可以得到非常宽的频率调节范围,其相对带宽为:

3 动态信号产生器的设计

系统框图如图2所示。动态信号产生器的核心部分DDS的数字部分用FPGA实现。同时FPGA还接收外部控制信号和产生用于控制整个电路工作的同步信号,向PC微机发送FPGA工作状态。图2中NCO,D/A转换和滤波电路构成了DDS电路。寄存器用来存放产生动态信号的频控码;时钟处理电路用来产生采样时钟信号和同步信号;串口电路用来完成与微机接口的任务,接收来自于微机的控制信号和数据。NCO由锁存器、相位累加器和波形存储器(RAM)构成。锁存器作为相位增量寄存器,相位累加器用于实现地址的累加,用该地址信息从波形存储器中获取相应的波形数据。波形存储器用于存放各种波形数据,可通过计算机来产生多种信号波形数据,从而实现信号源的多功能化。经过波形存储器后,将这些数字信号进行数/模转换得到模拟信号。最后再通过运算放大器和滤波整形电路将信号滤波、放大后输出。

由表达式(3)可以看出,只要频控码k变化,则输出频率随之变化,从而实现信号频率的改变。

图2中虚线内为FPGA部分,虚线外部分主要为FPGA服务。其中存储器完成对FPGA配置的功能;接口电路完成电平转换功能主要是将FPGA输出的TTL电平转换成RS 232标准电平。

滤波器设计采用了晶体滤波器,以滤除所产生动态信号的相位噪声,满足雷达设备应用。

由于要产生的信号频率为5 MHz,由上述分析可知,参考时钟必须大于:

在此选择了fc=25 MHz。

累加器位数的选择主要决定于5 MHz信号的频率分辨率,本动态5 MHz信号产生器需要的分辨率为δ=8×10-5Hz,根据表达式(4),可计算出累加器的位数N。

其中,fc=25 MHz为时钟频率,δ为分辨率,则相位累加器的位数为:

3.2.3 函数发生器位数选择

函数发生器位数的选择主要决定于输出5 MHz信号的相位分辨率,本动态5 MHz信号产生器需要的分辨率为a=0.034°,则根据表达式(1),可计算出函数发生器位数为:

取M=14。

由于频控码在产生动态信号前,需要全部装入FPGA的RAM中,所以FPGA的RAM必须满足一定要求。计算过程如下:

产生动态信号时间长度设定为500 s,每秒频控码为80个,所以,共有:500×80=40 000帧数据。每帧数据为16位,共需寄存器的位数为:40 000×16=640 000。在NCO中还需实现函数发生器,函数发生器的地址宽度为14位,数据宽度也为14位,则需要的寄存器位数为:214×14=229 367。所以最终需要的寄存器位数为:640 000+229 376=869 376。

其次,FPGA中必须有专用时钟处理电路,最少要有2个PLL。NCO需要的时钟较多,且时钟之间有严格的时序关系。时钟的类型主要有:数/模转换需要的时钟;串口时钟;参考时钟;80 Hz信号。

相位累加器的位数为14位,所以D/A转换器件的位数也必须是14位的。经过选择比对,AD公司的AD9754数/模转换器件可以满足要求。该数/模转换器具有14位精度,最大调整率为125 MSPS,片上集成了两级输入寄存器和参考电流源,所以设计电路简单,操作灵活,只需要较少的外部元器件就可以完成数/模转换功能。

AD9754为电流型输出器件,需要进行电流电压转换。拟用AD公司AD9631运算放大器完成电流电压转换功能,该运放的单位增益带宽在大信号情况下为175 MHz,在小信号情况下更宽。供电电压为±5 V,输出摆率为1 300 V/μs。

软件设计主要包括配置FPGA、计算波形数据和频控码数据。同时软件还要完成监控显示任务。软件开发用VC++,操作系统用Windows NT。由软件计算频控码并通过串口发送到FPGA的RAM中。波形数据可以以初始化文件形式写入FPGA的RAM中,可写入正弦波、三角波、方波等波形,还可写入各种调制波形。不同的波形数据用函数发生器地址加以区分,这样可随时改变输出信号的波形。系统控制命令发出后便可脱机工作。

根据表达式(3),可以得出计算频控码的表达式如下:

表达式如下:

在调试阶段,利用FPGA开发板对设计进行了验证,工作正常,波形如图3所示。

通过产生的动态5 MHz信号对高精度雷达设备进行检查,证明了本方案是可行的,能够完成对设备动态性能的检查,使设备的维护保养更具有针对性。

上一篇:宽频带数字锁相环的设计及基于FPGA的实现

下一篇:飞思卡尔具高级安全功能的新MSC8144 DSP

推荐阅读最新更新时间:2024-05-02 20:27

开关电源入门

开关电源入门 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号