简单地说,云中的一切都迫切需要更多的带宽。企业数据中心需要更多带宽;超大规模,云和HPC中心需要更多带宽; 5G部署进一步加剧了蜂窝运营商对更多网络带宽的需求,以满足不断增长的WAN容量需求。对于所有这些网络设备的大量用户,添加更多100G以太网(100GE)端口将无法满足带宽挑战。其他端口需要更多的机架空间用于服务器和交换机,并且需要更多的服务器机架空间;这些解决方案不经济。从100G迁移到400G以太网(400GE)端口是向数据中心注入更多带宽的一种便宜得多的方式。

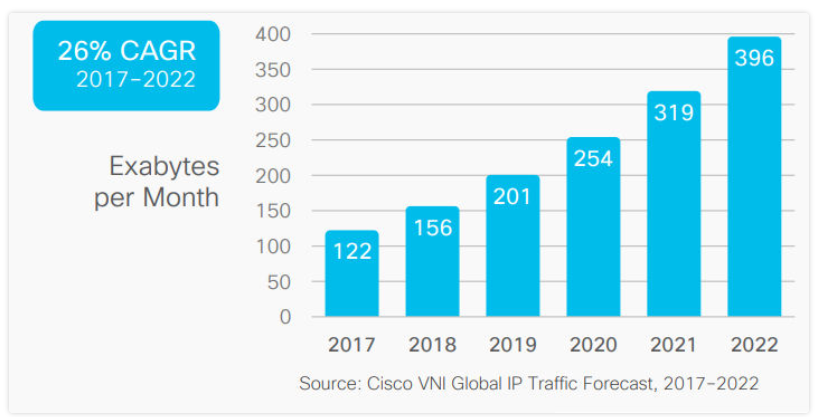

根据思科2017 - 2022年的视觉网络指数(VNI),报告涵盖的五年内每年的IP流量将增加三倍以上,如图1所示。该报告预测全球IP流量将达到4.8 ZB(zettabytes)每年到2022年。这是每月396 EB(艾字节)。 (exabyte是1018字节。)2017年,全球IP流量的年度运行率“仅”每年1.5 ZB或每月122 EB。同样的思科VNI预测,繁忙时段的互联网流量,即当天最繁忙的60分钟,将在同一时期增加4.8倍。

图1:思科视觉网络指数预测从2017年到2022年,IP流量将增加3倍以上。

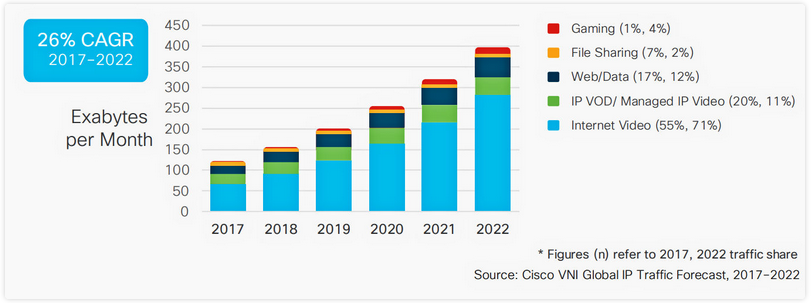

虽然所有IP流量的流量都在增长,但视频流是增长最快的因素。 IP视频流量包括对等视频服务的爆炸性使用,例如Apple的FaceTime,微信视频通话,Facebook Live,Microsoft Skype;快速增长的VoD(视频点播)服务数量,包括Netflix,亚马逊视频,YouTube电视,Hulu和刚刚宣布的迪士尼+;以及通过MSO(多个系统运营商,包括有线和卫星广播提供商)提供管理的IP视频广播服务。思科的VNI预测,视频IP流量将在同一时期内增加3倍,到2022年将占所有IP流量的82%,如图2所示。

图2:根据思科的视觉网络指数,到2022年,82%的IP流量将携带视频(每个条形的蓝色和绿色部分)。

流经这些网络的大部分IP视频将被移动设备消耗。思科VNI预测,到2022年,71%的IP流量将成为移动流量。这一移动流量的很大一部分将通过蜂窝运营商的WAN以及连接和内部数据中心的网络传输。这些数据中心的存储服务器提供了大量信息,包括流经全球互联网的视频。

将数据中心数量增加四倍或五倍以处理增加的网络流量非常昂贵并且没有任何吸引力。在许多情况下,物理扩展现有数据中心要么不可能,要么同样没有吸引力。包括Dell'Oro Group在内的分析师预测,公共和私有云提供商以及蜂窝网络运营商将通过迁移到400GE网络和交换机来解决数据中心内的常见带宽挑战。

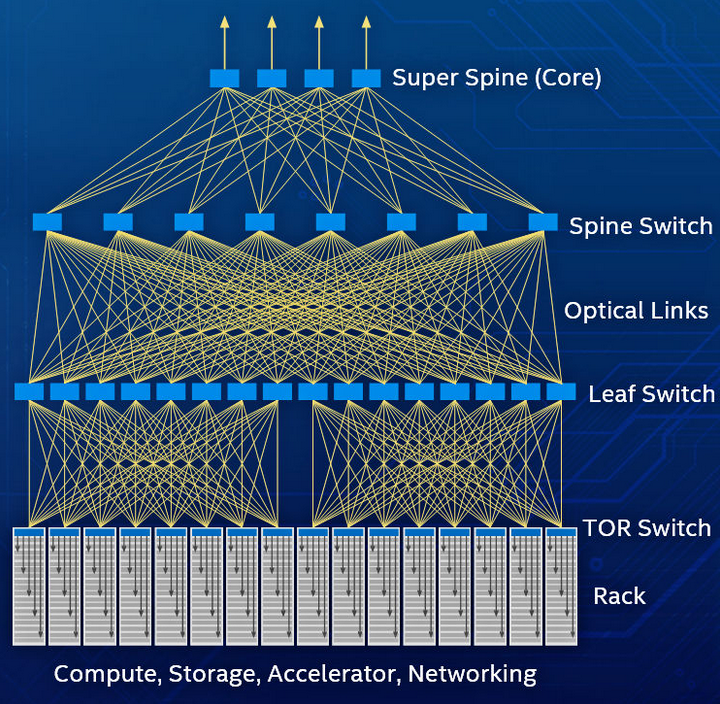

随着带宽需求的增长,早期的数据中心的网络架构是典型的三层树型结构,现在已经转变为大二层结构。如图3所示。满足数据中心带宽要求的挑战的最简单和最经济的方法是将数据中心内的交换机迁移到400G光纤链路。

图3:当前的数据中心架构采用叶脊拓扑网和主干网络拓扑。 (图片来源:英特尔)

英特尔在OFC 2018上展示了用于数据中心应用的400G光模块,并为选定的客户提供了这些模块的样品。此外,英特尔还展示了英特尔 Stratix 10TX FPGA中内置的58G PAM4 SerDes收发器与英特尔和其他供应商的400G插入式光模块之间的互操作性。只需8个58G PAM4 SerDes收发器即可处理400G光模块的带宽要求。英特尔Stratix 10 TX FPGA是首款采用PAM4调制,支持57.8 Gbps双向收发器的FPGA。

英特尔Stratix 10 TX FPGA系列中每个器件具有60个高速SerDes收发器,每个器件能够使用PAM4调制以57.8 Gbps的速度运行。所有这些收发器通道都包含专用物理介质附件(PMA)和硬化物理编码子层(PCS)。在将数据传输到FPGA内核架构之前,PMA为高速物理通道提供主要接口功能,PCS处理编码/解码,字对齐和其他预处理功能。

一个400GE端口需要8个50 Gbps SerDes收发器,因此Intel Stratix 10 TX FPGA系列中最大的成员可以实现多达5个400GE端口。因此,英特尔Stratix 10 TX FPGA为新的400GE设备设计提供了出色的实施工具。 (注意:这些相同的高速SerDes收发器是双模收发器,可配置为使用NRZ调制以28.9 Gbps运行。28.9 Gbps NRZ模式也使英特尔Stratix 10 TX中可用的高速收发器数量翻倍)。

由于采用HyperFlex核心架构和英特尔14纳米三栅极工艺技术,所有英特尔Stratix 10器件的单片FPGA内核均能够以1GHz频率运行。最大的英特尔Stratix 10 TX FPGA内核包含275.3万个逻辑单元和5,760个具有硬浮点和定点计算能力的可变精度DSP模块,以及多个不同大小的嵌入式SRAM存储器模块。

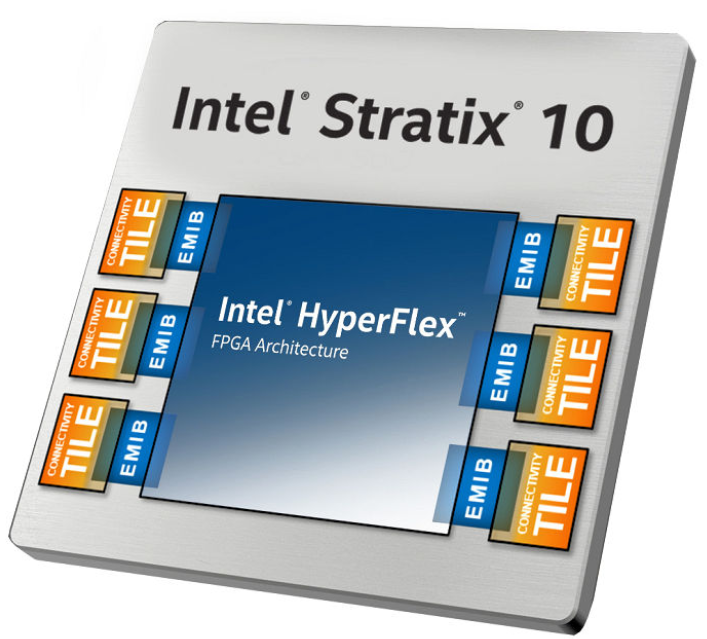

英特尔Stratix 10 FPGA采用异构3D系统级封装(SiP)技术,采用英特尔嵌入式多芯片互连桥接(EMIB)技术将多个芯片集成在一个封装中,该技术采用小型硅桥将多个芯片连接在一起封装,如图4所示。对于Intel Stratix 10 FPGA,封装中的一个大芯片包含单片FPGA内核。其他较小的芯片称为cell,为英特尔Stratix 10器件系列提供了多种接口选择。

图4:英特尔Stratix 10 FPGA和SoC采用英特尔EMIB互连技术,将单片FPGA芯片与多个连接区块绑定,提供各种I / O特性和功能。 (图片来源:英特尔)

英特尔Stratix 10 TX FPGA和SoC采用多达五个“E-tiles”来实现器件的多个58 Gbps PAM4 SerDes收发器。在PAM-4模式下,E-tile上的每个收发器通道都支持57.8 Gbps的数据速率,并针对新标准和新兴标准(包括OIF CEI 56 LR,MR和VSR)的短距离和长距离电气规范。这些高速SerDes收发器中集成的高级均衡电路可实现大多数高速串行协议所需的误码率(BER),这些收发器可支持高数据速率的传统和高损耗背板。

400GE设计需要高速Reed-Solomon前向纠错(FEC)和完整的400GE协议栈。英特尔Stratix 10 TX FPGA通过在英特尔Stratix 10 TX FPGA的E-tile中的固定硬件中实现FEC和最低级别的协议栈来满足这些要求,而400GE协议栈的较高部分通过可编程实现FPGA架构内的逻辑。

使用英特尔Stratix 10 TX FPGA实现400GE解决方案需要的不仅仅是快速的SerDes收发器。FPGA的内部逻辑结构必须处理通过SerDes收发器的多个高速数据流的极高数据速率。对于400GE设计解决方案,FPGA架构必须能够以366 MHz的最低时钟速率运行。英特尔Stratix 10 TX FPGA具有性能加倍的HyperFlex内核架构和1 GHz最大频率,可轻松实现此最低时钟速率。

英特尔提供经过测试的基于英特尔Stratix 10 TX FPGA的400GE端口参考设计,该产品通过测试和插件测试可与多家供应商的产品实现互操作。

上一篇:打造“FPGA+”新品类 Achronix 7nm FPGA算力提升10倍

下一篇:国产FPGA再获助力,上海安路D轮融资获得大基金领投

推荐阅读最新更新时间:2024-11-02 22:42

- 【已结束】 Qorvo & Keysight 直播【新一代无线连接的挑战与应对之道】

- 有奖直播|保护嵌入式设备与系统的完整性和可靠性——英飞凌 OPTIGA™ TPM 安全解决方案

- 下载设计资源,赢取“会说话”的啤酒托!

- EEWorld加磅双重礼 ELEXCON深圳国际电子展诚邀您参加

- ADI 新一期《模拟对话》上线,免费下载ing!

- 关注 PI 最新 SCALE-iDriver IC产品系列 答题有好礼!

- 爱“拼”才会赢 英飞凌栅极驱动IC拼图闯关 活动开始啦!

- ADI•世健工业嘉年华——电子书下载 活动开始啦

- 下载、答题赢好礼:使用Mentor的Xpedition Layout高效设计PCB

- 【EEWORLD第四十二届】2012年09月社区明星人物揭晓!

一种基于广义时间和传递常数的快速分析法_郑立博

一种基于广义时间和传递常数的快速分析法_郑立博 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号