引言

在嵌入式设计中常常会使用LCD屏,现在常用的屏大部分都是高性能的。因为LCD屏的生产厂商很多,标准也不统一,LCD屏往往不能与LCD控制器无粘合连接,所以在使用LCD屏时,厂家还会推荐使用其专为LCD屏是设计的时序芯片,例如,Sharp的LCD LQ035Q7DB02配套的控制器为LZ9FC22;日本的LCD屏是16位色的,本身价格很高,控制器成本也非常高,性能却不见得好,采用高性能的24位真彩色屏是比较理想的,但接口逻辑需要重新设计。

1 RGB565-RGB888的转换

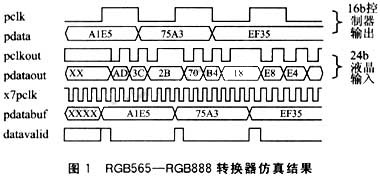

以友达光电AUO生产的A06QU01[1]为例,这是一种24位的TFT真彩屏,分辨率为320×240,每个象素由RGB888表示,其控制时序如图1所示,LCD要求的时序由帧同步(VSYNC)、行同步(HSYSNC)、比特时钟(DCLK)及数据(Data[0:7])构成,帧同步和行同步指示每一帧和每一行的开始。A06QU01每帧240行,每行320个象素,每个像素由依次产生的8b红、8b绿、8b蓝(R1,G2,B3,R4,G5,B6…)构成,所以称为RGB888。

|

|---|

以PXA25x为代表的嵌入式处理器拥有一个LCD控制器,可以将这个控制器配置为最高16位的TFT LCD屏控制器,其控制时序如图1所示,LCD要求的时序由帧同步(VSYNC)、行同步(HSYSNC)、点时钟(PCLK)及数据(Data[0:15]构成,帧同步和行同步指示每一帧和每一行的开始。对于A06QU01,每帧将有240行,每行有320个像素,每个像素由5b红、6b绿、5b蓝构成16位数据,称为RGB565。

将RGB565转换为RGB888要解决2个问题:

1)比特时钟3倍频。LCD控制器每一个像素用一个时钟1次送出16b数据,而LCD屏每个像素需要3个时钟,每次获得8b。这样就需要产生1个3倍于点时钟PCLK的时钟。

2)16b到24b数据分解。在LCD控制器送出16b数据时,需要缓存,并分解出RGB信号分别送出,5b红、6b绿、5b蓝构成16位数据可以采用补0的方法,构成8b红、8b绿、8b蓝。数据高位补0时色彩较柔和,低位补0时彩色较艳丽。

通常情况下,使用模拟锁相环技术可以实现均匀倍频,在这个设计中,3倍频时钟与RGB数据必须同步,否则会出现颜色错位;同时锁相环还需要数据分解电路配合使用,这样一个数字和模拟混合的电路会增加成本,因而特别设计使用了数字电路实现非均匀3倍频。具体方案是:使用一个大于6小于7倍的LCD屏比特时钟作为CPLD的主控制时钟,LCD屏的时钟频率约为7M赫兹,所以选择CPLD的主控制时钟频率为48M赫兹。如图1所示,pclk为控制器输出的点时钟,pdata为RBG565数据,pclkout和pdataout是送往LCD的信号,x7pclk为CPLD的定时时钟,在pclk上升沿将pdata存入缓冲器pdatabuf,并将内部状态位datavalid置位,在x7pclk的上升沿,如果检测到datavalid为高,则使pclkout为低,将缓冲器中的数据取出高5位红色信号,补零后送到pdataout,并将datavalid置为低,在下一个x7pclk的上升沿将pclkout置高,8b数据送出到LCD屏。使用这种方法依次将绿色及蓝色信号送出,在蓝色信号送出后,保持pclkout为高,直到下一个datavalid为高,进入下一次转换,从图1中可以看出,数字3倍频信号pclkout不是均匀的,蓝色数据时钟的占空比不是50%。根据LCD屏数据手册的要求,pclkout的占空比变化容许的范围是40%-60%,因而只要调整好x7pclk的时钟频率,还是比较容易产生符合占空比要求的pclkout时钟的,LCD屏正常工作还需要帧同步(VSYNC)和行同步(HSYSNC)信号,这些信号可以由软件驱动程序编程产生。

2 LCD背光及LCD偏置的电源产生器

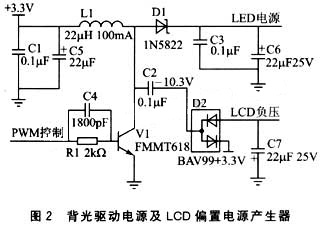

LCD屏需要特殊的供电,用于背景照明和LCD偏置,现在使用的小尺寸LCD大多数使用LED作为背光,以及-10V的偏置电压,本设计使用的LCD屏是2路各4个白光LED串联,每路需要的供电电压约为10V,电流为20mA。LCD偏置电压为-10V,电流为3-5mA。这些电源利用LCD控制器内部的电源控制器实现。如图2所示,由L1、V1构成升压型DC-DC转换器,L1为高频功率电感,V1为高频小功率开关晶体管。C4和R1构成的微分电路可以提高V1的导通和关闭速度,有利于提高电源效率,V1由脉冲宽度调制信号控制,在导通期间使用L1存储能量,在关闭时电感向负载释放能量,这样V1的集电极上生成高压脉冲信号,这个信号经过D1、C3和C6整流滤波后得到用于LED供电正电压,同样经过C2隔直流后再整流滤波得到用于LCD偏置的负电压,注意,电容C7是正端接地的。LED电流限制使用图3所示的电路,V3和V4为LED驱动管,V2为电流采样管,V2、V3、V4是3个型号相同的晶体管。这3个晶体管的基级相连,因而基极电压相等。因为型号相同,所以基极到发射极电压近似相等,于是,R3、R6、R7上的压降近似相等,这样R3、R4上的电流被转换为R2上的反馈电压。控制器根据反馈电压自动调整图2中的PWM控制信号的占空比,从而改变输出LED供电电压,使反馈电压稳定在0.6V,通过LED的电流稳定在22mA,LCD偏置电压大约稳定在-10V。

|

|---|

|

3 数字倍频及数据分解实现

RGB565-RGB888转换器用XC9536实现,如图4所示,来自LCD控制器的信号为:16b数据L_DD0..15、同步信号L_FCLK及L_LCLK、点时钟信号L_PCLK,输出到LCD屏的信号为:8b数据信号LCD_D0..7、同步信号LCD_VSYNC及LCD_HSYNC、时钟信号LCD_DCLK。X7CLK来自于48M赫兹的晶体振荡器,使用Verilog HDL开发。如果连接无误,则上电后加载带有TFT屏驱动的嵌入式Linux内核,一般在LCD屏左上角能看到企鹅图案,如果实际显示的图案位置和色彩不正确,则需要根据实际看到的图像调整LCD控制寄存器中的时序设置,实现正确的显示。

|

|---|

4 总结

由于接口标准不统一、将一个新型号的LCD屏接到嵌入式处理器比较困难,需要认真分析LCD控制器及LCD屏的时序和驱动方式,使用低价可编程逻辑电路,可以实现接口的时序转换,LCD屏需要的背光电源及偏置电源可以按本文所述方法,利用LCD屏内部集成的电源控制器实现,也可以通过外接专用的LCD背光电源和LCD偏置实现。

上一篇:基于AT89C51的激光密码锁的设计

下一篇:基于CMX860的来电显示电话测试仪的设计

推荐阅读最新更新时间:2023-10-18 14:32

Vishay线上图书馆

- 选型-汽车级表面贴装和通孔超快整流器

- 你知道吗?DC-LINK电容在高湿条件下具有高度稳定性

- microBUCK和microBRICK直流/直流稳压器解决方案

- SOP-4小型封装光伏MOSFET驱动器VOMDA1271

- 使用薄膜、大功率、背接触式电阻的优势

- SQJQ140E车规级N沟道40V MOSFET

【得捷电子Follow me第2期】四个任务的程序源码

【得捷电子Follow me第2期】四个任务的程序源码 基于lvgl构建的多任务程序框架

基于lvgl构建的多任务程序框架 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 ISL28110FBBZ

ISL28110FBBZ

京公网安备 11010802033920号

京公网安备 11010802033920号