图3.19举例说明的是一个100MBPS的数据传输系统。由于码间干扰和附加噪声,在D点输出的信号波形比A点的波形呈现了更多的抖动。这里主要讲的就是如何正确展现输出波形的抖动特性。

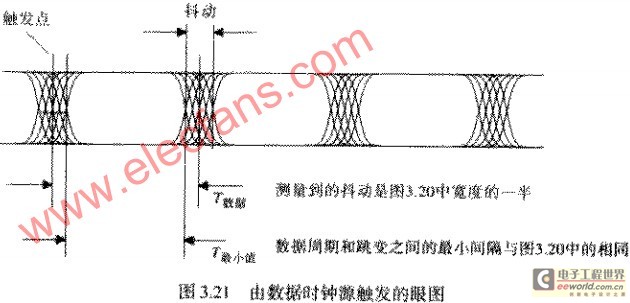

第一步把信号D连接到示波器通道1。我们选择通道1作为触发通道,并调整示波器使之在信号的上升沿触发。我们会看到图3.20所示的图案。

注意,波形在触发点处显示出是没有抖动的,这是一个关键的指示:肯定是某个地方出错了,示波器等待信号的正向跳变,然后把数据波形移位到左侧光标处与触发点对齐。第一个脉冲正确展示了信号的正向跳变,然后把数据波形移位到左侧光标处与触发点对齐。第一个脉冲正确展示了信号跳变的最小时间间隔,而围绕后继时钟点的抖动误差是实际的数据时钟抖动时间的两倍。

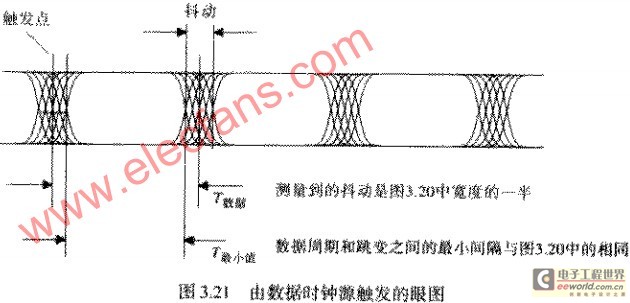

图3.21给出了测量的正确显示。图3.21中信号的触发是采用时钟源作为绝对参考的。显然,这里显示出来的抖动是前面抖动值的一半。前面的方法使所有的波形都有位移,所有的上升沿都在同一点处对齐。这种位移会叠加到其他所有的跳变区域当中去,时钟源信号比较稳定,没有抖动,是所有数据信号测量的可靠参考点。

有人会问道:“为什么不能用图3.20中的技术,然后把结果除以2呢?”回答是:只有当图3.20的眼图张得足够大时,抖动的测量才得以进行,而我们并不总是这样幸运。有时,如果我们不采用图3.21所示的高级触发技术,眼图根本就无法张开。

当没有源数据时钟时,可以尝试用源数据信号进行触发(如图3.19中的位置B或A)。源端的数据信号几乎没有抖动。

有些示波器,尤其值得注意的是大多数新式的数字采样示波器,其触发能力比较差,尤其是对非周期性的信号,如数据波形,尽管垂直输入具务显示高速信号的能力时,触发电路有可能无法触发。当面对这样的触发特性不好的示波器时,应该首先构造一个数字电路,对系统时钟进行分频处理,然后采用这个二次波形进行触发。随着触发稳定性的提高,可能会发现示波器上显示的信号上升时间有所减少。

关键字:串行数据 传输系统

引用地址:

如何观测一个串行数据传输系统

推荐阅读最新更新时间:2024-03-30 22:16

高速串行数据链路的自动化一致性测试

引言 每一位从286时代就开始接触PC的朋友一定能深刻体会到计算机技术飞跃进步给我们的生活和工作带来的便利性,这些技术进步主要体现在CPU的主频越来越高,存储器容量越来越大,以及芯片与芯片、模块与模块、系统与系统之间互连总线的数据传输率也越来越快。图1描述了一块典型的计算机主板,其上运转的总线类型可能包括以太网、USB、PCIExpress、SAS、HDMI、SATA、FBDIMM和UWB等。这些总线结构的共同点是:①都是串行数据链路,发送和接收采用两对差分信号线传输,没有单独的时钟线,数据格式已包含了时钟;②数据传输速率非常高,能达到Gb/s甚至10Gb/s速率级别以上,因而串行数据也是设计中必须重点考虑的问题;③同一总线上的

[测试测量]

编写单片机串行通信的数据发送程序

请编制串行通信的数据发送程序,发送片内RAM50H~5FH的16B数据,串行接口设定为方式2,采用偶校验方式。设晶振频率为6MHz。 解:查询方式发送程序如下 MOV SCON,#8OH M OV PCON,#80H MOV R0,#50H MOV R7,#16H LOOP: MOV A,@R0 MOV C,P MOV TB8,C MOV SBUF,A JNB T1,$ CLR T1 INC R0 DJNZ R7,LOOP RET

[单片机]

串行通信采用奇偶校验方式发送数据

编制串行通信的数据发送程序,发送片内RAM50H~5FH的16个字节的数据,串行接口设定为方式2,采用奇偶校验方式。设晶振频率为6MHz。 ORG 0000H LJMP START ORG 0030H START: MOV SP, #30H MOV PCON, #80H MOV SCON, #80H MOV R0, #50H MOV R7, #16 LOOP: MOV A, R0 MOV C, P ;红色部分为奇偶校验方式 MOV TB8, C MOV SBUF, A JNB TI, $ CLR TI INC R0 DJNZ R7, LOOP SJMP $

[单片机]

串行数据一致性测试系列之二--串行数据测试发包方法的讨论

在串行数据测试中,经常会使用专门的测试夹具把待测试信号引入示波器中测量和分析,这 时,待测试的串行信号链路并不在正常工作状态(即正常的业务数据流模式),而是工作在测试模式,待测试芯片的该串行链路的发送端必须强制发送出测试数据 包,然后通过测试夹具和同轴电缆连接到示波器,本文将简要讨论串行数据测试时如何发送出数据包。 百兆/千兆以太网 在 很多3C产品中都有RJ45接头的以太网口,最常见的速度为百兆和千兆,对应的标准为100BASE-TX和1000BASE-T,使用非屏蔽双绞线来连 接网口。通常,网卡芯片厂商提供了发包程序或者修改寄存器方法,让网卡芯片发出特定的测试数据包。比如Intel的LanConfig软件适用于所有 Intel

[测试测量]

基于SAA6752HS的嵌入式视频监控和传输系统设计

摘 要 :主要介绍了以SAA6752HS 为核心的实时视频压缩和传输系统,详细讨论了其结构与硬、软件实现。该系统成本较低、使用灵活, 可方便地嵌入到需要视频监控的监测系统中。 关键词: 视频采集;MPEG2 硬压缩;数据以太网传输;SAA6752H 引言 人类接受信息中有70%是视频信息。相对于语音和文字信息来说,视频信息更直观,信息量更大,处理和传输技术也更为复杂。视频监控系统作为视频技术的一个应用领域,在军事安全等领域发挥着重要的作用。目前视频监控系统主要采用模拟和数字两种技术。数字视频技术不仅能减少视频传输引起的失真,还能对视频信息进行分析、识别及有效信息提取。因此随着数字技术的进步,数字视频监控

[安防电子]

1394技术及其在图像传输系统中的应用

摘要:为了最大限度地利用现有硬件资源,缩短开发周期,研制了1394-PCI的转接卡,实现了基于1394的高速图像传输系统。介绍了1394高速串行总线的特性及原理及1394-PCI转接卡的硬件、软件设计。

关键词:1394高速串行总线 1394-PCI转接卡 设备驱动程序

当今的计算机外围设备都在追求高速性和高通用性,尤其在进行图像数据处理和传输时,数据的大指、高速、实时性对计算机与外设的接口提出了更高的要求。

目前新型总线接口有两种:USB和1394接口。它们都支持即插即用,具有易扩展、使用方便、成本低等特点。但在任何USB系统中,只能有一个主机,最多可接127个外设,在全速模式下的传输纺为500kbps~10Mbps。而相

[网络通信]

高速串行数据通信发送芯片CY7B923的原理及应用

摘要: 文章介绍了CYPRESS半导体公司推出的一种用于点对点之间高速串行数据通信的发送芯片CY7B923的原理及应用。较详细的介绍了CY7B923的管脚功能、内部组成、工作原理及工作方式。同时给出了一个实际电路来说明其具体的应用方法。

关键词: 串行数据通信 CY7B923 IDT7200 基带传输 差分PECL输出

1 概述

CY7B923是CYPRESS半导体公司推出的一种用于点对点之间高速串行数据通信的发送芯片。CY7B923采用的是基带传输通信方式,并支持带电插拔(热接插)。其内部电路主要包括时钟产生器、输入寄存器、编码器、移位寄存器、三对差分PECL输出对以及测试逻辑等。该芯片

[应用]

高速串行数据分析的整体解决方案

高速串行技术的不断发展,使得信号从发射机传送到接收机时,均会经过复杂的交互,最终发生严重的高频损耗。 全新的测试要求 计算机、消费电子和通信行业设计核心正采用最新的高速串行技术,数据传送速率持续提高,如10Gb/s以太网的出现、PCI Express已经从1.0版演进到2.0版,速率也从2.5Gb/s提高到5.0Gb/s、即将出现的8Gb/s PCIe Gen3和6Gb/s SATA III……高速串行技术的不断发展,使得信号从发射机传送到接收机时,均会经过复杂的交互,最终发生严重的高频损耗。这样,对串行数据的测试也必将面临前所未有的挑战:数据速率远远高出原有技术;信号完整性在整个链路中至关重要;需要提供复杂的分析和互通测量

[应用]

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

京公网安备 11010802033920号

京公网安备 11010802033920号