在串行数据测试中,经常会使用专门的测试夹具把待测试信号引入示波器中测量和分析,这 时,待测试的串行信号链路并不在正常工作状态(即正常的业务数据流模式),而是工作在测试模式,待测试芯片的该串行链路的发送端必须强制发送出测试数据 包,然后通过测试夹具和同轴电缆连接到示波器,本文将简要讨论串行数据测试时如何发送出数据包。

百兆/千兆以太网

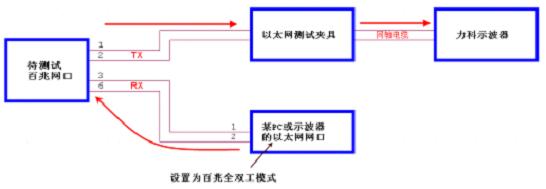

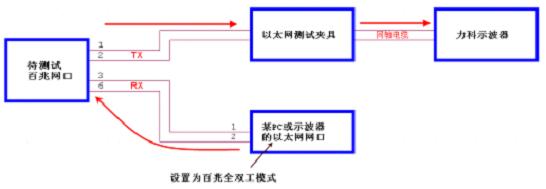

在 很多3C产品中都有RJ45接头的以太网口,最常见的速度为百兆和千兆,对应的标准为100BASE-TX和1000BASE-T,使用非屏蔽双绞线来连 接网口。通常,网卡芯片厂商提供了发包程序或者修改寄存器方法,让网卡芯片发出特定的测试数据包。比如Intel的LanConfig软件适用于所有 Intel的网卡芯片,Marvell、Realtek、Broadcom等等都有各自的发包程序和方法,测试工程师可以找网卡芯片公司或测试仪器厂商的 技术支持索要发包程序。不过对于百兆以太网口,可以用诱导发包方法让网卡芯片发出百兆测试数据包。下图1为使用该方法测试百兆以太网的示意图。后来我们设 计了新的百兆以太网夹具(产品代码为:TF-ENET-CN),包括了图1的电路,夹具上两个RJ45连接器,一个接待测试网卡,另外一个连接设置为百兆 全双工的网卡,示波器用同轴电缆连接到夹具即可观察到待测试网口发送出的数据包。

图1:百兆以太网测试的诱导发包方法

USB2.0

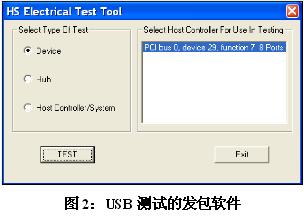

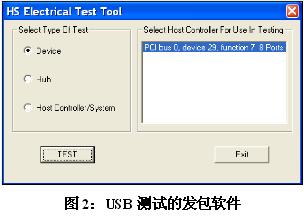

USB分为HOST和DEVICE两类:对于DEVICE,需要一台电脑,运行HSElectricalTestTool发包程序(可从www.usb.org下 载,如图2所示),按照示波器厂商的USB测试软件包的指示操作该发包程序即可让待测试DEVICE发送出适当的测试数据包。对于HOST,如果是可以运 行WINXP或WIN2K的USB端口,同样可以运行HSElectricalTestTool发包程序,按照示波器厂商的USB测试方法操作该软件,即 可发送出测试数据包;如果该HOST是嵌入式系统的USB端口,则需要USB芯片厂商提供发包方法。对于全速和低速的USB HOST测试,无需发包软件即可测试。

PCI Express

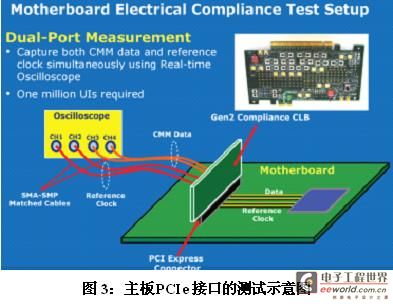

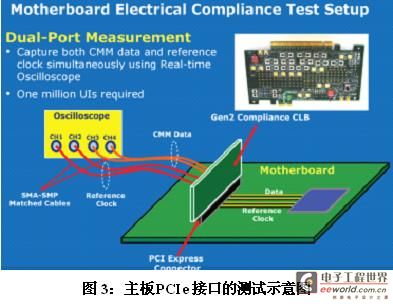

PCIe 的发包方法比较简单,PCIe的TX正负信号通过隔直电容后接到2个50欧电阻,PCIe芯片上电后可以发送出测试数据包,该数据包由 K28.5/D21.5/K28.5/D10.2组成。对于计算机主板上的PCIE 16X/8X/4X/1X的连接器,使用PCI官方组织PCISIG提供的测试夹具CLB进行测试,CLB插到主板上后,用同轴电缆连接CLB与示波器的 通道(通道的输入设置为DC50欧),主板上电后即可发送出测试数据包,示波器就可以测试PCIE了(如图3所示为PCIe Gen2的主板测试示意图)。对于PCIE的插卡,需要使用PCISIG的测试夹具CBB,CBB上提供了PCIe插卡的电源和时钟,把待测试PCIE插 卡插到夹具CBB,然后用同轴电缆连接CBB与示波器,对CBB上电后插卡就发出测试数据包到示波器。

SATA

SATA芯片的发包分为几种情况:

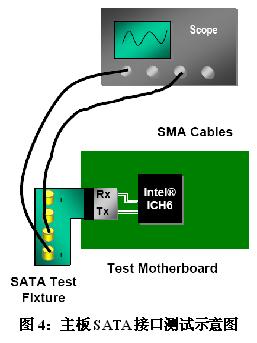

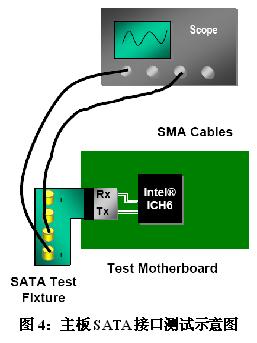

对 于PC客户,如果使用Intel芯片组的主板,可以运行RU软件修改寄存器,让ICH?(I/O Controller Hub)芯片发送出测试数据包。比如对于ICH6/7的SATA测试,DOS启动后运行RU软件,在RU软件中选择DEV 1Fh FUNC2的设备,然后把对应的4个地址的数值修改为00/1C/04/FF,即可发送出测试数据包。

PCI DEV31 = DEV 1Fh FUNC 2

92->00 A0->1C A6->04 92->FF

此 外,Intel提供了一个文档指导如何修改芯片寄存器、如何使用示波器和SATA测试夹具、如何运行Sigtest软件输出测试报告。文档名 为:Intel ICH? Serial ATA Motherboard Signal Quality Testing (MSQT),可向Intel技术支持索取。

SAS

SAS芯片厂商LSI LOGIC提供了发包软件,通常系统从DOS启动后,运行该发包程序,可以选择各种测试码型、还可以调节信号幅度和去加重程度。SAS的测试夹具与测试方 法与SATA类似。如果芯片厂商没有提供发包软件,也可使用力科SAS协议分析仪,通过夹具的RX端配置SAS芯片发送测试数据包。

HDMI

对 于HDMI Source的测试,通常先连接显示器后设置到各种分辨率(比如1080i、720p等等),然后拔掉SOURCE端的HDMI电缆,在待测试HDMI接 口上插入测试夹具(Efficere的HDMI夹具),测试夹具通过探头连接到示波器,即可观察到HDMI端口发送出的信号。

还有一种方法是先在主板上连上SATA硬盘,用U盘从DOS启动,然后拔掉主板上的SATA电缆,插上夹具,连接示波器,即可检测到SATA数据包。

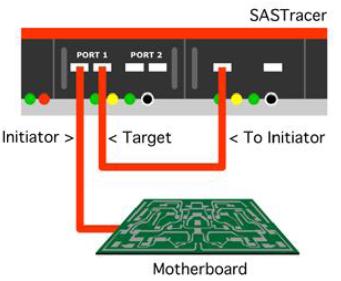

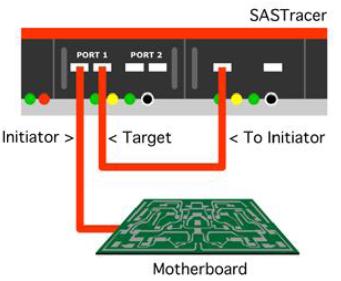

对 于嵌入式系统的SATA接口测试,工程师通常都是跑业务码流的时候用差分探头点测,很少使用SATA测试夹具测试。原因是使用夹具后SATA的HOST和 DEVICE就断开了,待测试SATA芯片通常就停止发包了。对于这种发包困难的SATA芯片测试,可以使用力科SATA协议分析仪,如图5所示为使用力 科SASTracer来配置主板发出测试数据包的示意图。

图5:使用力科SASTracer配置主板的SATA端口发送出测试数据包

引用地址:

串行数据一致性测试系列之二--串行数据测试发包方法的讨论

推荐阅读最新更新时间:2024-03-30 23:07

单片机串行数据采集传输模块的设计

在微机测控系统中,经常要用到A/D转换。常用的方法是扩展一块或多块A/D采集卡。当模拟量较少或是温度、压力等缓变信号场合,采用总线型A/D卡并不是最合适、最经济的方案。这里介绍一种以GNS97C2051单片机为核心,采用TLC2543 12位串行A/D转换器构成的采样模块,该模块的采样数据由单片机串口经电平转换后送到上位机(IBM PC兼容机)的串口COM1或COM2,形成一种串行数据采集串行数据传输的方式。经实践调试证实:该模块功耗低、采样精度高、可靠性好、接口简便,有一定实用价值。 1 主要器件介绍 1.1 TLC2543串行A/D转换器 模块采用TI公司的TLC2543 12位串行A/D转换器,使用开关电容逐次逼近技术

[单片机]

泰克推出自动化HDMI 2.0一致性测试和调试解决方案

新测试解决方案涵盖所有HDMI 2.0 PHY和协议测试,可提供快速、一致和准确的测试结果 2013年11月11日,泰克公司日前宣布,推出针对最新发布的HDMI 2.0规范的全自动一致性测试和调试解决方案。该解决方案涵盖HDMI 2.0发射器测试和基于直接合成技术的接收器测试以及电缆测试要求,可提供快速、一致和准确的测试结果。 作为得到广泛采用的HDMI 1.4a/b标准的后继者,HDMI 2.0规范旨在满足即将出现的超高清 (UHD) 或4K电视的带宽要求,同时使用现有电缆来提供向后兼容性。它使带宽显著增加至18Gbps并增加了许多特性,如32个音频通道和同时向多个用户传送视频和音频流。与先前的HDMI版本一样,

[测试测量]

e2v利用全新ESIstream© 协议简化串行数据传输

领先的高可靠性半导体供应商 e2v 日前发布了全新开放串行化协议的方案。高效串行接口 (ESIstream©) 将极高的数据速率效率和简化的硬件实施结合在一起,用于实现串行数据传输。 数据速率效率对于减少数据传输通道数量至关重要。e2v 的全新 ESIstream© 仅有 12.5% 的开销数据,而其他形式的串行化标准(例如 JESD204b)具有高达 30% 的开销数据。 由于应用范围非常广泛,通用标准变得日益复杂。这导致设计人员必须付出很大努力来了解协议复杂性,进而确定适用于其应用的最佳实施方式。与其他协议相比,ESIstream© 将逻辑门数量减少了至少一半,从而保持了简单性。这样可以缩短设计时间和产品上市时间。

[嵌入式]

RS-485串行数据通信协议

概述 串行数据通信的协议从RS-232到千兆位以太网,虽然每种协议都有特定的应用领域,但任何情况下我们都必须考虑成本和物理层(PHY)性能。本文主要介绍RS-485协议及该协议所适合的应用。同时给出了根据电缆长度、系统设计以及元件选择来优化数据速率的方法。

传输协议

什么是RS-485?Profibus又是什么?与其它串行协议相比,它们的性能如何?适用于哪些应用?为了回答这些问题,我们对RS-485物理层(PHY)、RS-232和RS-422的特性、功能进行了总体比较 (本文中的RS表示ANSIEIA/TIA标准)。RS-232是一个最初用于调制解调器、打印机及其它PC外设

[嵌入式]

CAN一致性测试系统之报文DLC测试

CAN 总线作为应用非常广泛的现场总线,保证 CAN 总线一致性非常重要,DLC作为 CAN 帧的一部分,它的正确与否直接影响到总线通信。那么DLC代表什么?它的功能是什么?如何测试验证其正确性? CAN总线是ISO国际标准化的串行通信协议。在汽车产业中,出于对安全性、舒适性、方便性、低公害、低成本的要求,各种各样的电子控制系统被开发了出来。由于这些系统之间通信所用的数据类型及对可靠性的要求不尽相同,由多条总线构成的情况很多,线束的数量也随之增加。为适应“减少线束的数量”、“通过多个CAN,进行大量数据的高速通信”的需要,CAN总线孕育而生,CAN总线在汽车中的应用图。 随着新能源、智能网联等概念发展,新能源

[汽车电子]

简化高速串行数据调试验证和一致性测试问答

1. 专家你好:请问DPOJET的主要应用领域 DPOJET的主要应用领域是高速串行总线研发、调试和一致性测试,如:PCI_E/DDR/HDMI/DISPLAYPORT/SATA等高速串行总线。 2. 我想问张欣 高级工程师:所谓的高速是指的?结合Tektronix示波器平台DPO/DSA70000,以及DPOJET抖动和眼图分析工具最高采样的速率是多少? 最佳的工作速率段在哪个范围是?谢谢 高速是指被测串行信号的比特率。目前像PCIe2,可以达到5Gbps。DSA70000最高的采样率高达50GS/s,极大的提高对抖动的测量精度。最佳的工作采样率要根据您的具体的测试信号而定。在ppt中有详细讲解。谢谢 3. 请问孙先生,

[测试测量]

串行数据线的一个总结和概述

RS232 是个人计算机上的通讯接口之一,由电子工业协会,EIA) 所制定的异步传输标准接口。通常 RS-232 接口以9个引脚 (DB-9) 或是25个引脚 (DB-25) 的型态出现。(Electronic Industries Association

RS-232-C标准规定的数据传输速率为每秒50、75、100、150、300、600、1200、2400、4800、9600、19200波特。

RS-232-C标准规定,驱动器允许有2500pF的电容负载,通信距离将受此电容限制,例如,采用150pF/m的通信电缆时,最大通信距离为15m;若每米电缆的电容量减小,通信距离可以增加。传输距离短的另一原因是RS-232属单端

[嵌入式]

信号完整性分析基础系列之三--串行数据测试中的CDR

在当今的GHz速率的串行数据测试中,眼图和抖动测试是最重要的两个测试项目。眼图和抖动测量中,测试仪器必须从待测试信号中恢复参考时钟,用该时钟同步和采样数据。因此,恢复时钟的方法会直接影响眼图和抖动测试结果,各种串行数据标准都规定了抖动测量中时钟恢复电路CDR的参数,正确的设置测试仪器的CDR参数才可以使测量结果与芯片接收端的实际性能保持一致。 下图1所示为某串行数据链接的系统图,在Fibre Channel、Gigabit Ethernet、SDH等串行链路中都采用了这样的架构。发送端(TX)发送的信号通过信道传输到接收端(RX)后,收发器芯片RX部分的时钟恢复电路从串行数据中恢复出时钟,用恢复的时钟来同步串行数据,进行采样。

[测试测量]

汽车电线束设计与工艺

汽车电线束设计与工艺 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号