串行数据标准数量不断激增,明显改善了PC、服务器系统的性能。对这些更高速的标准执行测试,找到抖动迹象对设计的长期稳定性及实现优秀的误码率(BER)目标至关重要。要进行高效分析,首先要选择正确的仪器,要很好地了解仪器噪声、上升时间以及三阶谐波、四阶谐波、五阶谐波性能等因素。

但这远不只是进行测量 – 适当的仪器必需与适当的分析工具配套使用。在测试8 Gb/sec以上的串行数据速率时,抖动分隔、反嵌/嵌入等也是重要的考虑因素。在本文中,我们将重点介绍存在串扰时隔离抖动的一种新方法,随着通路数量提高、以提升计算系统吞吐量,串扰问题正变得日益明显。

使用电压跳变表示定时信息的所有电气系统都有定时抖动。在历史上,电气系统通过采用相对较低的信令速率,弱化了定时抖动 (或简称抖动)的负面效应。随着数据速率攀升到8 Gb/sec以上,抖动在信令间隔中的占比明显提高,了解抖动的类型和来源对成功地部署高速串行技术非常关键。

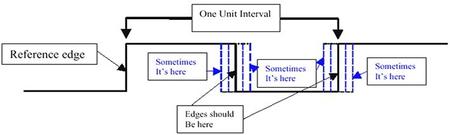

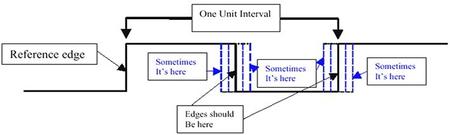

最简单的抖动是边沿距本应位置的偏差,如图1所示。根据ITU定义,抖动是“数字信号有效时点距理想时间位置的短期变化”。

图1: 抖动是边沿距本应位置的偏差。

[图示内容:]

Reference edge: 参考边沿

One Unit Interval: 一个单位间隔

Sometimes It’s here: 有时它在这儿

Edges should Be here: 边沿应该在这儿

可以通过多种方式,测量一个波形上的抖动,包括周期抖动、周期间抖动及时间间隔误差(TIE),设计中经常会指定哪种测量指标比较合适。

在独立振荡器中,信号是时钟,可以跳频或扫频。这里,周期抖动是合适的测量指

标。在发射机的串行数据流中,信号是数据流,ISI (符号间干扰)是关键问题。这里,TIE抖动是合适的测量指标。

徘徊在抖动问题上的工程师有很多仪器可以选择,每种仪器都有独特的优势和劣势:

1)·实时数字存储示波器(DSO)恢复整个波形,可以测量任意项目,可以用于TIE、周期间抖动和周期抖动测量。但它在频率(或位速率)和频谱分辨率、小的抖动和多电平调制方面具有局限性。

2)·BER测试仪(BERT)特别适合测量TIE抖动,尤其是TJ或总抖动,这是TIE的一种形式。BERT的优势是它计数每个比特,但测试执行起来耗时可能会很长。

3)·实时频谱分析仪(RTSA)可以用于移动设备复杂调制的周期间测量和周期测量,用来观察时钟、PLL,了解其动态性能。其局限性包括频宽(低于100 MHz)、带宽信号有大的调制频谱。

4)·等效时间采样示波器提供了最佳的带宽,可以用于串行数据所有抖动测量。目前,这种仪器是唯一拥有噪声分析功能和BER眼图的仪器。其局限性包括:没有实时捕获功能,只能用于重复码型,部分抖动频谱有假信号。

用户经常问的一个问题是如果我们只关心BER,那么为什么还要担心抖动。原因在于如果眼图(宽度)闭合太多,那么会导致误差。抖动和噪声分析工具可以迅速预测和分析BER中的问题。最终,它测试的就是误差,但消除设计中的这些误差要求了解抖动过高的一个或多个原因。

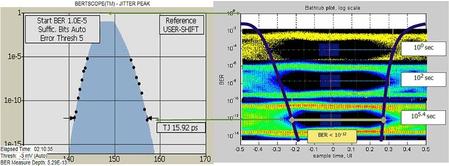

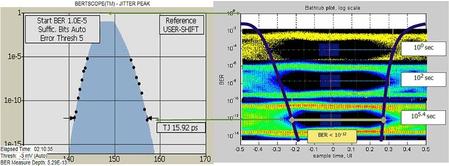

我们首先要从整体BER角度了解系统的性能状况。示波器实现了这一目标,它使用眼图和统计分析创建浴缸曲线,之所以叫浴缸图,是因为在极限变化时,得到的图形形状像浴缸。在使用BERT仪器时,每个位的具体数量会得到一个抖动峰值图。如图2所示,左面来自BERT的抖动峰值与右面示波器抖动浴缸图几乎完全等效。

图2: 左面BERT 抖动峰值与右面示波器抖动浴缸之间的BER性能等效图。

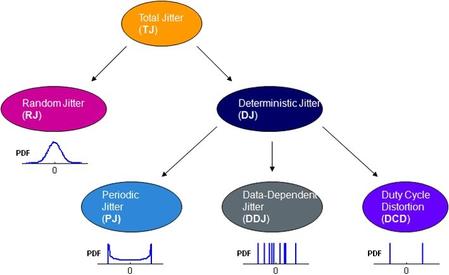

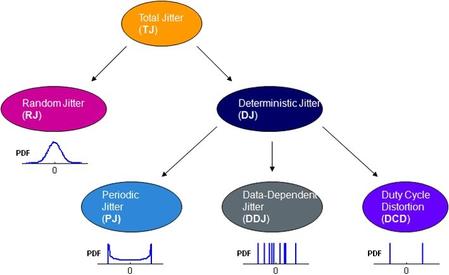

鉴于结果紧密对准,示波器成为BERT非常实用的补充,因为使用BERT测量直到BER=10-12的TJ会需要几个小时的时间,结果并不能揭示哪类问题导致抖动。示波器可以以智能方式测量少量数据,然后把抖动划分成各种抖动成分,其一般采用图3所示的公认的抖动模型。

通过做出假设,示波器可以进行TJ@BER计算,真实反映使用BERT获得的结果,而所用时间只是BERT的几分之一,也就是说,如果所有假设都正确的话。所有复杂系统模型都做出假设和简化,因此模型和实际系统行为之间永远不会完全拟合。正如本文后面讨论的那样,目前,特别麻烦的一个问题是串扰。

图3: 业内抖动模型,2001-2010.

关键字:串扰 抖动 定时分析

引用地址:存在串扰时的抖动和定时分析

但这远不只是进行测量 – 适当的仪器必需与适当的分析工具配套使用。在测试8 Gb/sec以上的串行数据速率时,抖动分隔、反嵌/嵌入等也是重要的考虑因素。在本文中,我们将重点介绍存在串扰时隔离抖动的一种新方法,随着通路数量提高、以提升计算系统吞吐量,串扰问题正变得日益明显。

使用电压跳变表示定时信息的所有电气系统都有定时抖动。在历史上,电气系统通过采用相对较低的信令速率,弱化了定时抖动 (或简称抖动)的负面效应。随着数据速率攀升到8 Gb/sec以上,抖动在信令间隔中的占比明显提高,了解抖动的类型和来源对成功地部署高速串行技术非常关键。

最简单的抖动是边沿距本应位置的偏差,如图1所示。根据ITU定义,抖动是“数字信号有效时点距理想时间位置的短期变化”。

图1: 抖动是边沿距本应位置的偏差。

[图示内容:]

Reference edge: 参考边沿

One Unit Interval: 一个单位间隔

Sometimes It’s here: 有时它在这儿

Edges should Be here: 边沿应该在这儿

可以通过多种方式,测量一个波形上的抖动,包括周期抖动、周期间抖动及时间间隔误差(TIE),设计中经常会指定哪种测量指标比较合适。

在独立振荡器中,信号是时钟,可以跳频或扫频。这里,周期抖动是合适的测量指

标。在发射机的串行数据流中,信号是数据流,ISI (符号间干扰)是关键问题。这里,TIE抖动是合适的测量指标。

徘徊在抖动问题上的工程师有很多仪器可以选择,每种仪器都有独特的优势和劣势:

1)·实时数字存储示波器(DSO)恢复整个波形,可以测量任意项目,可以用于TIE、周期间抖动和周期抖动测量。但它在频率(或位速率)和频谱分辨率、小的抖动和多电平调制方面具有局限性。

2)·BER测试仪(BERT)特别适合测量TIE抖动,尤其是TJ或总抖动,这是TIE的一种形式。BERT的优势是它计数每个比特,但测试执行起来耗时可能会很长。

3)·实时频谱分析仪(RTSA)可以用于移动设备复杂调制的周期间测量和周期测量,用来观察时钟、PLL,了解其动态性能。其局限性包括频宽(低于100 MHz)、带宽信号有大的调制频谱。

4)·等效时间采样示波器提供了最佳的带宽,可以用于串行数据所有抖动测量。目前,这种仪器是唯一拥有噪声分析功能和BER眼图的仪器。其局限性包括:没有实时捕获功能,只能用于重复码型,部分抖动频谱有假信号。

用户经常问的一个问题是如果我们只关心BER,那么为什么还要担心抖动。原因在于如果眼图(宽度)闭合太多,那么会导致误差。抖动和噪声分析工具可以迅速预测和分析BER中的问题。最终,它测试的就是误差,但消除设计中的这些误差要求了解抖动过高的一个或多个原因。

我们首先要从整体BER角度了解系统的性能状况。示波器实现了这一目标,它使用眼图和统计分析创建浴缸曲线,之所以叫浴缸图,是因为在极限变化时,得到的图形形状像浴缸。在使用BERT仪器时,每个位的具体数量会得到一个抖动峰值图。如图2所示,左面来自BERT的抖动峰值与右面示波器抖动浴缸图几乎完全等效。

图2: 左面BERT 抖动峰值与右面示波器抖动浴缸之间的BER性能等效图。

鉴于结果紧密对准,示波器成为BERT非常实用的补充,因为使用BERT测量直到BER=10-12的TJ会需要几个小时的时间,结果并不能揭示哪类问题导致抖动。示波器可以以智能方式测量少量数据,然后把抖动划分成各种抖动成分,其一般采用图3所示的公认的抖动模型。

通过做出假设,示波器可以进行TJ@BER计算,真实反映使用BERT获得的结果,而所用时间只是BERT的几分之一,也就是说,如果所有假设都正确的话。所有复杂系统模型都做出假设和简化,因此模型和实际系统行为之间永远不会完全拟合。正如本文后面讨论的那样,目前,特别麻烦的一个问题是串扰。

图3: 业内抖动模型,2001-2010.

上一篇:基于高吞吐率WLR测试的 ACS集成测试系统

下一篇:TSP-Link—TSP控制基础

推荐阅读最新更新时间:2024-03-30 22:53

基于MIPS处理器和RTAI的数控系统中调度抖动的研究

1 前言 目前,国内外的数控系统大多采用X86体系结构的CPU,主要是因为X86体系结构上拥有丰富的应用软件,开 发环境和技术积累,可以在一定程度上缩短数控系统的开发周期.但X86体系结构也有其自身的缺点,比如其指令集体系结构过于复杂,成本高.而且X86技术一直被国外的几家大公司所垄断,将其应用在数控系统这样的战略资源上,存在一定的安全隐患. M1PS体系结构具有灵活开放,成本低的优点,在工业控制、网络、通信、多媒体娱乐等领域得到了广泛的应用.我国已经研制出了具有自主知识产权的MIPS通用CPU.因此将MIPS结构的CPU应用在数控系统上,不仅可以降低数控系统的成本,还增加了数控系统特别是高档数控系统国产化的水平. 实时操

[单片机]

为什么抖动测试像盲人摸象(上)

抖动测试对于高速信号是非常重要的,抖动测试不光能检查信号的质量,还能预测出BER。但是抖动测试方法业界并没有统一的标准,作为指导的也仅有MJSQ。 由于每种测试都采用了不同的硬件平台和测试方法,所以得出的抖动结果也不一样,有时候甚至大相径庭。一般来说采用了一种仪器来测试抖动的人没有这种困惑,但对于采用了多种仪器来测试抖动的人则不免疑惑 究竟哪种仪器的测试结果是正确的? 本文译自Altera资深工程师Daniel Chow和Agilent抖动测试专家Ransom Stephens合著的《抖动测试方法的相关性和一致性》一文,该文通过两个方面的研究来解释大家所面临的困惑。首先,相关性研究检查了抖动测量的趋势和特性,说明了不同

[测试测量]

CAN总线位定时和同步机制的分析

引言

CAN(Controller Area Network)是有效支持分布式实时控制的串行通讯网络。从位定时的同步方式考虑,它实质上属于异步通讯协议,每传输一帧,以帧起始位开始,而以帧结束及随后的间歇场结束。这就要求收/发双方从帧起始位开始必须保持帧内信息代码中的每一位严格的同步。从位定时编码考虑,它采用的是非归零编码方式,位流传输不像差分码那样可以直接用电平的变化来代表同步信号,因此为保证同步质量,CAN协议定义了自己的位同步方式:硬同步和重同步。

目前相关文献均缺乏对CAN总线位定时与同步机制的详细分析。本文深入分析了CAN总线位周期的结构以及CAN的两种位同步方式 (硬同步和重同步),并明确给出了重同步时重同步跳转

[嵌入式]

关于示波器设置的抖动完美测量

对抖动完美测量的一半工作量都在于如何设置示波器。我们的目标是捕获并显示出信号在系统环境下的真实情况。因为每个实验室都有实时示波器,有必要知道如何去操作它们。抖动测量对环境特别敏感,所以要想办法针对各种抖动优化测试环境。 首先要选取具备合适带宽的设备。如果带宽太窄,测试得边沿速率就会很低。低的沿速率会将幅度噪声更多的转化为时域错误。但是,如果带块太大,也只会增加测试中的热噪声和散粒噪声从而提高噪底。在NRZ码流来讲,一个经验规则就是选取带宽为码率的1.8倍。 接下来,尽量提高采样率,避免发生由于欠采样而发生的混叠效应。理论上,采样速率至少是信号最高基频的两倍;实际上,捕获过程中的模拟信号整形和数据变换会留有余量,

[测试测量]

关于DVD与高速串行总线抖动测量技术

引言 随着计算机和通信系统总线速度的显著提高,特别是各种不同的采用内嵌时钟技术的高速串行总线日益普及,定时抖动已经成为影响其性能的基本因素;而DVD普遍于国内外伴随的品质控制-抖动问题又成为厂商与用户关注的焦点.如何面对关系到系统成败关键的这二个领域的具有共性的抖动测量技术与方法是我们应研讨重点方案。值此将所采的不同的新型和实用之测量技术作分折介绍。 1、作为新标准的DVD抖动测量方法 1.1使用数字时间取样和处理技术(TIA)的方法测量抖动 使用数字处理方法读取抖动值。抖动测量设备, 例如型号LEl875(S1版)和LEl870(抖动测量设备)使用数字处理方法(即使用和TIA相同的处理方法)以读取抖动

[测试测量]

Crystek Crystals的VCSO具有低噪声低抖动特性

Crystek Crystals公司近日推出一款1GHz的声表面压控振荡器(VCSO)CVCSO-914-1000。该器件具有低噪声、低抖动和理想正弦波形输出等特性,适用于PLL频率转换、航空、电信及测量测试等多种应用。 CVCSO-914-1000采用FR5 PC板和SAW晶体技术设计而成,10KHz偏移下相位噪声为-135dBc/Hz。该芯片采用9×14mm表面贴装封装形式,5V电源供电,可在7dBm最小输出功率下产生理想的正弦波,APR稳定性达±50ppm,无次谐波,二次谐波仅-20dBc。 CVCSO-914-1000的工作温度范围在-20℃至70℃之间,量购单价为125美元(仅供参考)。

[新品]

高性能缓冲器系列 实现更最低抖动【赛普拉斯】

2011年3月8日,北京讯,赛普拉斯半导体公司日前宣布推出一款新型时钟缓冲器系列产品,该系列具有业界最低的额外RMS相位抖动。CY2Dx15xx系列的额外RMS相位抖动可低至60fs,同时还能实现低至480ps的传播延迟。 新的缓冲器可以产生多个相同的时钟,通常可用于系统中的几个接口和IC,例如处理器和FPGA。他们可以产生最多10个差分输出,格式包括LVPECL, LVDS 和 CML。这些新款缓冲器具有多种封装方式,包括8-pin SOIC、8-pin TSSOP、20-pin TSSOP以及32-pin TQFP。 这一低抖动、低偏移、高性能缓冲器完善了赛普拉斯的FleXO™系列低抖动时钟发生器产品线。高性能

[嵌入式]

直流电机制动是电机抖动的原因吗

直流电机制动是导致电机抖动的一个可能原因,但并不是唯一的原因。 1. 引言 直流电机在许多应用中被广泛使用,如工业生产线、交通工具等。然而,在电机制动过程中,会出现抖动问题,这影响了电机的运行效果和使用寿命。本文将详细探讨直流电机制动抖动的原因,并提出一些建议来减轻抖动问题。 2. 直流电机制动过程 直流电机的制动一般是通过改变电机的输入电压或电流来实现的。在制动开始时,电机的输入电压或电流突然减少,导致电机停转力矩急剧下降。这时,电机的旋转惯性会使其继续旋转,直至停转。然而,由于制动力矩的突然减小,电机会产生反向的旋转力矩,即制动力矩与电机的旋转惯性之间的失衡。 3. 直流电机制动抖动的原因 3.1 制动力矩和电机惯性失衡 由于

[嵌入式]

数字电路答疑解惑与典型题解_北京邮电大学 (吴蕾、杨平乐、王诗兵、吴婷)

数字电路答疑解惑与典型题解_北京邮电大学 (吴蕾、杨平乐、王诗兵、吴婷) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号