随着ASIC电路结构和功能的日趋复杂,与其相关的测试问题也日益突出。在芯片测试方法和测试向量生成的研究过程中,如何降低芯片的测试成本已经成为非常重要的问题。DFT(可测性设计)通过在芯片原始设计中插入各种用于提高芯片可测性的逻辑,从而使芯片变得容易测试,大大降低了芯片的测试成本。目前比较成熟的可测性设计主要有扫描设计、边界扫描设计、BIST(Built In Self Test,内建自测试)等。本文通过对一种控制芯片的测试,证明通过采用插入扫描链和自动测试向量生成(ATPG)技术,可有效地简化电路的测试,提高芯片的测试覆盖率,大大减少测试向量的数量,缩短测试时间,从而有效地降低芯片的测试成本。

基于扫描的DFT方法扫描设计的基本原理

时序电路中时序元件的输出不仅由输入信号决定,还与其原始状态有关,因此,对它的故障检测比组合电路要困难的多。扫描设计就是将时序电路转化为组合电路,然后使用已经很成熟的组合电路测试生成系统,来完成测试设计。

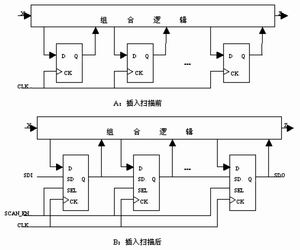

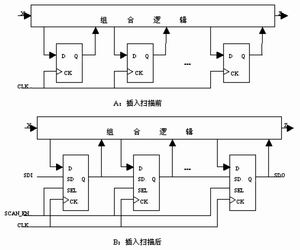

扫描设计可将电路中的时序元件替换为相应的可扫描的时序元件(也叫扫描触发器),然后把它们串起来,形成一个从输入到输出的测试串行移位寄存器(即扫描链),以实现对时序元件和组合逻辑的测试。

如图1所示,采用扫描设计技术后,通过扫描输入端,可以把需要的数据串行地移位到扫描链的相应单元中,以串行地控制各个单元;同时,也可以通过扫描输出端串行地观测它们。这样就消除了时序电路的不可控制性和不可观测性,提高了电路的可测性。需要注意的是,可测性设计的前提是不能改变原始设计的功能。

扫描设计的基本流程

扫描设计测试的实现过程是:

1) 读入电路网表文件,并实施设计规则检查(DRC),确保设计符合扫描测试的设计规则;

2) 将电路中原有的触发器或者锁存器置换为特定类型的扫描触发器或者锁存器(如多路选择D触发器),并且将这些扫描单元链接成一个或多个扫描链,这一过程称之为测试综合;

3) 测试向量自动生成(ATPG)工具根据插入的扫描电路以及形成的扫描链自动产生测试向量;

4) 故障仿真器(Fault Simulator)对这些测试向量实施评估,并确定故障覆盖率情况。

DFT对芯片的影响

DFT是为了简化芯片测试而采用的技术,对芯片的功能没有影响,但不可避免地会增加逻辑,对芯片产生一些影响。

对芯片面积的影响

DFT以增加逻辑来达到简化测试的目的,增加的逻辑势必会增加芯片面积。一般,采用DFT会增加10%"15%的芯片面积。

对芯片性能的影响

边界扫描要在每个输入输出端口处插入边界扫描寄存器(BSC),因此,在正常工作时,信号要多通过一个多路开关,这就带来了额外延时,降低了芯片原本可以达到的工作频率。

对芯片故障覆盖率的影响

芯片测试的要求就是要尽可能地将有故障的芯片检测出来,从而降低芯片的逃逸率(Escape)。DFT的目的在于方便测试,提高故障覆盖率,从而降低逃逸率。故障覆盖率并非越高越好,因为提高故障覆盖率可能会大大增加测试成本,所以应该在测试成本与取得的逃逸率之间进行折衷。[page]

对芯片上市时间的影响

产品的上市时间对于企业至关重要,与芯片测试相关的影响上市时间的因素有:测试电路的设计时间、测试准备(ATPG,Test仿真)及工艺测试时间。

在上述因素中,测试电路设计时间的增加无疑会延迟芯片的上市时间,但DFT设计软件的不断完善能够缩短该设计时间。测试准备包括测试向量的编写和仿真,一个高效的测试向量集可以大大缩短工艺测试时间。若不采用DFT技术,就要付出相当长的时间来编写测试向量集,而且,随着VLSI的快速发展,由人工提供测试向量将越来越不现实。如果采用DFT技术,就可以缩短测试准备和工艺测试时间。因此,从总体上看,DFT是可以缩短芯片上市时间的。

两种测试方法的比较

本文针对某一种控制芯片,对采用DFT和不采用DFT的两种测试方法进行了比较,以说明DFT技术对芯片故障覆盖率及测试向量集的影响。对芯片进行“结构测试”时的测试激励来源有两种:一种是直接根据芯片的功能测试激励得到芯片的生产测试向量;另一种就是采用DFT技术,通过对设计插入扫描链,采用ATPG的方法得到测试向量。

不采用DFT技术的芯片测试测试工具与测试流程

Cadence公司的Verifault_XL工具可以统计一个测试向量集能测出多少故障,从而给出该测试向量集的故障覆盖率。采用该工具的测试流程为:

1) 用芯片功能测试激励中的部分激励对芯片的RTL级代码进行代码覆盖率的测试;

2) 在激励中调用Verifault的系统任务,实现故障的管理、注入等工作;

3) 使用Verilog_XL运行本组测试激励,得到Verifault统计结果;

4) 根据统计结果报告的故障覆盖率调整测试激励,直至达到满足要求的故障覆盖率;

5) 对达到要求的测试激励进行测试向量的提取。

需要注意的是流程中第3步,由于受机器内存的限制,Verifault能复制的设计数量有限,为了验证所有的prime故障,Verifault会重复进行多遍测试(pass),这是对Verifault仿真时间影响最大的因素。每测试完一遍,Verifault会报告一次统计结果。

测试结果

本文经过对测试激励的不断调整,最终可达到的最高故障覆盖率为81.3%,在时钟的下降沿提取测试向量,得到了超过88万个的测试向量,其位数为54b。

采用DFT技术的芯片测试测试工具与测试流程

因为该芯片逻辑是全同步设计,所以采用ATPG+扫描链的DFT技术可以得到高效的测试向量集和较高的故障覆盖率。Synopsys公司的DC和TetraMAX工具是完成该可测性设计的最佳选择。

DC用来完成扫描链的插入,同时生成TetraMAX需要的约束文件(.spf文件)和插入扫描链后的网表文件。TetraMAX是用来实现ATPG的工具,需要与DC配合使用。 采用这些工具的测试流程为:

1) 首先把不符合可测性设计要求的逻辑模块从逻辑内核中分离出来,保证逻辑内核的时钟可以直接使用管脚输入的时钟,而非门生时钟;

2) 增加test_en端口,以及一些必要的逻辑门;

3) 在综合后的网表基础上插入扫描链;

4) 使用TetraMAX做ATPG,生成测试向量;

5) 用得到的测试向量测试逻辑内核;

在最后一步中,由于TetraMAX生成测试激励的时候,扫描链的数据是并行加载的,与实际情况不同,所以需要重新编写测试激励对得到的测试向量的可靠性进行测试。

测试结果

TetraMAX生成的测试向量共有324个,其位数为359b。测试覆盖率达到92.86%。扫描器件的使用以及与DFT相关的附加逻辑的加入,导致了芯片面积的增长,据输出报告可知,采用DFT技术后,芯片面积增加了大约13%。

结语

通过两种测试方法的对比,可以看到,不采用DFT技术,不必增加逻辑,但仅使用功能验证时的测试激励可能无法达到要求的故障覆盖率,而且测试深度(生产测试用向量)也容易超过测试机的存储量。本文对该控制芯片进行测试时,如果不采用DFT技术,虽然测试覆盖率可以达到80%以上,但测试向量却高达80多万,若以人工的方法修改测试向量,将大大延长芯片开发周期,推迟芯片上市时间。采用DFT技术虽然增加了芯片面积,但可以自动生成高效简洁的测试向量,且故障覆盖率能达到90%以上,极大地提高了芯片的测试效率,降低了测试成本。

关键字:DFT 扫描 芯片测试

引用地址:基于扫描的DFT对芯片测试的影响

基于扫描的DFT方法扫描设计的基本原理

时序电路中时序元件的输出不仅由输入信号决定,还与其原始状态有关,因此,对它的故障检测比组合电路要困难的多。扫描设计就是将时序电路转化为组合电路,然后使用已经很成熟的组合电路测试生成系统,来完成测试设计。

扫描设计可将电路中的时序元件替换为相应的可扫描的时序元件(也叫扫描触发器),然后把它们串起来,形成一个从输入到输出的测试串行移位寄存器(即扫描链),以实现对时序元件和组合逻辑的测试。

如图1所示,采用扫描设计技术后,通过扫描输入端,可以把需要的数据串行地移位到扫描链的相应单元中,以串行地控制各个单元;同时,也可以通过扫描输出端串行地观测它们。这样就消除了时序电路的不可控制性和不可观测性,提高了电路的可测性。需要注意的是,可测性设计的前提是不能改变原始设计的功能。

扫描设计的基本流程

扫描设计测试的实现过程是:

1) 读入电路网表文件,并实施设计规则检查(DRC),确保设计符合扫描测试的设计规则;

2) 将电路中原有的触发器或者锁存器置换为特定类型的扫描触发器或者锁存器(如多路选择D触发器),并且将这些扫描单元链接成一个或多个扫描链,这一过程称之为测试综合;

3) 测试向量自动生成(ATPG)工具根据插入的扫描电路以及形成的扫描链自动产生测试向量;

4) 故障仿真器(Fault Simulator)对这些测试向量实施评估,并确定故障覆盖率情况。

DFT对芯片的影响

DFT是为了简化芯片测试而采用的技术,对芯片的功能没有影响,但不可避免地会增加逻辑,对芯片产生一些影响。

对芯片面积的影响

DFT以增加逻辑来达到简化测试的目的,增加的逻辑势必会增加芯片面积。一般,采用DFT会增加10%"15%的芯片面积。

对芯片性能的影响

边界扫描要在每个输入输出端口处插入边界扫描寄存器(BSC),因此,在正常工作时,信号要多通过一个多路开关,这就带来了额外延时,降低了芯片原本可以达到的工作频率。

对芯片故障覆盖率的影响

芯片测试的要求就是要尽可能地将有故障的芯片检测出来,从而降低芯片的逃逸率(Escape)。DFT的目的在于方便测试,提高故障覆盖率,从而降低逃逸率。故障覆盖率并非越高越好,因为提高故障覆盖率可能会大大增加测试成本,所以应该在测试成本与取得的逃逸率之间进行折衷。[page]

对芯片上市时间的影响

产品的上市时间对于企业至关重要,与芯片测试相关的影响上市时间的因素有:测试电路的设计时间、测试准备(ATPG,Test仿真)及工艺测试时间。

在上述因素中,测试电路设计时间的增加无疑会延迟芯片的上市时间,但DFT设计软件的不断完善能够缩短该设计时间。测试准备包括测试向量的编写和仿真,一个高效的测试向量集可以大大缩短工艺测试时间。若不采用DFT技术,就要付出相当长的时间来编写测试向量集,而且,随着VLSI的快速发展,由人工提供测试向量将越来越不现实。如果采用DFT技术,就可以缩短测试准备和工艺测试时间。因此,从总体上看,DFT是可以缩短芯片上市时间的。

两种测试方法的比较

本文针对某一种控制芯片,对采用DFT和不采用DFT的两种测试方法进行了比较,以说明DFT技术对芯片故障覆盖率及测试向量集的影响。对芯片进行“结构测试”时的测试激励来源有两种:一种是直接根据芯片的功能测试激励得到芯片的生产测试向量;另一种就是采用DFT技术,通过对设计插入扫描链,采用ATPG的方法得到测试向量。

不采用DFT技术的芯片测试测试工具与测试流程

Cadence公司的Verifault_XL工具可以统计一个测试向量集能测出多少故障,从而给出该测试向量集的故障覆盖率。采用该工具的测试流程为:

1) 用芯片功能测试激励中的部分激励对芯片的RTL级代码进行代码覆盖率的测试;

2) 在激励中调用Verifault的系统任务,实现故障的管理、注入等工作;

3) 使用Verilog_XL运行本组测试激励,得到Verifault统计结果;

4) 根据统计结果报告的故障覆盖率调整测试激励,直至达到满足要求的故障覆盖率;

5) 对达到要求的测试激励进行测试向量的提取。

需要注意的是流程中第3步,由于受机器内存的限制,Verifault能复制的设计数量有限,为了验证所有的prime故障,Verifault会重复进行多遍测试(pass),这是对Verifault仿真时间影响最大的因素。每测试完一遍,Verifault会报告一次统计结果。

测试结果

本文经过对测试激励的不断调整,最终可达到的最高故障覆盖率为81.3%,在时钟的下降沿提取测试向量,得到了超过88万个的测试向量,其位数为54b。

采用DFT技术的芯片测试测试工具与测试流程

因为该芯片逻辑是全同步设计,所以采用ATPG+扫描链的DFT技术可以得到高效的测试向量集和较高的故障覆盖率。Synopsys公司的DC和TetraMAX工具是完成该可测性设计的最佳选择。

DC用来完成扫描链的插入,同时生成TetraMAX需要的约束文件(.spf文件)和插入扫描链后的网表文件。TetraMAX是用来实现ATPG的工具,需要与DC配合使用。 采用这些工具的测试流程为:

1) 首先把不符合可测性设计要求的逻辑模块从逻辑内核中分离出来,保证逻辑内核的时钟可以直接使用管脚输入的时钟,而非门生时钟;

2) 增加test_en端口,以及一些必要的逻辑门;

3) 在综合后的网表基础上插入扫描链;

4) 使用TetraMAX做ATPG,生成测试向量;

5) 用得到的测试向量测试逻辑内核;

在最后一步中,由于TetraMAX生成测试激励的时候,扫描链的数据是并行加载的,与实际情况不同,所以需要重新编写测试激励对得到的测试向量的可靠性进行测试。

测试结果

TetraMAX生成的测试向量共有324个,其位数为359b。测试覆盖率达到92.86%。扫描器件的使用以及与DFT相关的附加逻辑的加入,导致了芯片面积的增长,据输出报告可知,采用DFT技术后,芯片面积增加了大约13%。

结语

通过两种测试方法的对比,可以看到,不采用DFT技术,不必增加逻辑,但仅使用功能验证时的测试激励可能无法达到要求的故障覆盖率,而且测试深度(生产测试用向量)也容易超过测试机的存储量。本文对该控制芯片进行测试时,如果不采用DFT技术,虽然测试覆盖率可以达到80%以上,但测试向量却高达80多万,若以人工的方法修改测试向量,将大大延长芯片开发周期,推迟芯片上市时间。采用DFT技术虽然增加了芯片面积,但可以自动生成高效简洁的测试向量,且故障覆盖率能达到90%以上,极大地提高了芯片的测试效率,降低了测试成本。

上一篇:MAX1464的片上温度传感器

下一篇:电子产品辐射发射的抑制

推荐阅读最新更新时间:2024-03-30 22:54

特斯拉新软件更新 车辆可扫描崎岖不平的道路并避让

据外媒报道,特斯拉在新的软件更新中证实,其车辆现在可扫描崎岖不平的道路,如坑洼,并通过调整悬架避让以避免车辆损坏。 图片来源:FredericLambert 为了实现全自动驾驶,系统必须能够处理不同的场景,包括各种天气和路况。但对于人类驾驶员而言都很难处理的坑洼等路况,自动驾驶系统可能更无法正确导航。特斯拉正在利用其配备Autopilot硬件的大型客户车队来捕获有关这些极端案例的数据,并教学神经网络进行处理。 特斯拉在新的2022.20软件更新发行说明中写道,“特斯拉自适应悬架(Tesla Adaptive Suspension)”系统添加了一项新功能: 特斯拉自适应悬架将为前方崎岖路段调整行驶高度。随着车辆

[汽车电子]

封装测试等,近6亿元光库科技芯片产业园项目于珠海开工

12月10日,光库科技芯片产业园项目于广东省珠海市高新区开工奠基。 光库科技铌酸锂高速调制器芯片研发及产业化项目投资总额5.85亿元,其中募集资金投入5.4亿元。项目占地约26亩,总建筑面积约4万平方米,预计2022年投产,将年产10万片铌酸锂芯片及高速调制器。 据介绍,项目主要包括芯片生产中心,封装测试中心和研发中心,落成后用以电信级铌酸锂系列高速光调制器芯片及器件的研发和产业化,并研发下一代薄膜铌酸锂调制器。 光库科技成立于2000年,于2019年成功收购Lumentum公司在意大利米兰的铌酸锂调制器产品线资产后,又于今年10月成立了光子集成事业部。 光库科技消息显示,随着芯片产业园项目的落成,光库科技将填补国内高

[手机便携]

1200万像素SmartScan R12蓝光扫描系统全新上市

海克斯康SmartScan系列蓝光扫描系统拥有微结构光栅投影技术,能够为扫描任务提供更高的精度和更好的细节呈现。SmartScan扫描系统,也因其多功能性和便携性而备受市场赞誉。 如今蓝光扫描技术再添新品——AICON SmartScan R12,它将提供1200万像素高分辨率相机系统,再次拓展了海克斯康制造智能蓝光扫描系统的产品涵盖范围,从几毫米到几米的测量范围内,分辨率和准确性都得到了极大地提高。 1200万像素,更多应用覆盖面 海克斯康SmartScan R12蓝光扫描系统扫描速度快、精度高,模块化的系统可以提供小到喷嘴大到整车的扫描测量的个性化的定制方案。 海克斯康AICON扫描系统产品经理Di

[工业控制]

Chroma 13001组件测试扫描仪的特点及应用

近几年来由于组件变得更加复杂与多通道等复合性问题,使测试困难与结构变得复杂,增加人为错误可能性与人力成本。Chroma 13001提供多信道扫描功能,搭配 Chroma 3302 / 3252 / 11022 / 11025 LCR 表做电感值、电容值、电阻值等量测,并包含圈数比 (turn ratio) 量测 (如果LCR表有提供此功能),也可以与 Chroma 11200 电容漏电流/绝缘电阻表配合绝缘电阻测试,并有专为漏感量测的短路设计。单台可以支持8插槽模块,当搭配8个选配 A113007 的 40 Channels 扫描模块,单台可多达320通道。并提供主/从设计,Chroma/致茂台湾13001组件测试扫描仪客户可经由

[测试测量]

全球首款采用7纳米工艺的CCIX测试芯片即将问世

赛灵思、Arm、Cadence和台积公司今日宣布一项合作,将共同构建首款基于台积7纳米FinFET工艺的支持芯片间缓存一致性(CCIX)的加速器测试芯片,并计划在2018年交付。这一测试芯片旨在从硅芯片层面证明CCIX能够支持多核高性能Arm CPU和FPGA加速器实现一致性互联。 关于CCIX 出于功耗及空间方面的考虑,在数据中心内对应用进行加速的需求日益增长,诸如大数据分析、搜索、机器学习、4G/5G无线、内存内数据处理、视频分析及网络处理等应用,都已受益于可在多个系统部件中无缝移动数据的加速器引擎。CCIX将支持部件在无需复杂编程环境的情况下,获取并处理位于任何地方的数据。 CCIX将利用现有的服务器互连基础架构,实现对

[嵌入式]

英国利用磁共振成像扫描法观察钠 研发下一代高性能钠电池

据外媒报道,英国伯明翰大学(the University of Birmingham)一项研究表明,磁共振成像(MRI)技术可有效支持下一代高性能可充电电池的研发。 (图片来源:伯明翰大学) 该项技术本是为探测钠电池中金属钠离子的移动和沉积情况而研发,也可用于加快新型电池材料评估速度,并有助于加快钠电池的上市。 人们普遍认为,钠电池有望取代锂离子电池,而目前锂离子电池广泛应用于便携式电子产品和 电动汽车 等设备。生产锂离子电池所需的材料是非常关键的战略性元素,因此,研究人员正努力研发替代性材料以及更加可持续性的技术。 尽管钠似乎具有生产高效电池的许多特性,但是在优化其性能方面仍存在挑战。其中的关键挑战就是了解钠在

[汽车电子]

全新屏下指纹技术:整块屏幕都能扫描

近日,三星的一项有关于屏下指纹的专利已经可以通过美国专利商标局显示了出来。这次的屏下指纹识别非常先进,它能够使得手机的整块屏幕都变成指纹扫描仪,这也就意味着用户可以用手指触摸屏幕的任何地方都能够进行指纹扫描。 对于屏下指纹技术,相信现在很多人都已经非常了解了,现在很多安卓旗舰机都已经搭载了屏下指纹技术。然而在安卓手机中有着非常大影响的三星却迟迟没有搭载这项先进的技术。之所以这样就是因为三星在自己研究这项技术。 现有的屏下指纹手机的扫描位置仅仅只是在一个固定的区域,而三星这次所研究的技术将会在整个屏幕的任意位置都可以进行指纹扫描解锁,而且其速度要比现在的超声波解锁更快、更稳定,所以我们就一

[手机便携]

数码管显示驱动和键盘扫描控制器CH451及其应用

摘要:介绍一种新型的键盘显示驱动芯片CH451的性能特点和工作原理,给出了CH451键盘显示驱动芯片与MCS-51单片机的接口方法与相应的软件驱动程序。

关键词:键盘显示控制;单片机;CH451

单片机在开发过程中,常常会因为资源不足而不得不大量扩展接口芯片以满足应用系统的需要,其中原因之一是人机界面中的键盘显示占用了系统太多资源,从而造成系统庞大,同时降低了系统的可靠性。在单片机应用系统中,键盘显示通常可采用以下几种方式:

(1)采用并行接口的键盘显示专用芯片8279。但8279所需外围元件多(显示驱动、译码等)、占用电路板面积大、综合成本高,在中小系统中常常大材小用;

(2)采用通用并行I/O芯片扩展(如用8155等

[单片机]

全相位数字信号处理方法及MATLAB实现

全相位数字信号处理方法及MATLAB实现 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号